## Feature Model-based Software Product Line Testing

VOM FACHBEREICH 18

ELEKTRO- UND INFORMATIONSTECHNIK

ZUR ERLANGUNG DER WÜRDE

EINES DOKTOR-INGENIEURS (DR.-ING.)

GENEHMIGTE DISSERTATION

VON

DIPL.-INFORM. SEBASTIAN OSTER

GEBOREN AM

22. NOVEMBER 1981 IN HAMBURG

REFERENT: PROF. DR. RER. NAT. A. SCHÜRR KORREFERENT: PROF. DR. RER. NAT. U. GOLTZ

TAG DER EINREICHUNG: 23. AUG. 2011

TAG DER MÜNDLICHEN PRÜFUNG: 16. DEZ. 2011

HOCHSCHULKENNZIFFER D17

DARMSTADT 2012

## Dedication

For the ones I love the most. Oya, Mikael, Alisha, Barbara, and Wolfgang. Your love is inspiring and motivating.

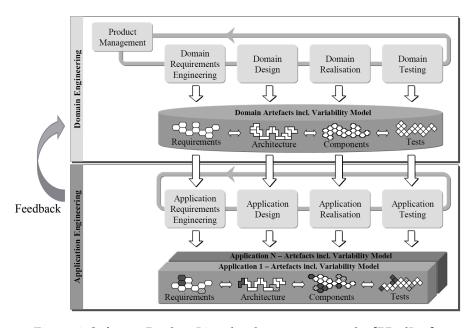

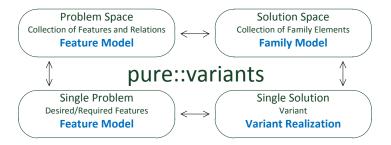

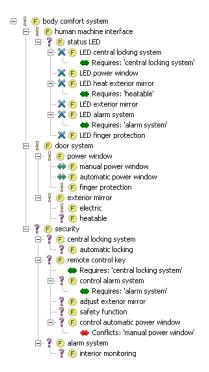

Software Product Line (SPL) engineering is a popular approach for the systematic reuse of software artifacts across a very large number of similar products. SPLs are gaining widespread acceptance and various domains already apply SPL engineering successfully to address the well-known needs of the Software Engineering community, such as increasing quality, saving costs for development and maintenance, and decreasing time-to-market. The central aspect of systematic reuse is the concept of variability often leading to an enormous number of possible products

In the automotive sector, we are increasingly encountering a situation where a single electronic control unit (ECU) may be instantiated in at least 10,000 different ways, and the software running on a network of more than 50 ECUs in a single car may exist in millions of different configurations. As a result, we are confronted with a world where any instance of a certain brand of car possesses a unique configuration of the embedded software of all its ECUs. At a first glance, SPL engineering seems to result in a major benefit for the automotive sector as well as for other industrial domains, allowing the combination of mass production and product customization. The reverse side of the coin is the challenge to assure the quality of each derivable product of the SPL e.g. via testing activities.

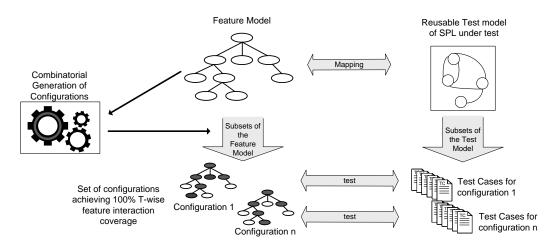

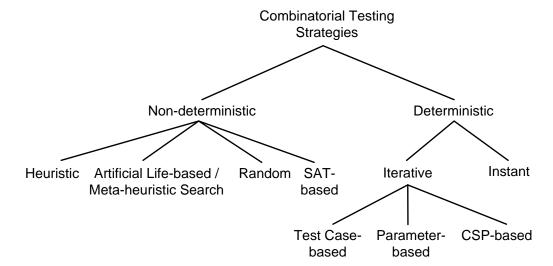

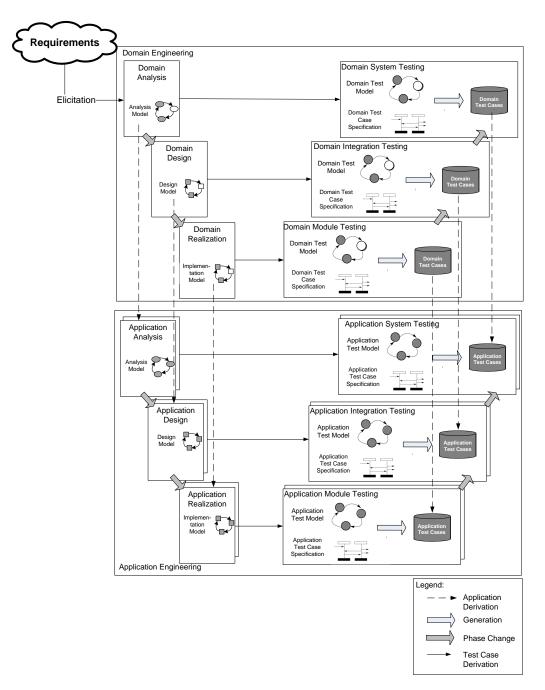

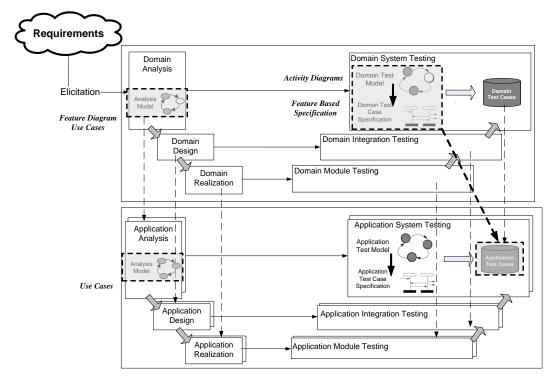

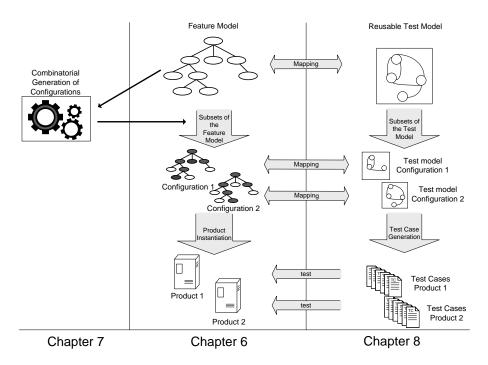

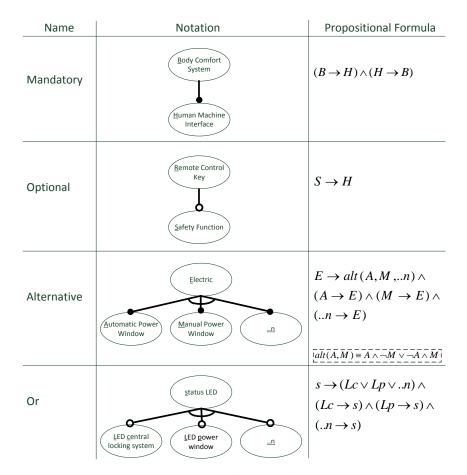

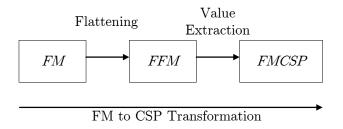

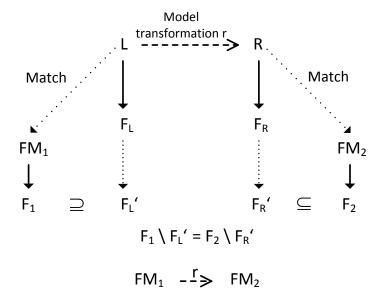

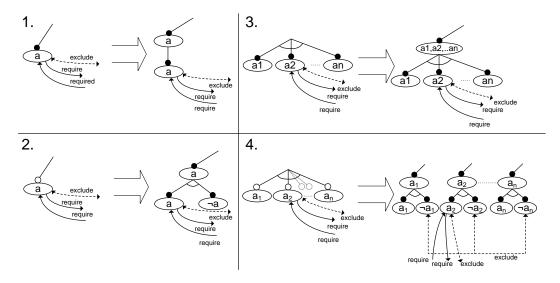

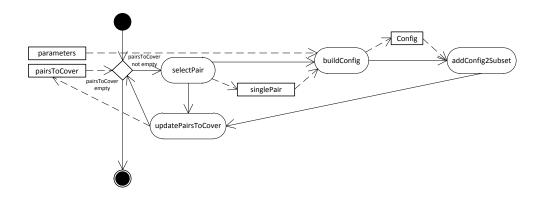

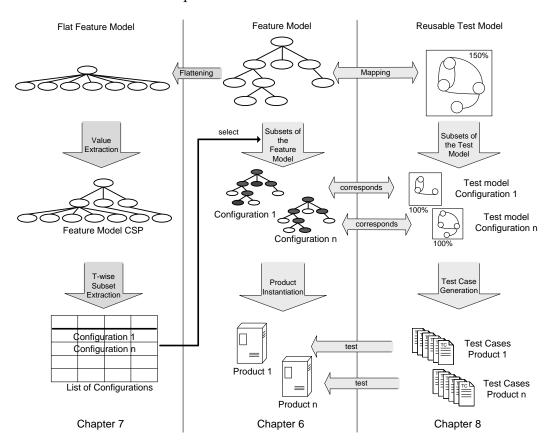

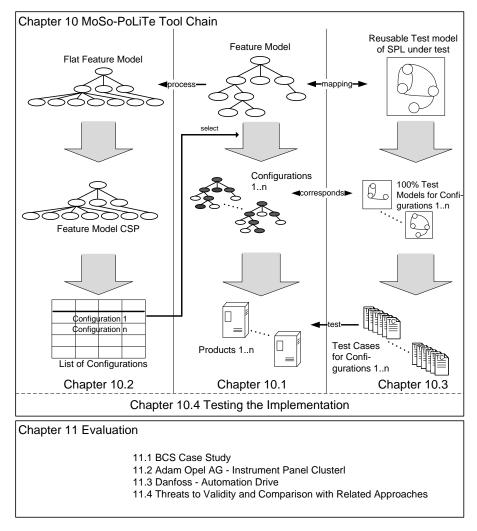

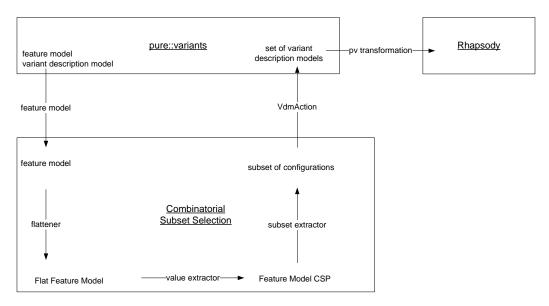

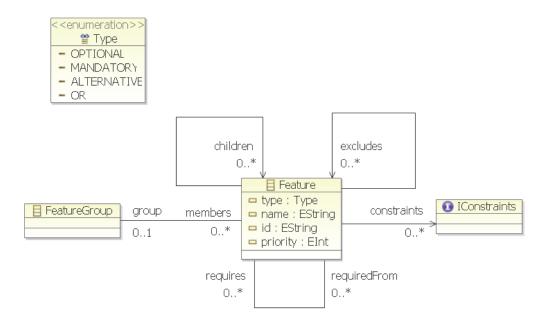

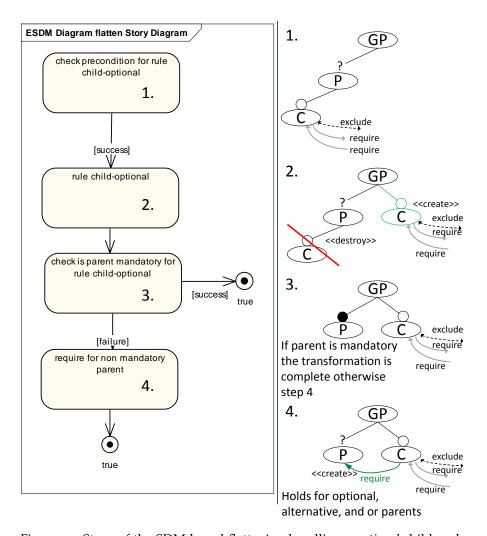

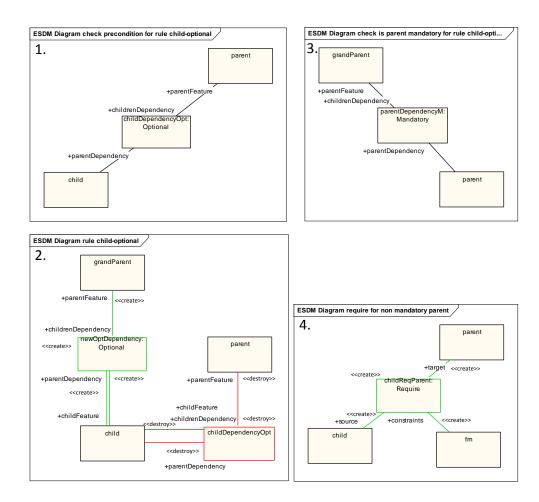

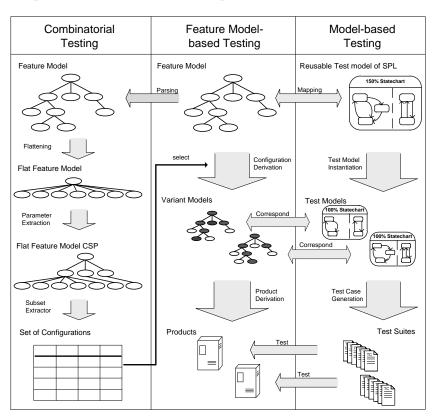

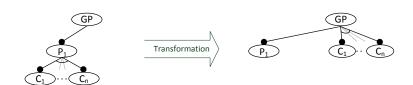

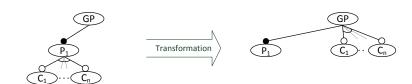

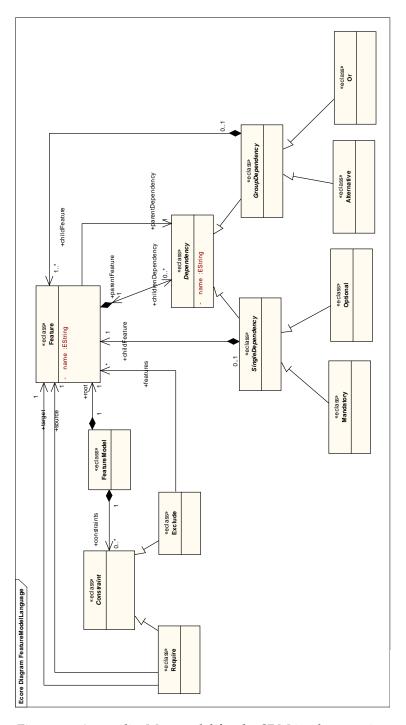

Testing all products of an SPL individually is generally not feasible. This thesis contributes an approach to significantly reduce the test effort for SPL testing. Faults are likely to be revealed at execution points where features exchange information with other features or influence one another. Therefore, a criterion for test adequacy is to cover as many interactions among different features as possible, thus, increasing the probability of finding bugs based on feature interaction. We present a novel approach to generate a representative set of products of the SPL required for comprehensive coverage of feature interactions. The features of the feature model are combined in products using a combinatorial strategy assuring a certain degree of feature interaction coverage. For this purpose we introduce a graph transformation-based algorithm to translate the feature model into a binary constraint satisfaction problem and also an algorithm combining constraint solving techniques with a feature combination strategy to generate the representative set of products. A mapping between the feature model and a reusable test model allows for generating test cases for each product automatically. We implemented our approach as a tool chain and applied it to three different industrial SPLs for evaluation purposes. The results suggest that with our approach higher coverage of feature interactions is achieved at a fraction of cost and time when compared with the state-of-the-art approach of testing all derivable products.

Software-Produktlinien (SPL)-Engineering ist ein populärer Ansatz für die systematische Wiederverwendung von Software-Artefakten über eine große Menge von sich ähnelnden Produkten. Die industrielle Verwendung von SPLs steigt zunehmend. Eine Vielzahl von verschiedenen Domänen setzen bereits erfolgreich auf SPL Engineering mit der Zielsetzung, die bekannten Software-Engineering-Anforderungen, wie steigende Qualitätsansprüche, Kostenreduzierung für Entwicklung und Wartung und der Verkürzung der Time-to-Market, zu erfüllen. Zentraler Bestandteil der systematischen Wiederverwendung ist das Konzept der Variabilität, welches häufig zu einer enorm hohen Anzahl von möglichen Produkten führt.

Im Automobilbereich werden die Entwickler zunehmend mit der Situation konfrontiert, in der ein elektronisches Steuergerät (ECU) bis zu 10.000 verschiedene Konfigurationsmöglichkeiten besitzt. Bei durchschnittlich mehr als 50 ECUs in einem Auto ergeben sich Millionen von möglichen Konfigurationen. Folglich hat bereits jedes Auto bei bestimmten Modellen einiger Automobilhersteller einen individuellen Softwarestand. Auf den ersten Blick scheint das SPL-Engineering einen immensen Vorteil für den Automobilbereich und viele andere Industriezweige zu bringen, da dieser Ansatz die Kombination von Massenproduktion und Produkt-Customizing bietet. Die Kehrseite der Medaille ist die Herausforderung, die Qualität jedes einzelnen Produktes sicherzustellen, z.B. durch Tests.

Das individuelle Testen aller Produkte ist in der Regel nicht möglich. Diese Arbeit stellt einen Ansatz zur signifikanten Reduktion des Testaufwands für SPLs vor. Fehler treten erwartungsgemäß dort auf, wo Features Informationen/Daten austauschen oder sich beeinflussen. Die Abdeckung solcher Interaktionen erscheint als geeignetes Kriterium für adäquates Testen, um möglichst viele interaktionsbasierte Fehler zu finden. In dieser Arbeit wird eine Methodik zu Generierung einer repräsentativen Menge von Produkten vorgestellt. Die Features des Featuremodells werden gemäß einer kombinatorischen Test Strategie zu Produkten kombiniert, um einen gewissen Grad an Feature-Interaktionen abzudecken. Dazu wird das Featuremodell durch Graphtransformation in ein binäres Constraint Satisfaction Problem übersetzt, welches dann durch eine Kombination von Constraint Solver und kombinatorischem Testen gelöst wird, um die repräsentative Menge von Produkten zu generieren. Ein Mapping zwischen den Features und einem wiederverwendbaren Testmodell erlaubt die automatische Generierung von produktspezifischen Testfällen für jedes Produkt der SPL. Der gesamte Ansatz wird als Werkzeugkette implementiert und anhand von drei verschiedenen industriellen SPLs evaluiert. Die Ergebnisse zeigen, dass mit diesem Ansatz eine höhere Abdeckung von Fehlern durch das Abdecken von Feature Interaktionen erreicht werden kann. Gleichzeitig werden Kosten und Zeit im Vergleich zum standardmäßigen SPL-Testverfahren, dem Testen einzelner Produkte, reduziert.

Some ideas and figures within this thesis have appeared previously in the following publications. A complete list of my publications is available online under http://www.es.tu-darmstadt.de/mitarbeiter/sebastian-oster.

#### **Book Chapters:**

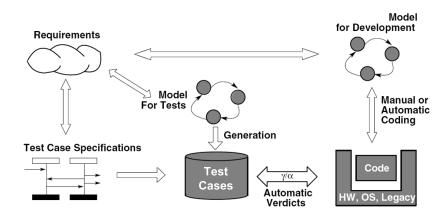

• S. Oster, A. Wübbeke, G. Engels, A. Schürr: **Model-Based Software Product Lines Testing Survey**, in: J. Zander, I. Schieferdecker, P. Mosterman (eds.): Model-based Testing for Embedded Systems, CRC Press/Taylor & Francis, 339–381, 2011.

#### **Articles:**

• G. Perrouin, S. Oster, S. Sen, J. Klein, B. Baudry, Y. Traon: **Pairwise Testing for Software Product Lines: Comparison of Two Approaches**, in: Software Quality Journal - Special issue on Quality Engineering for Software Product Lines, Heidelberg: Springer Verlag, 2011.

#### **Refereed Conference And Workshop Papers:**

- S. Oster, M. Lochau, M. Zink, M. Grechanik: **Pairwise Feature-Interaction Testing for SPLs: Potentials and Limitations**, in: Proceeding of the 15th International Software Product Line Conference (SPLC'11), FOSD 2011 Workshop Proceedings, 2011.

- S. Oster, I. Zorcic, F. Markert, M. Lochau: "MoSo-PoLiTe Tool Support for Pairwise and Model-Based Software Product Line Testing", in: K. Czarnecki, U. Eisenecker (eds.), 4th International Workshop on Variability Modelling of Software-Intensive Systems, Namur, Belgium, 79–82, 2011.

- S. Oster, F. Markert, P. Ritter: "Automated Incremental Pairwise Testing of Software Product Lines", in: Proceedings of the 14th International Software Product Line Conference, Heidelberg: Springer Verlag, 196–210, 2010.

- S. Oster, P. Ritter, A. Schürr: "Featuremodellbasiertes und kombinatorisches Testen von Software-Produktlinien", in: Proceedings of the Software Engineering 2010; GI-Edition Lecture Notes in Informatics, Vol. 159, Gesellschaft für Informatik, 177-188, 2010.

- S. Oster, A. Schürr: "Architekturgetriebenes Pairwise-Testing für Software-Produktlinien", in: Software Engineering 2009 Workshop: Produkt-Variabilität im gesamten Lebenszyklus, 131–134, 2009.

- S. Oster, F. Markert, A. Schürr: "Integrated Modeling of Software Product Lines with Feature Models and Classification Trees", in: Proceedings of the 13th International Software Product Line Conference (SPLC'09), MAPLE 2009 Workshop Proceedings, Springer Verlag, 75–82, 2009.

- A. Schürr, S. Oster, F. Markert: "Model-Driven Software Product Line Testing: An Integrated Approach", in: Proceedings of the 36th International Conference on Current Trends in Theory and Practice of Computer Science; Lecture Notes in Computer Science (LNCS), 112-131, 2009.

- S. Oster, A. Schürr, I. Weisemöller: "Towards Software Product Line Testing using Story Driven Modelling", in: U. Aßmann, J. Johannes, A. Zündorf (eds.), Proceedings of the 6th International Fujaba Days, Technische Universität Dresden, 48-51, 2008.

### CONTENTS

| _  |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _                     |

|----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

|    |         | ODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                     |

| 1  |         | RODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3                     |

|    | 1.1     | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4                     |

|    | 1.2     | Contribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6                     |

|    |         | 1.2.1 Benefit for Industry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8                     |

|    |         | 1.2.2 Classification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8                     |

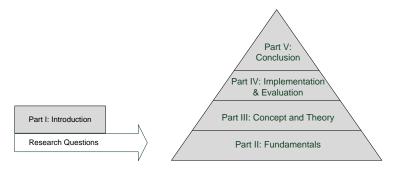

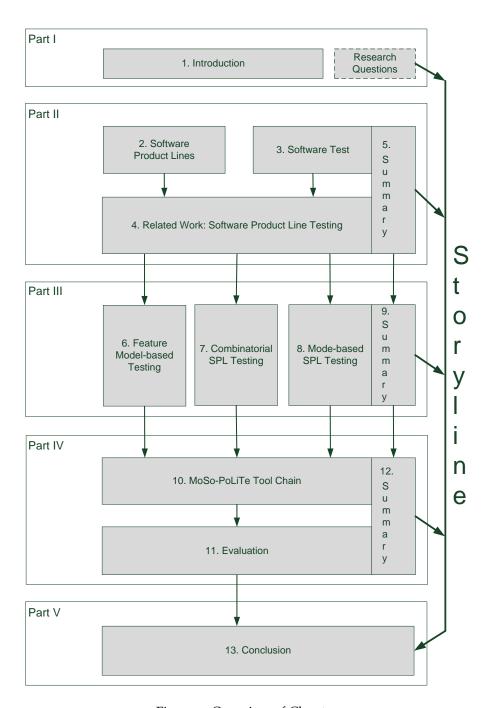

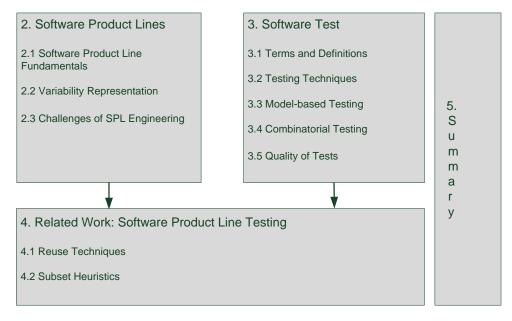

|    | 1.3     | Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8                     |

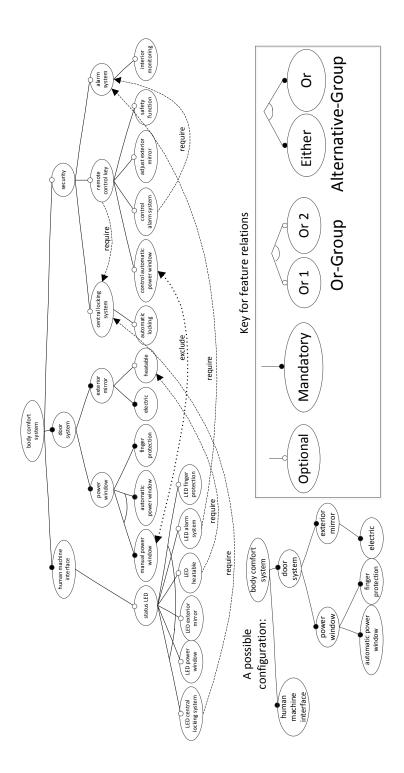

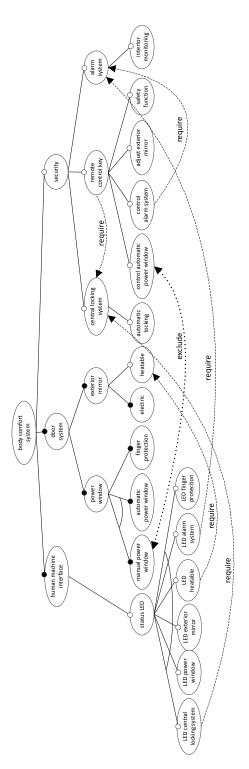

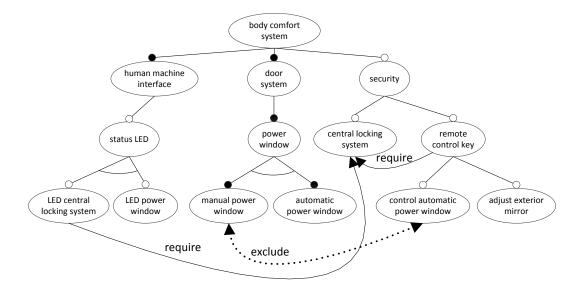

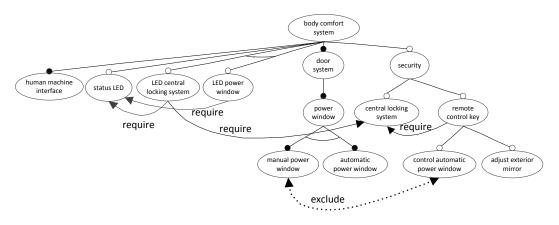

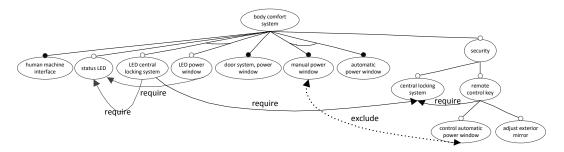

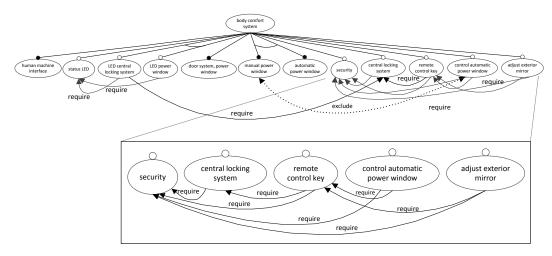

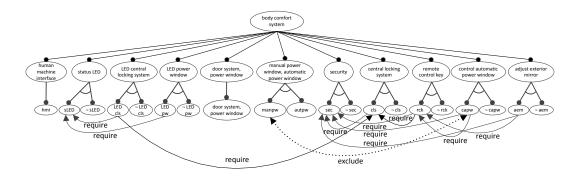

|    | 1.4     | Running Example: Body Comfort System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12                    |

| II | BACE    | KGROUND AND RELATED WORK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 15                    |

| 2  | SOF     | TWARE PRODUCT LINES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19                    |

|    | 2.1     | Software Product Line Fundamentals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 21                    |

|    |         | 2.1.1 Variability and Reuse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 23                    |

|    |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24                    |

|    | 2.2     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25                    |

|    |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26                    |

|    |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29                    |

|    | 2.3     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 30                    |

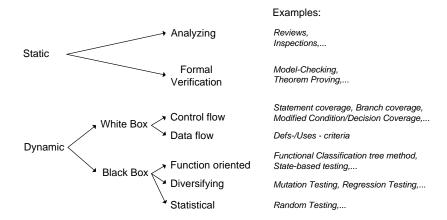

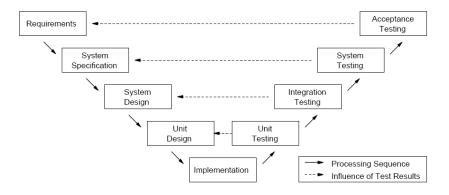

| 3  | SOF     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31                    |

| ,  | 3.1     | 15.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32                    |

|    | 3.2     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 34                    |

|    | ,       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 34                    |

|    |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 36                    |

|    | 3.3     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 36                    |

|    | 3.4     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 38                    |

|    | 3.5     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 42                    |

|    |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 42                    |

|    |         | No. of the control of | 44                    |

| 4  | REL     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45                    |

| 7  | 4.1     | D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 47                    |

|    | 7.2     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 48                    |

|    |         | 77 1 1 110 1 1 2 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <del>5</del> 6        |

|    |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 58                    |