# Fully Integrated Autonomous System-on-Chips with Wireless Energy and Data Transmission

Zur Erlangung des akademischen Grades Doktor-Ingenieur (Dr.-Ing.) Genehmigte Dissertation von Dominic Korner aus Offenbach am Main Tag der Einreichung: 6. September 2024, Tag der Prüfung: 21. November 2024

Gutachten: Prof. Dr.-Ing. Klaus Hofmann

Gutachten: Prof. Dr. Ralf Brederlow

Darmstadt, Technische Universität Darmstadt

Fully Integrated Autonomous System-on-Chips with Wireless Energy and Data Transmission

Accepted doctoral thesis by Dominic Korner

Date of submission: 6. September 2024 Date of thesis defense: 21. November 2024

Darmstadt, Technische Universität Darmstadt

Bitte zitieren Sie dieses Dokument als: URN: urn:nbn:de:tuda-tuprints-288133 URL: http://tuprints.ulb.tu-darmstadt.de/28813 Jahr der Veröffentlichung auf TUprints: 2024

Dieses Dokument wird bereitgestellt von tuprints, E-Publishing-Service der TU Darmstadt http://tuprints.ulb.tu-darmstadt.de tuprints@ulb.tu-darmstadt.de

Die Veröffentlichung steht unter folgender Creative Commons Lizenz: Namensnennung – Weitergabe unter gleichen Bedingungen 4.0 International https://creativecommons.org/licenses/by-sa/4.0/

This work is licensed under a Creative Commons License: Attribution–ShareAlike 4.0 International https://creativecommons.org/licenses/by-sa/4.0/

# Erklärungen laut Promotionsordnung

### §8 Abs. 1 lit. c PromO

Ich versichere hiermit, dass die elektronische Version meiner Dissertation mit der schriftlichen Version übereinstimmt.

### §8 Abs. 1 lit. d PromO

Ich versichere hiermit, dass zu einem vorherigen Zeitpunkt noch keine Promotion versucht wurde. In diesem Fall sind nähere Angaben über Zeitpunkt, Hochschule, Dissertationsthema und Ergebnis dieses Versuchs mitzuteilen.

### §9 Abs. 1 PromO

Ich versichere hiermit, dass die vorliegende Dissertation selbstständig und nur unter Verwendung der angegebenen Quellen verfasst wurde.

## §9 Abs. 2 PromO

Die Arbeit hat bisher noch nicht zu Prüfungszwecken gedient.

Darmstadt, 6. September 2024

Dominic Korner

# Acknowledgment

This work would have not been possible without the support of my colleagues and family. I want to especially thank Prof. Dr.-Ing. Klaus Hofmann for giving me the opportunity to write my thesis and for his support over the years.

I want to thank Jessica Wolf for designing the wonderful artwork for my ASICs. Furthermore, I would like to thank the following colleagues and friends for numerous discussions and/or proof-reading of my thesis: Andreas Kramer, David Riehl, Henning Ahrens, Jana Späth, Katrin Hirmer, Markus Graber, Sebastian Santos, Timo Oster, and Viktor Weinelt.

I would also like to thank the administrative support from Andreas Schmidt, Caroline Pierre, Roland Brandt, and Silvia Hermann.

Large language models were used to enhance the writing style and grammar of this thesis with tools from Grammarly Inc. and DeepL SE.

# Abstract

Integrated autonomous **S**ystem-**o**n-**C**hips (SoCs) with wireless data and energy transmission enable applications in areas that were previously inaccessible due to size constraints or the lack of an energy source. Depending on the transmission medium, the integration of an energy source and communication into the **A**pplication-**S**pecific Integrated **C**ircuit (ASIC) requires specialized circuitry. Ideally, an autonomous SoC consists of a single ASIC, requiring no external components for operation, making it hereby particularly small.

This work focuses on developing, designing, and fabricating autonomous SoCs with the smallest possible size and as few external components as feasible while still being capable of energy and data transmission. Four different ASICs have been designed and fabricated for three different applications. Two fabricated ASICs use ultrasound for energy and bidirectional data transmission, whereas the other two ASICs use visible light for energy and unidirectional data transmission.

The ultrasonic-powered systems presented are a Sensor-integrated Machine element (SiMe) and a medical smart implant. The SiMe can generate a power of  $60 \,\mathrm{mW}$ , providing power to sensors even in fully encapsulated metal enclosures deep inside the machine. The medical smart implant focuses on minimal-sized implants for the human body.

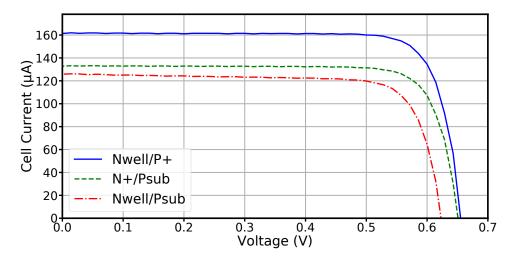

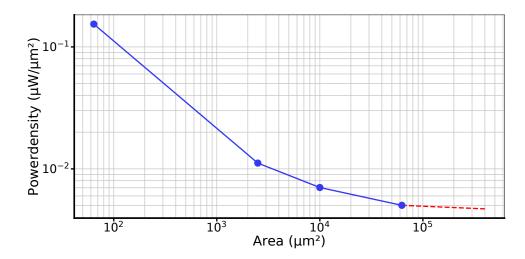

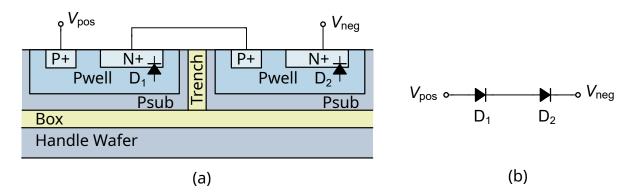

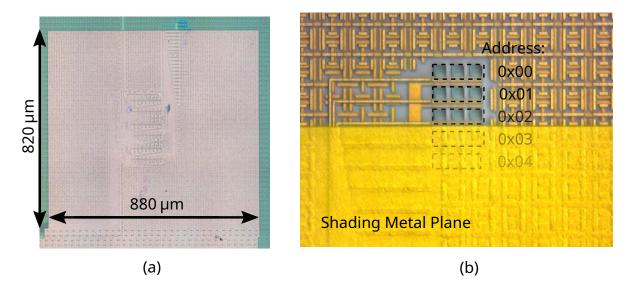

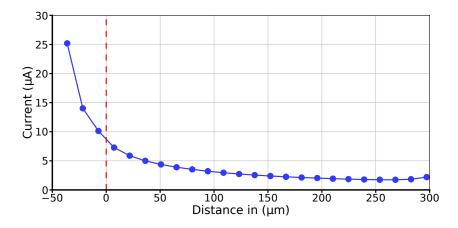

External piezoelectric crystals, required for ultrasound, consume much space compared to the size of an ASIC. Visible light as an energy and data carrier offers the possibility to integrate all components into a single die by using on-chip solar cells. The presented system for discovering novel drug candidates with an ASIC tag uses visible light as an energy and data carrier, and therefore requires no external components. It operates at a high illumination intensity of 10 Mlx, decreasing the overall system size to a minimum. A single solar cell generates voltages of up to 0.7 V, which is not enough to supply the ASIC. Instead of charge pumps, which consume energy and chip area, a serialization of solar cells in a **S**ilicon-**o**n-Insulator (SOI) technology provides the required supply voltage. To predict the power generated by the solar cell array on the ASIC, different types of solar cells are fabricated and measured. Light encountering the ASIC generates leakage current on the p-n junctions in sensitive circuitry. A countermeasure was taken to reduce the light-induced leakage currents: Measurements show a reduction of the leakage current by over 90% when using a metal shield and give instructions on how to design it.

This thesis provides design and implementation recommendations for autonomous SoCs with wireless energy and data transmission. It considers light and ultrasound transmission principles for energy and data, as well as provides a system architecture overview for the implementation. The fabricated ASICs prove the effectiveness of the presented recommendations.

# Zusammenfassung

Neuartige integrierte autonome **S**ystem-**o**n-**C**hips (SoCs) mit drahtloser Energie- und Datenübertragung ermöglichen Anwendungen in Bereichen die bisher aufgrund von Größenbeschränkungen oder dem Fehlen einer Energiequelle unzugänglich waren. Je nach verwendetem Übertragungsmedium, erfordert die Integration von Energiequelle und Kommunikation in den **A**pplication-**S**pecific Integrated **C**ircuit (ASIC) spezielle Schaltungen. Im Idealfall besteht der autonome SoC ausschließlich aus einem einzigen ASIC ohne weitere externe Bauteile zu benötigen und ist dadurch besonders klein.

Diese Arbeit befasst sich mit der Entwicklung und Herstellung von autonomen SoCs mit der kleinstmöglichen Größe und so wenig wie möglichen externen Komponenten, wobei sie dennoch Energie und Daten übertragen können müssen. Es wurden vier verschiedene ASICs für drei verschiedene Anwendungen entwickelt. Zwei der hergestellten ASICs verwenden Ultraschall für eine bidirektionale Datenübertragung, während die anderen beiden ASICs sichtbares Licht für eine unidirektionale Datenübertragung verwenden.

Bei den ultraschallbasierten Systemen handelt es sich um ein **S**ensorintegriertes **M**aschinenelement (SiMe) und ein Implantat für den menschlichen Körper. Das SiMe kann eine Leistung von bis zu 60 mW in einem hermetisch geschlossenen Metallgehäuse bereitstellen und somit eine stabile Versorgung von Sensoren mit Strom im Inneren von Maschinen gewährleisten. Das medizinische Implantat hingegen ist besonders auf eine minimale Größe ausgelegt.

Im Vergleich zur Größe eines ASICs brauchen externe piezoelektrische Kristalle viel Platz. Sichtbares Licht als Energie- und Datenträger hingegen eröffnet die Möglichkeit, alle erforderlichen Komponenten mithilfe von On-Chip Solarzellen in einen einzigen Chip zu integrieren. Das vorgestellte System für die Wirkstofffindung in der Medizin nutzt sichtbares Licht zur Energie- und Datenübertragung und benötigt daher keine externen Komponenten. Um die Größe des Systems weiter zu minimieren, arbeitet es mit einer hohen Lichtstärke von 10 Mlx. Eine Herausforderung ist hierbei, dass eine einzelne Solarzelle eine Spannung von bis zu 0.7 V erzeugt. Diese Spannung reicht nicht für die Versorgung eines ASICs aus. Um Ladungspumpen welche Energie und Chipfläche benötigen zu vermeiden, können zur Erzeugung der Versorgungsspannung stattdessen Solarzellen in einer **S**ilicon-**o**n-Insulator (SOI) Technologie in Reihe geschaltet werden. Um die erzeugte Leistung des Solarzellen-Arrays vorherzusagen, werden verschiedene Solarzellen gefertigt und vermessen. Licht, das auf den ASIC trifft, erzeugt Leckströme in den p-n-Übergängen. Eine Metallabschirmung sorgt für eine Verringerung der Leckströme um über 90 %.

Diese Arbeit gibt Designempfehlungen für autonome SoCs mit drahtloser Energie- und Datenübertragung. Es werden Licht und Ultraschall und die dafür benötigte Systemarchitektur vorgestellt. Die gefertigten ASICs zeigen die Wirksamkeit der vorgestellten Empfehlungen.

# Contents

| Ab  | ostract                                                                                                                                                                                                                                                                                                                                           | vii                                                                                                                          |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Zu  | Isammenfassung                                                                                                                                                                                                                                                                                                                                    | ix                                                                                                                           |

| Lis | st of Abbreviations                                                                                                                                                                                                                                                                                                                               | xxi                                                                                                                          |

| Lis | st of Symbols                                                                                                                                                                                                                                                                                                                                     | xxiii                                                                                                                        |

| I.  | Introduction to Autonomous System-on-Chips                                                                                                                                                                                                                                                                                                        | 1                                                                                                                            |

| 1.  | Introduction1.1. Research Scope and Contribution1.2. Thesis Outline                                                                                                                                                                                                                                                                               | <b>3</b><br>4<br>6                                                                                                           |

| 2.  | System Architecture of Autonomous System-on-Chips         2.1. Wireless Power Transfer         2.1.1. Inductive Coupling         2.1.2. Capacitive Coupling         2.1.3. Ultrasound         2.1.4. Electromagnetic Waves         2.2.1. Antenna         2.2.2. Energy Management         2.2.3. Communication         2.2.4. Digital Processing | <ul> <li>7</li> <li>8</li> <li>8</li> <li>8</li> <li>9</li> <li>9</li> <li>10</li> <li>11</li> <li>12</li> <li>13</li> </ul> |

| II. | Solar and Ultrasonic Power Transmission                                                                                                                                                                                                                                                                                                           | 15                                                                                                                           |

| 3.  | Introduction to Solar Power Transmission3.1. Photoelectric Effect3.2. Simulation Model and Equivalent Circuit of a Solar Cell3.3. Solar Cells for Integrated Circuits                                                                                                                                                                             | <b>17</b><br>17<br>18<br>20                                                                                                  |

| 4.   | Introduction to Ultrasonic Power Transmission<br>4.1. Equivalent Circuit                                                                                                                                                                                                                                                                                                        | <b>21</b><br>22                         |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

|      | <ul> <li>4.1. Equivalent Circuit</li></ul>                                                                                                                                                                                                                                                                                                                                      | 22                                      |

| III. | Implemented and Fabricated Autonomous System-on-Chips with Wireless<br>Energy and Data Transmission                                                                                                                                                                                                                                                                             | 25                                      |

| 5.   | Ultrasonic Powered ASIC for Sensor Integrated Machine Elements         5.1. Bidirectional Ultrasonic Communication         5.1.1. Receive Protocol         5.1.2. Transmit Protocols         5.2. Implemented SoC for Sensor Integrated Machine Elements         5.2.1. Schematic Implementation         5.2.2. Fabricated ASIC and Demonstrator         5.3. ASIC Measurements | 27<br>28<br>29<br>31<br>32<br>38<br>42  |

|      | 5.4. Summary                                                                                                                                                                                                                                                                                                                                                                    | 46                                      |

| 6.   | Ultrasonic Powered ASIC for Medical Smart Implants         6.1. Bidirectional Ultrasonic Communication and Location of the implant         6.2. Implemented ASIC for Medical Smart Implants         6.2.1. Schematic Implementation         6.2.2. Fabricated ASIC and Experimental Setup         6.3. Summary                                                                  | <b>47</b><br>48<br>49<br>50<br>54<br>59 |

| 7.   | Light Powered ASIC Tag for Discovery of Novel Drug Candidates         7.1. Split and Pool Synthesis                                                                                                                                                                                                                                                                             | 67                                      |

| IV.  | Results and Conclusion                                                                                                                                                                                                                                                                                                                                                          | 77                                      |

| 8.   | Design of Autonomous System-on-Chips8.1. System Size vs. Wavelength                                                                                                                                                                                                                                                                                                             | <b>79</b><br>79                         |

|     | <ul> <li>8.2. Systems with External Components</li></ul>            | 80<br>82<br>82<br>82<br>85<br>85 |

|-----|---------------------------------------------------------------------|----------------------------------|

|     | Conclusion and Outlook         9.1. Conclusion         9.2. Outlook |                                  |

| V.  | Appendix                                                            | 91                               |

| Bib | bliography                                                          | 93                               |

| Lis | t of Own Publications                                               | 101                              |

| Sup | pervised Theses                                                     | 103                              |

| Ver | rilog-A Solar Cell Model                                            | 105                              |

# List of Figures

| 1.1. Building Blocks Autonomous System-on-Chips1.2. Thesis Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4<br>5                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| <ul><li>2.1. System Architecture Overview</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7<br>10                                                                          |

| <ul> <li>3.1. Solar Cell Sectional View</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 17<br>18<br>19<br>20<br>20                                                       |

| <ul> <li>4.1. Inner Structure Piezoelectric Crystal</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 21<br>22<br>23<br>24                                                             |

| 5.1. M20 Bolt with Integrated Electronic5.2. Communication Protocol Receive5.3. Communication Protocol Transmit Backscatter5.4. Communication Protocol Transmit FM and On/Off5.5. Communication Protocol Transmit Resonance Modulation5.6. System Overview SoC SiMe5.7. Bandgap Reference5.8. Voltage Regulator5.9. Power-on Reset Circuit5.10. Active Rectifier Schematic5.11. RC Oscillator5.13. Digital Controlled RC Oscillator5.14. Digital Controlled RC Oscillator Simulation5.15. Output Stage for Piezoelectric Crystal5.16. Dieshot SiMe (Archimedes)5.17. Experimental Setup | 27<br>29<br>30<br>31<br>33<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41 |

| 5.18. Piezoelectric Crystal Driver PCB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 41                                                                               |

#### 6.1. Application Example Medical Smart Implant 6.2. Communication Protocol Receive 6.3. Communication Protocol Transmit 6.4. Location Beacon Protocol 6.5. Block Diagram ASIC for Medical Smart Implant 6.8. Power-on Reset Circuit 6.10. Ultrasonic Clock Extractor 6.14. Ultrasonic Board Medical Smart Implant 6.15. Piezoelectric Crystal for Medical Smart Implant 6.16.Experimental Setup Medical Smart Implant 7.3. Optical Communication Protocol 7.6. Power-on Reset Generator 7.7. Bandgap Reference 7.11. Die Shot Light Powered ASIC Tag (Anton) 8.1. Wavelength for Wireless Power Transfer

| 8.3. | Series Connection Solar Cells        | 84 |

|------|--------------------------------------|----|

| 8.4. | Series Connection Photodiodes        | 84 |

| 8.5. | Photograph Shading Metal Plane       | 87 |

| 8.6. | Photodiode Current Below Metal Plane | 88 |

# **List of Tables**

| 5.1. | Active Rectifier Comparison                  | 45 |

|------|----------------------------------------------|----|

|      | Technology Overview    Smart Dust Comparison |    |

# **List of Abbreviations**

| AC     | Alternating Current                                 |

|--------|-----------------------------------------------------|

| ADC    | Analog-to-Digital Converter                         |

| AM     | Amplitude Modulation                                |

| ASIC   | Application-Specific Integrated Circuit             |

| BB     | Building Block                                      |

| Box    | Buried oxide                                        |

| CMOS   | Complementary Metal-Oxide-Semiconductor             |

| DAC    | Digital-to-Analog Converter                         |

| DC     | Direct Current                                      |

| DRAM   | Dynamic Random Access Memory                        |

| EEPROM | Electrically Erasable Programmable Read-Only Memory |

| ESD    | Electrostatic Discharge                             |

| ESR    | Equivalent Series Resistance                        |

| FDA    | U.S. Food and Drug Administration                   |

| FM     | Frequency Modulation                                |

| FPGA   | Field Programmable Gate Array                       |

| IC     | Integrated Circuit                                  |

| LDO    | Low-Dropout                                         |

| LED    | Light-Emitting Diode                                |

| LNA    | Low Noise Amplifier                                 |

| MIM    | Metal-Insulator-Metal                               |

| MOS    | Metal-Oxide-Semiconductor                           |

| MOSFET | Metal-Oxide-Semiconductor Field-Effect Transistor   |

| MPPT   | Maximum Power Point Tracking                        |

| MTP    | Multiple-Time-Programmable                          |

|        |                                                     |

| NVM                              | Non-Volatile Memory                  |  |  |

|----------------------------------|--------------------------------------|--|--|

| OOK                              | On-Off Keying                        |  |  |

| OTP                              | One-Time-Programmable                |  |  |

| PCB                              | Printed Circuit Board                |  |  |

| PTAT                             | Proportional to Absolute Temperature |  |  |

| PVT                              | Process, Voltage, Temperature        |  |  |

| RF                               | Radio Frequency                      |  |  |

| RFID                             | Radio Frequency Identification       |  |  |

| S-parameter Scattering-parameter |                                      |  |  |

| SiMe                             | Sensor-integrated Machine element    |  |  |

| SMD                              | Surface-Mounted Device               |  |  |

| SoC                              | System-on-Chip                       |  |  |

| SOI                              | Silicon-on-Insulator                 |  |  |

| SPI                              | Serial Peripheral Interface          |  |  |

| SRAM                             | Static Random-Access Memory          |  |  |

| USB                              | Universal Serial Bus                 |  |  |

| UV                               | Ultraviolet                          |  |  |

| VNA                              | Vector Network Analyzer              |  |  |

|                                  |                                      |  |  |

# List of Symbols

| Symbol         | Unit                         | Definition                                              |

|----------------|------------------------------|---------------------------------------------------------|

| A              | $m^2$                        | Area                                                    |

| C              | F                            | Capacitance                                             |

| $c^{E}_{3333}$ | ${ m Nm^{-2}}$               | Electroelastic coefficient                              |

| d              | m                            | Diameter of a piezoelectric crystal                     |

| e              | С                            | Elementary charge                                       |

| f              | Hz                           | Frequency                                               |

| $f_p$          | Hz                           | Parallel resonance frequency                            |

| $f_r$          | Hz                           | Resonance frequency                                     |

| $f_s$          | Hz                           | Series resonance frequency                              |

| h              | ${ m kg}{ m m}^2{ m s}^{-1}$ | Planck constant                                         |

| Ι              | А                            | Current                                                 |

| $I_L$          | А                            | Load current                                            |

| $I_s$          | А                            | Reverse-bias saturation current                         |

| $I_{SC}$       | А                            | Short circuit current                                   |

| k              |                              | Number of ASICs                                         |

| l              | m                            | Length                                                  |

| m              |                              | Number of stages in a split and pool synthesis          |

| N              |                              | Number of generated compounds                           |

| $N_r$          | $\mathrm{Hzm}$               | Frequency constant of a piezoelectric crystal           |

| P              | W                            | Power                                                   |

| Q              | С                            | Charge                                                  |

| R              | Ω                            | Resistance                                              |

| $R_L$          | Ω                            | Load resistance                                         |

| S              |                              | Scattering parameters                                   |

| s              |                              | Different building blocks in a split and pool synthesis |

| T              | Κ                            | Temperature                                             |

| t              | s                            | Time                                                    |

| V              | V                            | Voltage                                                 |

| v              |                              | Resonating mode                                         |

| $V_{OC}$       | V                            | Open circuit voltage                                    |

| $V_T$          | V                            | Threshold voltage of a MOSFET                           |

| Ζ              | Ω                            | Impedance                                               |

| Symbol     | Unit                       | Definition                           |

|------------|----------------------------|--------------------------------------|

| $\lambda$  | m                          | Wavelength                           |

| ho         | ${ m kg}{ m m}^{-3}$       | Volumetric mass density              |

| $	au_x$    | m                          | Thickness of a piezoelectric crystal |

| $\Phi$     | ${\rm m}^{-2}{\rm s}^{-1}$ | Photon flux density                  |

| $\Omega^v$ | Hz                         | Dimensionless eigenfrequency         |

Part I.

# Introduction to Autonomous System-on-Chips

# 1. Introduction

In 1959, Jack Kilby patented his idea of the first Integrated **C**ircuit (IC) [1]. However, it would be unfeasible to mass produce the IC since it still required gold wires for the connection of the individual transistors. A few months later, Robert Noyce invented the first silicon IC based on an idea from Jean Hoerni [2]. The following years showed that the number of components in an IC is increasing exponentially. In 1965, Gordon Moore predicted a yearly doubling of components on each chip [3]. Ten years later, he renders his statement more precisely to a doubling of components every two years [4]. This forecast was true for about 50 years but the doubling of components is slowing down recently, as Moore stated in 2015 [5]. New concepts have to be explored for further scaling of **C**omplementary **M**etal-**O**xide-**S**emiconductor (CMOS) ICs [6].

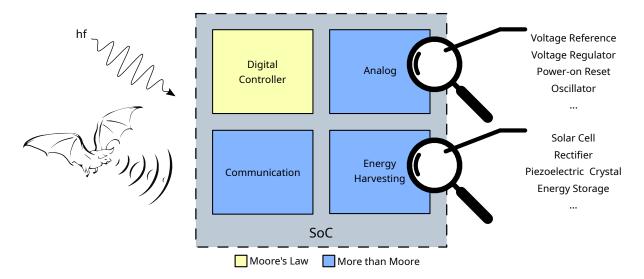

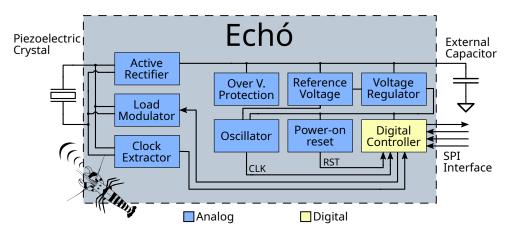

To achieve a higher level of integration, additional functions have to be included in an IC, which were formerly discrete components on a **P**rinted **C**ircuit **B**oard (PCB). Integrating additional components like sensors, analog, and digital circuits into a single silicon chip is called More than Moore [7]. By integrating additional functionality into a chip, the size of the overall system becomes significantly smaller. Additionally, the energy efficiency can be increased by omitting no longer required connections and power supplies on the PCB, although these components do not follow Moore's law itself. Such systems are called **S**ystem-**o**n-**C**hips (SoCs). Figure 1.1 shows the building blocks of SoCs with a digital controller, which follows Moore's law, and various analog components, which do not scale so well with smaller transistor sizes. The analog block has to provide different functions on the SoC, for example, reference voltages, power-on reset, and clock sources. Besides these functions, circuitry for energy management, energy harvesting, and communication interfaces have special demands on the **A**pplication-**S**pecific Integrated **C**ircuit (ASIC) and might require special process technologies. The reduced size for the overall systems is of the highest importance and enables new application fields in space-limited environments.

This thesis presents ASIC-based communication systems powered solely wirelessly with no external power supply. Four fabricated ASICs for three application areas are introduced in this work. Each ASIC is optimized for its application, demonstrating fully integrated autonomous system-on-chips with wireless energy and data transmission.

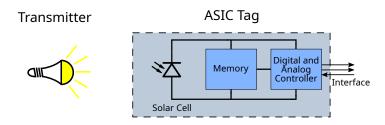

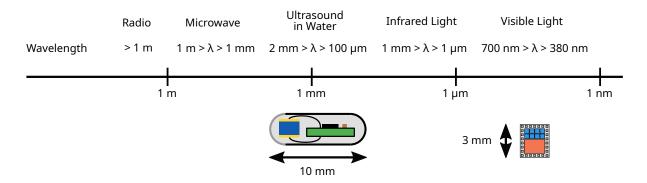

Two ASICs use ultrasound for energy and data transmission. The presented **S**ensor-integrated **M**achine element (SiMe) focuses on high power ultrasound transmission through a metal enclosure in a compact format, while the smart implant focuses on the overall size of the system. Ultrasound requires external piezoelectric crystals, which consume additional space inside the system. To develop even smaller systems, visible light can be chosen. The developed light-powered ASIC

for the discovery of novel drug candidates integrates solar cells directly into the ASIC. Since the power receiver is integrated into the ASIC, no external components are required, making it a single-chip solution and herewith extremely small. However, light induces leakage currents in the circuitry on the ASIC, a metal shield for counteracting this effect is presented.

Figure 1.1.: Building blocks of fully integrated autonomous system-on-chips with wireless energy and data transmission.

# 1.1. Research Scope and Contribution

This thesis investigates the integration of energy autonomous systems into a single ASIC, including a power management system and a communication interface. A key aspect is ultrasonic and solar energy transmission including data transfer using as few external components as possible. This work presents three different applications, with individually designed and manufactured ASICs for their best performance in the particular use case. As a result, the following research questions are dealt with and answered:

- How to minimize the overall system size using autonomous self-powered SoCs? A smaller system allows new areas of application that can be accessed as a result of the reduced size.

- Is it possible to integrate autonomous SoCs with wireless energy and data transmission into a single ASIC? More than Moore technologies provide a suitable basis for the integration of such systems into a single ASIC.

- How can the power supply be integrated into the ASIC? External elements like antennas or solar cells consume a large area of the system. Integration directly on the ASIC would decrease the overall system size significantly.

- How to counteract light-induced leakage currents on the ASIC? Light generates leakage currents on a p-n junction in the ASIC causing low power circuits to consume more energy than necessary.

# 1.2. Thesis Outline

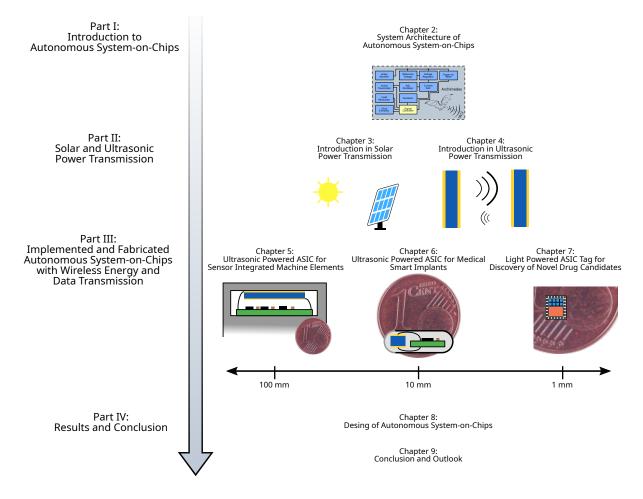

The outline of this thesis is illustrated in Figure 1.2. After the brief introduction in Part I, Chapter 2 focuses on the general system architecture of autonomous integrated systems and explains the required system components for integration. Part II introduces ultrasound and solar energy harvesting for ASICs in Chapters 3 and 4.

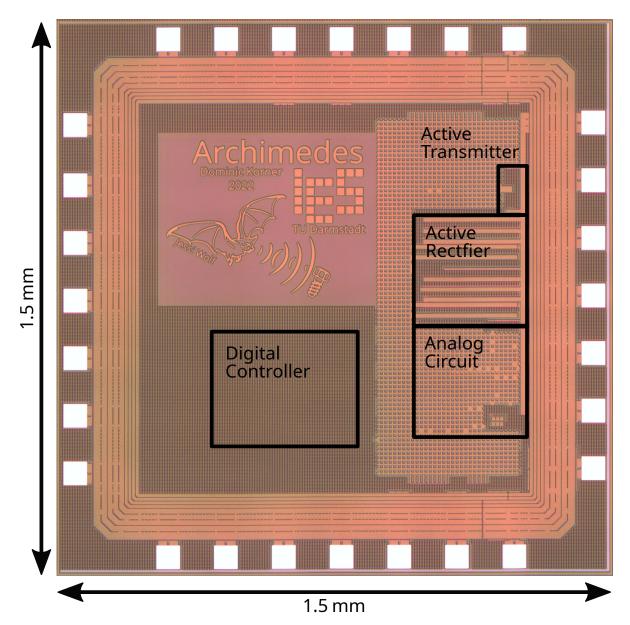

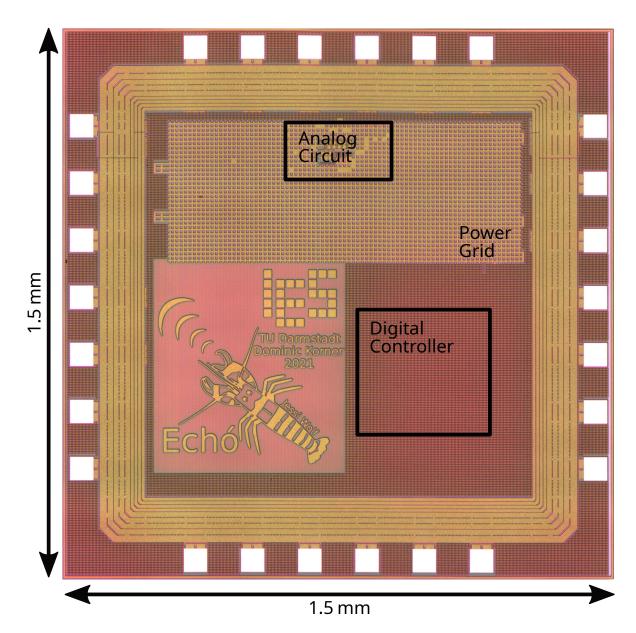

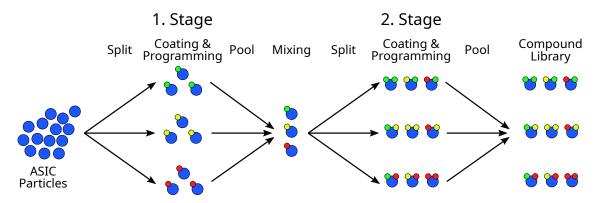

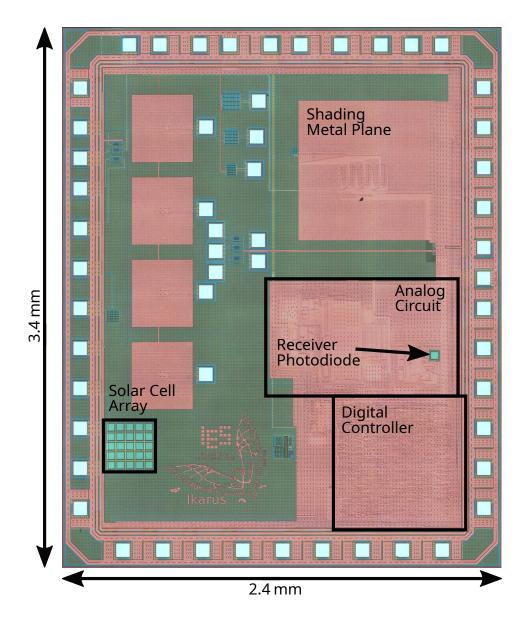

Part III presents four manufactured ASICs, each designed for a different application. Chapter 5 shows an ultrasonic-powered SiMe. It is optimized for high energy transfer, as well as high data throughput. Chapter 6 introduces a smart implant powered by ultrasound. Due to a size limit of  $2 \text{ mm} \times 2 \text{ mm} \times 10 \text{ mm}$ , the ASIC integrates everything except a piezoelectric crystal and an energy storage. Because of the small piezoelectric crystal, the system focuses particularly on low power consumption. Chapter 7 presents the smallest system in this thesis that does not need any external components. It integrates all necessary components like energy harvesting, communication, and memory into one single ASIC. Its energy supply and communication are based on visible light, making the system extremely small, with an area of only  $8.16 \text{ mm}^2$ . Particular focus is put on low power consumption and light-induced leakage.

Part IV presents the findings of the fabricated ASICs. Chapter 8 gives recommendations for designing autonomous systems with wireless energy and data transmission on an ASIC scale. Finally, Chapter 9 concludes the presented designs and gives an outlook for future developments and research in this field.

# 2. System Architecture of Autonomous System-on-Chips

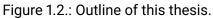

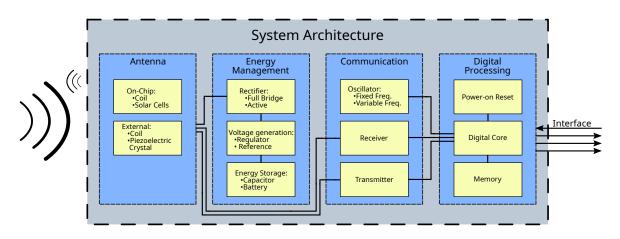

Autonomous SoCs with wireless energy and data transmission in space-limited applications require a high degree of integration to fit the system in the designated place. These systems cover various application areas, such as ultrasonic implants for the human body to record health data or wirelessly powered integrated machine elements to monitor a machine [8, 9]. This chapter provides a brief overview of wireless power transfer techniques and the integrated components in the SoC. Figure 2.1 shows the general system architecture of an autonomous SoC.

Figure 2.1.: System architecture for energy autonomous SoCs with wireless energy and data transmission and the required and optional components.

These systems have a similar architecture as a basis, including an external transceiver for energy and data transmission. It requires an antenna to receive the energy and the data sent by the external host. Connected to the antenna is an energy management circuit, to convert the power received by the antenna to voltages suitable for the ASIC. In most cases, this circuit has to rectify an Alternating Current (AC) voltage and stabilize it. Additionally, reference voltages are often required for supplying sensitive analog circuitry. An energy storage might be necessary, depending on the application of the system and the continuity and quantity of the delivered power. Besides energy, the antenna also receives data for communication. It is the purpose of the communication module to decode the received data. If bidirectional communication is desired, the module also has to include a transmitter. A digital processing circuit is implemented to process the received data and if necessary to execute received commands. It can consist of a state machine, particularly designed for one purpose, or a microcontroller, which gives more flexibility. Depending on the application, the digital processing unit can connect various optional internal or external components, including but not limited to sensors, memories, or actuators. The following Section 2.1 introduces different wireless power transfer methods, while Section 2.2 explains the required components in such systems.

# 2.1. Wireless Power Transfer

There are multiple methods to supply integrated autonomous SoC with wireless power, but not all of them are suitable for energy transmission. Subsequently, different wireless power transfer techniques are summarized and rated with regard to the suitability for integrated autonomous SoCs.

### 2.1.1. Inductive Coupling

Inductive power transfer is widely used as energy transfer in household appliances, like toothbrushes or the well-known Qi interface standard for wireless power transfer [10]. It is based on Faraday's law of induction, discovered in 1831 by Michael Faraday [11]. A magnetic field is generated with a wire coil, while a second coil converts the magnetic field back to an AC voltage. A study for biomedical implants shows that for small systems, which are of particular interest in this thesis, inductive energy transfer is outperformed by ultrasonic energy transfer for receiver diameters smaller than 3 mm. At source-receiver distances higher than 14 mm, ultrasound is even more efficient than receivers with a size of 5 mm or smaller [12].

### 2.1.2. Capacitive Coupling

Capacitive coupling between two electrodes uses the electric field to transfer energy. The transmitter electrode plates are driven with a high frequency AC voltage, which induces a voltage on the receiver plate. Although this technique is rarely used for end-consumer products due to the high voltage and frequency required, recent research has shown capacitively coupled power transfer techniques for low power implants [13, 14]. For capacitive plates with a size of  $20 \text{ mm} \times 20 \text{ mm}$  and a distance of 3 mm, a power transmission of up to 100 mW was achieved in compliance with safety guidelines for human tissue [15].

### 2.1.3. Ultrasound

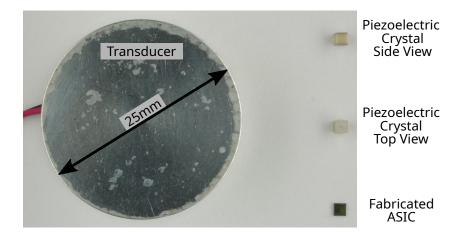

Sound waves with a frequency of more than 20 kHz are called ultrasonic waves. Ultrasound is known for measuring distances, detecting objects, cleaning objects, or as a non-invasive imaging tool in medicine [16]. Piezoelectric crystals provide an efficient method for converting electrical signals into ultrasonic waves and vice versa. For frequencies above around 1 MHz, piezoelectric crystals become small enough, i.e. longest dimension below 1 mm, to be used as power and

communication device in the human body. For example, a piezoelectric crystal cube with an edge length of  $750 \,\mu\text{m}$  at a frequency of  $1.85 \,\text{MHz}$  can receive up to  $350 \,\mu\text{W}$ , in compliance with the U.S. Food and Drug Administration (FDA) safe density limit of  $7.2 \,\mathrm{mW} \,\mathrm{mm}^{-2}$  for the transmitter [17].

### 2.1.4. Electromagnetic Waves

History has given different names for the electromagnetic spectrum. Sorted from a long to short wavelength, it includes radio waves, microwaves, infrared light, visible light, ultraviolet light, X-rays, and gamma rays [18]. Radio waves, microwaves, infrared, and visible light in limited intensity are considered harmless to most organisms including the human body. Therefore, these electromagnetic waves represent a possible transmission medium and are considered in more detail.

#### **Radio Waves and Microwaves**

In 1887 Heinrich Hertz discovered the existence of radio waves [19]. The size of antennas required for an efficient transmission for radio and microwaves depends on the wavelength and the antenna type. An often-used dipole antenna needs a wire length of half the wavelength, which results in an antenna length in the range of a few mm to one meter. Increasing the frequency and hereby decreasing the antenna size is an option, but the attenuation of the electromagnetic wave in human tissue will increase with the frequency. Small implants proved to work with a harvesting coil diameter of 2 mm at a depth of 5 cm while receiving a power of  $200 \,\mu\text{W}$  at a transmit power of  $500 \,\text{mW}$  [20].

#### Infrared and Visible Light

Infrared and visible light have a wavelength from  $400 \,\mathrm{nm}$  to  $10 \,\mu\mathrm{m}$ . To receive and convert light to electricity, solar cells offer a high energy conversion efficiency. Additionally, solar cells can be directly integrated into an ASIC due to the silicon substrate. Energy densities of up to  $12 \,\mathrm{W} \,\mathrm{cm}^{-2}$  are demonstrated. By increasing the light intensity higher energy densities are possible, practically only limited by the heating of the ASIC by the incident light [21].

# 2.2. Required Components in Wireless-Powered ASICs

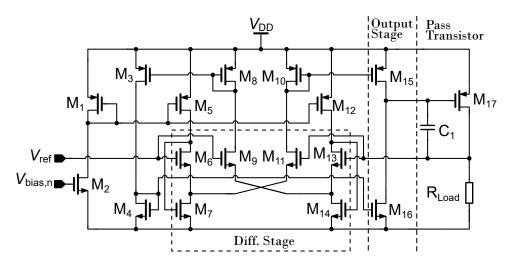

The previously mentioned architecture of wirelessly powered SoCs is divided into four major building blocks, shown in Figure 2.2. The antenna converts the received energy, which could be electromagnetic waves or a different method, into an electrical voltage. The subsequent energy management block provides a stable **D**irect **C**urrent (DC) voltage for the operating circuit. It usually includes a rectifier circuit, a **L**ow-**D**rop**o**ut (LDO), and a reference voltage generator, as well as an energy storage. A communication module incorporates a receiver and transmitter to implement a bidirectional communication interface. At last, a digital processing block handles

communication and potential additional tasks like sensor management. The following subsections will dive into further detail of each building block.

Figure 2.2.: Detailed building block for wireless-powered SoCs.

### 2.2.1. Antenna

In general, there are two possibilities for placing the antenna: On-chip antennas (internal) integrated into the system or off-chip antennas (external) as an additional device connected to the system. On-chip antennas have the big advantage of being very small compared to external ones, at the expense of energy efficiency and maximum range.

### Internal

A standard CMOS process only allows coils or solar cells as a direct implementation. It limits the received signals to electromagnetic waves for the wavelength of radio waves, microwaves, and light. In each case the die size limits the maximum size of the antenna, leading to a small energy yield.

#### External

External antennas extend the application area to other transmission methods like ultrasound by using a piezoelectric crystal or inductive and capacitive coupling at the expense of a larger device. Additionally, larger antennas have a higher sensitivity compared to internal antennas and can therefore still work with lower energy densities.

### 2.2.2. Energy Management

The energy received by the antenna is often a high frequency AC voltage with low amplitude, therefore the first block for energy management is a rectification circuit. This is not a requirement if solar cells are used. The rectified voltage needs an LDO for stabilization. Additional voltage references provide an accurate voltage for the analog components. The optional energy storage provides a stable voltage or energy for the ASIC in phases without active energy transmission or for short bursts of increased power consumption i.e. sensor activation or data transmission.

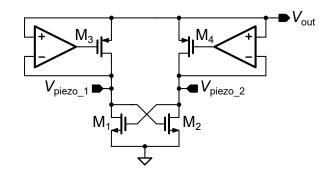

### Rectifier

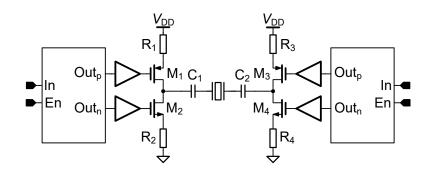

As mentioned previously most methods using an antenna will convert the input to a high frequency AC voltage with low amplitude and require a rectification circuit. In general, there are two possibilities for rectifying an AC voltage: passive or active rectification circuits. Passive rectification with diodes is simple and reliable but lowers the output voltage by at least one diode drop voltage. For a full bridge rectifier with two diodes in the conduction path, it increases the voltage drop to two diode drop voltages. That would decrease the obtainable output voltage by approximately 0.7 V or 1.4 V for silicon diodes. While Schottky diodes would have a lower drop voltage they are often not available in CMOS processes. This would limit the usable energy significantly and decrease the overall energy efficiency. An active rectifier can replace the diodes with transistors, lowering the drop voltage significantly. Naturally, the active control mechanism has to be fast enough to switch the transistors according to the AC voltage, which makes it hard to build active rectifiers for **R**adio Frequency (RF) applications that have very high frequencies. However, this is a common choice for ultrasound applications as they operate with lower frequencies [22].

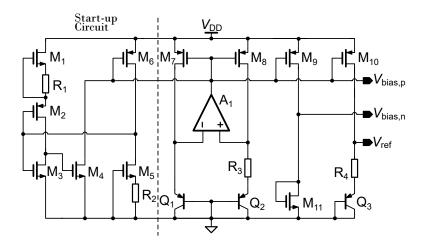

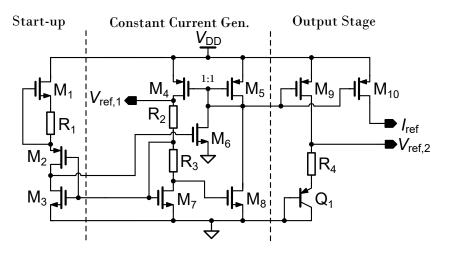

#### **Reference Voltage Generation**

Analog and digital circuitry need a stable supply voltage to operate in the given specifications. A reference voltage circuit can provide a stable voltage reference to the ASIC. Depending on the necessary precision of the reference voltage and the allowed maximum power dissipation, a solely Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET)-based reference or a more stable bandgap voltage reference is suitable. Compared to bandgap voltage references, a MOSFET-based reference usually has a smaller area and a lower power consumption [23]. If precision is the main concern and power or area are less important, a bandgap reference has a more process-robust reference voltage [24]. Since the reference circuits usually operate with a constant current, a bias current can be derived for components on the ASIC. Important to note here is that these currents usually are not temperature compensated. With a working reference voltage, an LDO can supply the circuit with a stable supply voltage.

### **Energy Storage**

If the application has phases with no active power transmission or short bursts with high power consumption, an energy storage has to supply the system to prevent a non-intermittent operation.

Since on-chip capacitors are usually only fabricable in the range of a few picofarads, this will only allow the charge to be buffered for a short time. Therefore, an external solution is unavoidable for buffering the supply voltage for longer times. In general, three different technologies as an external energy storage exist that are suitable for energy autonomous systems: (super)capacitors, rechargeable batteries, or primary batteries. The systems developed in this thesis receive energy wirelessly. Since primary batteries cannot be recharged, they are not suitable for the task of momentary energy storage and are therefore not further discussed here. Supercapacitors are a form of capacitors with a higher energy density compared to a ceramic or electrolytic capacitor. However, supercapacitors have a higher Equivalent Series Resistance (ESR) and subsequently a lower maximum charge and discharge rate, which is not a significant problem in this application since our overall currents are small [25]. The self-discharge rate is typically around 1.8% per day, making a supercapacitor realistically suitable for storing energy for about one month [26]. The energy density is low, with only up to  $10 \text{ W h L}^{-1}$ , compared to a modern lithium-ion battery cell with up to  $100 \,\mathrm{Wh\,L^{-1}}$  for small-sized cells [27, 28]. Additionally, lithium-ion batteries have a lower self-discharge rate of about 4% per month. In terms of cycle life, a supercapacitor can reach more than 50000 cycles, whereas a lithium-ion battery can survive up to 5000 cycles [25].

In summary, there exist two different energy storage technologies that are suitable for energy autonomous systems. A capacitor may be sufficient for systems with only short operation times. For higher operation times in the range of days, higher cycle lifetime, or broader temperature range a supercapacitor is preferred. For systems that need to operate without an external power transmission for longer than a month, rechargeable batteries feature a higher energy density or a more compact solution.

#### 2.2.3. Communication

To establish a communication with the SoC, a receiver and transmitter are required. Additionally, a clock source for transmitting data is necessary.

#### Receiver

A receiver decodes the data from the wireless transmission path. In many applications, the data rate to the SoC has a low priority since only simple commands are sent to the system. The energy consumption and chip area on the other hand play a major role, making an easy decodable modulation like **On-Off Keying** (OOK) preferable.

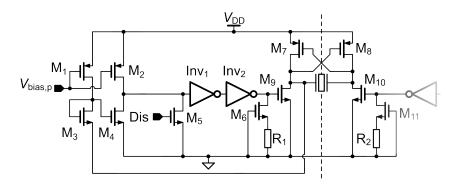

#### Transmitter

The transmitter handles the encoding and physical output to the antenna to send data over the transmission path. In general, two different transmission schemes are possible: Either an active or a passive transmission scheme. The active transmission possesses a power amplifier and actively transmits bursts of power to the antenna containing the data payload. If power requirements do not permit the active scheme, a passive data transmission can manipulate the incoming waveform

and change the reflected signal. This is called backscatter communication. While this requires less energy than an active transmission, the achievable data rate and range usually decrease compared to an active transmission. Also, the active external transducer has to detect changes in the reflectivity to decode the returned data.

#### Oscillator

The oscillator provides a constant frequency to the receiver, transmitter, and digital core. It typically operates with a frequency below 10 MHz to minimize system power consumption due to switching losses. LC oscillators and ring oscillators typically operate in much higher frequencies while the LC oscillator requires an additional on-chip inductor. Crystal oscillators always need a large external crystal and thus are unsuitable for energy autonomous systems. For frequencies below 10 MHz, relaxation oscillators are a common choice because of their low power consumption [29]. The frequency can be made adjustable by tuning the input current of the relaxation oscillator, making it especially useful for generating a signal for a Frequency Modulation (FM) transmitter.

#### 2.2.4. Digital Processing

The digital processing block controls the entire SoC, including receiving and transmitting data, evaluating sensor data, and handling the power management circuit. Additional analog blocks for generating a power-on reset and an optional memory are possible.

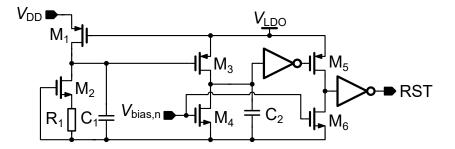

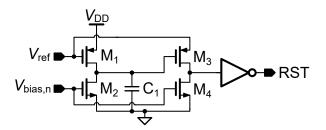

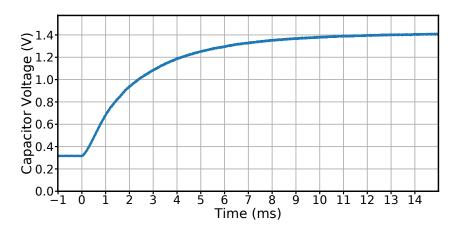

#### **Power-on Reset**

At the start-up of the SoC, the digital core needs a proper power-on reset. Different kinds of reset systems have to be implemented, depending on the power source and application. For the ultrasonic-powered systems presented in this thesis, a classical voltage-sensitive circuit detects a rising supply voltage and releases a reset signal after an additional delay. A voltage-sensitive power-on reset is not sufficient for light-powered systems because of the voltage-current characteristic of solar cells. Here, a resistive load checks if enough power is present. If that is the case, the power-on reset releases the circuit.

#### **Digital Core**

All implemented digital cores in this thesis are synthesized from Verilog code. A place and route tool transfers the synthesized netlist to a layout integrated into the SoC. They incorporate multiple state machines to fulfill the individual tasks. The clock frequency is as low as possible, in this thesis below 500 kHz, to save as much power as possible. Besides controlling the receive and transmit process of the SoC, the digital core has an external interface for debugging or to connect an external microcontroller for further functionality. This microcontroller can use the SoC as a power source and data transceiver. If the application requires a high amount of memory, an additional memory interface for external memory can be integrated.

#### Memory

Depending on the application, the digital core needs external or internal memory. In general, two types of integrated memory exist: Volatile memory like Static Random-Access Memory (SRAM) or Dynamic Random Access Memory (DRAM), which loses its information without power, and Non-Volatile Memory (NVM), which can retain its data without a power source. Since electrical power is usually not constantly available in energy autonomous systems, this section focuses on NVMs. NVMs are divided into two kinds of memories: One-Time-Programmable (OTP) memory, which can programmed only once, or an Multiple-Time-Programmable (MTP) memory, which allows multiple program cycles [30, 31]. Electrically Erasable Programmable Read-Only Memory (EEPROM) and flash memory belong to the MTP category and are available in many technologies. By depositing a charge on a floating gate, the threshold voltage of a MOSFET changes, and thus the stored information persists. The stored information can be deleted by removing the charge trapped on the floating gate. In contrast to an MTP memory, an OTP memory stores the information by changing a device permanently, typically by a controlled destruction of a specific device for writing data. The information is then readable an infinite number of times from the device. As storing elements, Zener diodes, metal traces, and gate oxides are possible. Unfortunately, burning Zener diodes or metal tracks is an energy-intensive task that typically involves currents in the milliampere range. These high currents are not available in wireless-powered ASICs and are therefore unsuitable for this type of system. Implementing an EEPROM or destroying gate oxides for the creation of an OTP on the other hand, requires only currents in the range of microamperes. Unfortunately, storing charge on an EEPROM cell or destroying gate oxides requires a high voltage ranging from 5 V to 15 V for typical process technologies. If this voltage is not available in the system, a charge pump is required to generate the high voltages.

Part II.

# **Solar and Ultrasonic Power Transmission**

## 3. Introduction to Solar Power Transmission

In 1839, A. E. Becquerel discovered the photovoltaic effect by illuminating a junction between an electrode and an electrolyte [32]. In 1905, A. Einstein proposed the idea of photons, which distribute the energy of light discontinuous in space instead of a continuous energy distribution, explaining Becquerel observations [33]. 35 years later, in 1940, R. Ohl demonstrated the first p-n junction, which generated a substantial voltage with the photovoltaic effect, leading to the first solar cell [34]. Only nine years later, in 1949, W. Shockley proposed a theory on p-n junctions, enabling the development of the bipolar transistor and subsequently many modern semiconductor devices [35, 36]. Today, solar cells are widely used as a source of renewable energies and are the primary means to directly convert sunlight to electricity. Photodiodes are based on the same working principle but are optimized for sensor applications to detect light. Therefore they are widely used in optical communication systems.

#

## **3.1. Photoelectric Effect**

Figure 3.1.: Sectional view of a solar cell. A photon with sufficient energy (E=hf) excites a carrier, generating a photocurrent.

The photoelectric effect can be divided into two different effects: The external and the internal photoelectric effect. The external photoelectric effect describes the emission of electrons from a metal surface caused by the irradiation with Ultraviolet (UV) light. The internal photoelectric effect, present in semiconductors, describes the generation of electron-hole pairs from photons. This effect can also occur for photons with a wavelength longer than UV light. Therefore, it is suitable for electrical energy generation from the sun. Figure 3.1 shows a sectional view of a basic solar cell or photodiode. It consists of a n- and p-doped semiconductor. When a photon excites an atom within a depletion region of a semiconductor, an electron will drift to the n-doped area, while the remaining hole drifts to the p-doped area. Since an electron is negatively charged and an atom missing an electron (the hole) is positively charged, the transfer of charges is considered a current. In this case, the generated current is called photocurrent. It is proportional to the incident illumination in a wide operating range. The ratio of incident light photons to generated electron-hole pairs is called the quantum efficiency. It depends on the device's dimensions, the doping concentration, how much light enters the semiconductor, the light wavelength, and many other parameters. Solar cells and photodiodes are basically from the same construction type, whereas solar cells are optimized for high energy conversion efficiency at a broad solar spectrum while photodiodes are designed for high quantum efficiency and low capacitance for high response speeds. The wavelength and the material determine how deep light penetrates the solar cell. Silicon as a typical semiconductor, has a light penetration depth of  $1 \,\mu m$  to  $10 \,\mu m$  in the visible light range from about  $400 \,\mathrm{nm}$  to  $780 \,\mathrm{nm}$  [37]. To excite an electron, the depletion region must be in the same depth as the light penetration depth to contribute to the photocurrent.

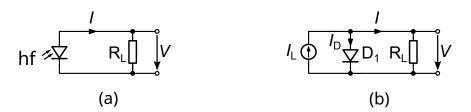

### 3.2. Simulation Model and Equivalent Circuit of a Solar Cell

For developing integrated solar cells, a working simulation model for a solar cell in a circuit is required, and thus an equivalent circuit. Figure 3.2(a) shows a solar cell with a connected load resistance  $R_L$ . Figure 3.2(b) substitutes the solar cell with an equivalent circuit, consisting of the ideal current source  $I_L$  in parallel with an ideal diode  $D_1$ . The current  $I_L$  derives from the excitation of electron-hole pairs, while the current  $I_D$  derives from the Shockley diode equation.

Figure 3.2.: Equivalent circuit for solar cells. Figure (a) shows a solar cell with a connected load resistance, and Figure (b) an equivalent circuit consisting of an ideal current source and a diode substituting the solar cell.

$I_L$  can be calculated using

$$I_L(E_g) = Ae \int_{hf=E_g}^{\infty} \frac{d\Phi}{dhf} d(hf)$$

(3.1)

where A is the area of the solar cell, e the elementary charge, h the Planck constant, f the frequency of the photon,  $E_g$  the bandgap of the semiconductor, and  $\Phi$  the photon flux density [37]. This simplified equation neglects the quantum efficiency of a real solar cell. The integral counts every photon with an energy higher than the bandgap of the semiconductor and adds one electron to the output current  $I_L$ .

The current through diode  $D_1$  can be described by the Shockley diode equation [35]. By using Kirchhoff's law, the output current over the solar cell voltage can be expressed as follows [38]:

$$I = I_L - I_s \left( exp^{\left(\frac{eV}{kT}\right)} - 1 \right)$$

(3.2)

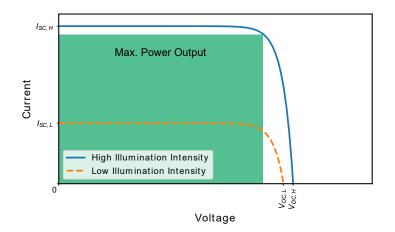

where  $I_s$  is the reverse-bias saturation current, k the Boltzmann constant, T the absolute temperature of the p-n junction, and V the voltage over the diode. With this equation, a characteristic load line can be simulated. Figure 3.3 shows the simulated load line for two different light intensities. The maximum power point is shown in green for the high illumination intensity. This point represents the maximal power output from the solar cell when the product of cell voltage and cell current reaches its maximum. It changes with the temperature and light intensity of the solar cell. Therefore, in solar power plants, an Maximum Power Point Tracking (MPPT) algorithm changes the load to reach the maximum power output.  $I_{SC}$  marks the short circuit current, and  $V_{OC}$ the open circuit voltage of a solar cell, which is typically around 0.6 V to 0.7 V for silicon-based cells.

Figure 3.3.: Load line of a typical solar cell. It shows the current generated for two different light intensities and the maximum power point in green.

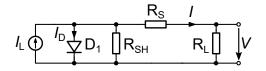

By adding a shunt resistor in parallel to the diode and a series resistor to the output in the equivalent circuit, more parasitic effects of a solar cell are modeled. Figure 3.4 shows the two

additional resistors. The parallel shunt resistor  $R_{SH}$  models defects in the crystal, non-ideal doping profiles, and other material defects that can lead to increased leakage currents in the p-n junction. Usually, this resistance is relatively high compared to the series resistance. The series resistance  $R_s$  models the resistance of the semiconductor material and contact resistances [39].

Figure 3.4.: Equivalent circuit for solar cells including a parallel and serial resistance for modeling parasitic effects.

Equation 3.2 can be extended with a parallel and series resistor to account for the additional parasitic effects, which results in the following equation:

$$I = I_L - \left(\frac{V + IR_S}{R_{SH}}\right) - I_s \left(exp^{\left(\frac{q(V+IR_S)}{kT}\right)} - 1\right)$$

(3.3)

#### 3.3. Solar Cells for Integrated Circuits

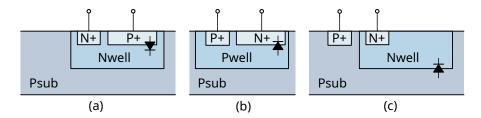

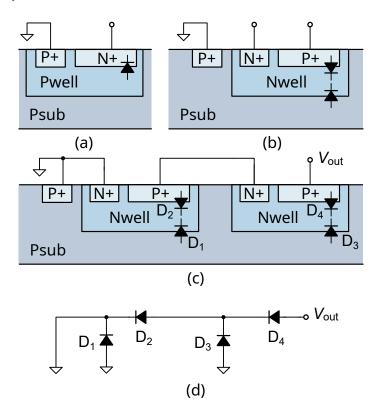

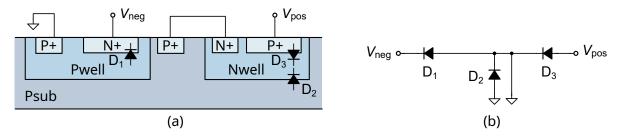

Normal solar cells are manufactured in a specially created process, solely optimized for the highest power conversion efficiency and longevity of the produced solar cells. A typical CMOS process is optimized for the best transistor properties or the smallest gate length and not for solar cells. Therefore, the options for implementing solar cells are limited in a CMOS process. Figure 3.5 shows three different solar cell structures implementable in most CMOS processes. The typical light penetration depth for visible light is around 2 µm and every solar cell structure has a different p-n junction depth. The junction depth should be near the light penetration for a good-performing solar cell. Among other parameters like doping concentration and doping profile, the junction depth gives every solar cell a unique quantum efficiency. The resulting efficiency can only be measured on a fabricated ASIC since the exact manufacturing parameters are usually classified by the manufacturing fab and are unknown to an IC designer.

Figure 3.5.: Available solar cells in CMOS technologies: (a) Nwell/P+, (b) N+/Pwell, (c) Nwell/Psub.

## 4. Introduction to Ultrasonic Power Transmission

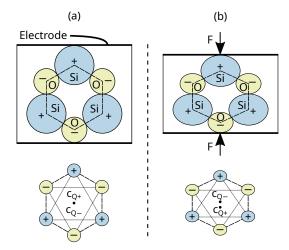

The discovery of the piezoelectric effect dates back to 1880 when Jacques and Pierre Curie discovered that a mechanical deformation of tourmaline can cause the formation of an electrical voltage [40]. Since then, piezoelectric crystals have been used in a variety of applications such as crystal oscillators, ultrasound transducers, and sensors [41, 42, 43]. Figure 4.1 shows the simplified inner structure of a piezoelectric crystal lattice consisting of silicon and oxygen atoms. Since oxygen is more strongly electronegative than silicon, oxygen can be viewed as weakly negatively ionized while silicon is weakly positively ionized. A conductive coating on the top and bottom of the piezoelectric crystal provides a contact electrode. In Figure 4.1(a), the crystal is without any external loads, whereas a mechanical force compresses the crystal in Figure 4.1(b). Compressing the crystal with an external force shifts the positive charges  $C_{Q+}$  of the silicon atom, as well as the negative charges  $C_{Q-}$  of the oxygen atom. Where in 4.1(a), the charges  $C_{Q+}$  and  $C_{Q-}$  are congruent, in 4.1(b), the charges  $C_{Q+}$  and  $C_{Q-}$  are separated from each other, and an electrical voltage is measurable on the electrodes due to the charge displacements. A piezoelectric crystal can convert an electrical input to a mechanical output and vice versa. Conversion from the mechanical to the electrical domain is named the direct piezoelectric effect, while the conversion from the electrical to the mechanical domain is referred to as the inverse piezoelectric effect [44].

Figure 4.1.: Inner structure of a piezoelectric crystal consisting of silicon and oxygen. The left side (a) shows the crystal with no external mechanical force applied, while on the right side (b) a mechanical force is applied at the electrical contacts [44].

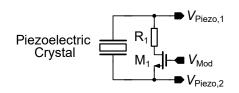

## 4.1. Equivalent Circuit

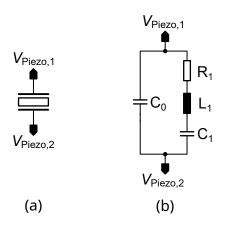

To model the behavior of a piezoelectric crystal in an electrical circuit, an equivalent circuit is required. In 1928, K. S. Van Dyke proposed the equivalent circuit shown in Figure 4.2. It consists of only four circuit elements, a parallel capacitor  $C_0$  and a damped series resonant circuit  $R_1L_1C_1$  [45]. Therefore, it only models the first and second resonance of a piezoelectric crystal, namely the series resonance of the series  $R_1L_1C_1$  branch and a parallel resonance consisting of  $C_0$  and  $R_1L_1C_1$ .

Figure 4.2.: Electrical equivalent circuit for a piezoelectric crystal.

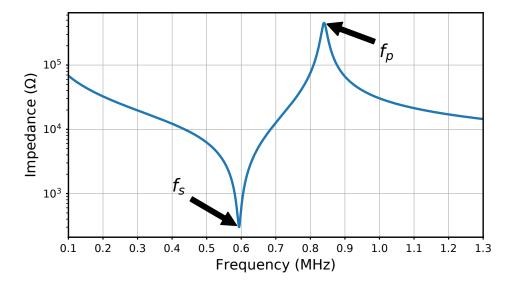

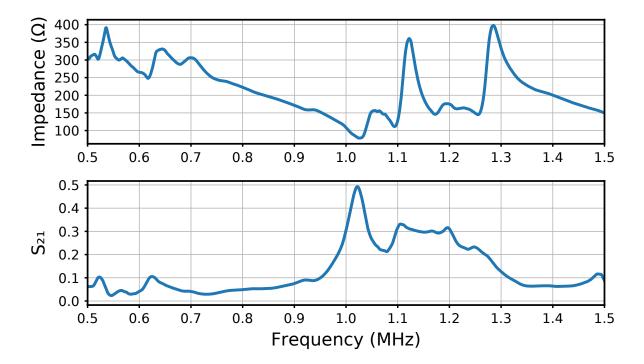

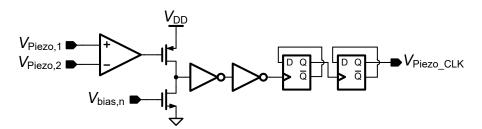

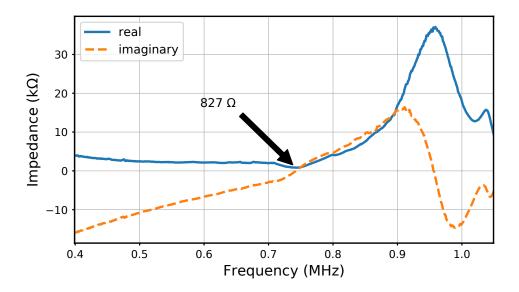

A typical piezoelectric crystal impedance curve is shown in Figure 4.3. The basis is the Van Dyke equivalent circuit and it shows a series resonance  $f_s$  at about 600 kHz and a parallel resonance  $f_p$  at 840 kHz. Resonances of higher orders are possible to model, by adding additional *RLC* resonance circuits in parallel to the existing circuit. The series resonance frequency enables a high power transmission with a piezoelectric crystal at low driving voltages due to the minimum impedance of the piezoelectric crystal at that frequency. Whereas the parallel resonance frequency has a maximum impedance at that frequency, making it ideal for receiving weak signals with a high voltage output.

## 4.2. Calculation of the Resonance Frequencies

The resonance frequency of a piezoelectric crystal is the preferred frequency for energy and data transmission. For a piezoelectric crystal disc in thickness extensional mode, where the diameter is d is at least ten times higher than the thickness of the piezoelectric crystal disc  $\tau_x$ , it can be assumed that the resonance frequency is proportional to its thickness [44]. With the following equation, the resonance frequency  $f_r$  of a piezoelectric crystal disc can be calculated to

$$f_r = \frac{N_r}{\tau_x} \tag{4.1}$$

Figure 4.3.: Plot of a piezoelectric crystal impedance based on the Van Dyke equivalent circuit.

with  $N_r$  being the frequency constant of the piezoelectric crystal material in Hz m. For the PZT-5A piezoelectric material,  $N_r$  ranges from 1900 Hz m to 2100 Hz m, depending on the exact material type and manufacturer [46]. For piezoelectric crystals, where the diameter *d* is less than ten times the thickness  $\tau_x$ , the assumption that the resonance frequency is proportional to its thickness is not valid anymore. For small systems where the piezoelectric crystal limits the miniaturization of the system, a cubical piezoelectric crystal is an often used geometry. R. Holland describes a model for the calculation of the resonance frequency for cubical piezoelectric crystals [47]. With the following approximation, the size of the cubical piezoelectric crystal can be calculated for a given resonance frequency:

$$\tau_x = \frac{\Omega^v}{2 \cdot f_p^v} \cdot \sqrt{\frac{c_{3333}^E}{\rho}}$$

(4.2)

$\tau_x$  now represents the edge length of the piezoelectric crystal cube,  $\Omega^v$  the dimensionless eigenfrequency dependent on the oscillation mode,  $f_p^v$  the parallel resonance frequency,  $c_{3333}^E$  the electroelastic coefficient and  $\rho$  the material density of the PZT-5A crystal. v describes different oscillation modes of the piezoelectric crystal. Mode 1 is the correct mode for a parallel resonance and results in 0.629 for  $\Omega^{(1)}$ . With the electroelastic coefficient  $c_{3333}^E$  of  $11.1 \times 10^{10}$  N m<sup>-2</sup> and the density of PZT-5A of 7550 kg m<sup>-3</sup> inserted into Equation 4.2, the edge length of the piezoelectric crystal can be calculated to

$$\tau_x = \frac{0.824}{2 \cdot f_p^{(1)}} \cdot \sqrt{\frac{11.1 \times 10^{10} \,\mathrm{N \,m^{-2}}}{7550 \,\mathrm{kg \,m^{-3}}}} = \frac{1579.74 \,\mathrm{m \, s^{-1}}}{f_p^{(1)}}.$$

(4.3)

The equation demonstrates that the resulting edge length  $\tau_x$  of the piezoelectric crystal cube is inversely proportional to the resonance frequency  $f_p^{(1)}$ .

## 4.3. Measuring Piezoelectric Crystal Parameters

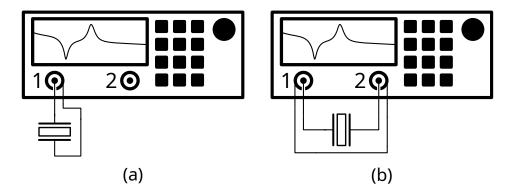

A 50  $\Omega$  matched Vector Network Analyzer (VNA) is used to measure the resonance frequencies of a piezoelectric crystal. Figure 4.4(a) shows the reflection technique which is especially suitable for small impedances around 50  $\Omega$ , while the series-through technique is preferred for impedances over 50  $\Omega$ , as shown in Figure 4.4(b) [48]. Both techniques require different wiring of the piezoelectric crystal and a different calculation of the resulting impedance since a VNA only calculates the Scattering-parameter (S-parameter).

Figure 4.4.: Set up for measuring the impedance of a piezoelectric crystal with a VNA. (a) shows the reflection technique for low-impedance piezoelectric crystals while (b) shows the series-through method for high-impedance piezoelectric crystals.

For measuring the impedance with the reflection technique, the piezoelectric crystal is connected as shown in Figure 4.4(a), and the  $S_{11}$  parameter is measured. The result can then be converted to the piezoelectric crystal impedance  $Z_{Piezo,Reflection}$  using

$$Z_{Piezo,Reflection} = 50\,\Omega \cdot \frac{1+S_{11}}{1-S_{11}}.$$

(4.4)

For calculating the resulting impedance of the piezoelectric crystal with the series-through technique, the piezoelectric crystal is connected as shown in Figure 4.4(b). By measuring the  $S_{21}$  parameter,  $Z_{Piezo,Series-through}$  calculates to [49]

$$Z_{Piezo,Series-through} = 100 \,\Omega \cdot \frac{1 - S_{21}}{S_{21}}.\tag{4.5}$$

# Part III.

# Implemented and Fabricated Autonomous System-on-Chips with Wireless Energy and Data Transmission

## 5. Ultrasonic Powered ASIC for Sensor Integrated Machine Elements

Figure 5.1.: (a) 3D rendering of the sensor integrated bolt [95], (b) Sectional view of the bolts' head with attached ultrasonic transducer.

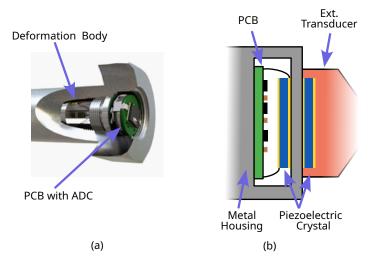

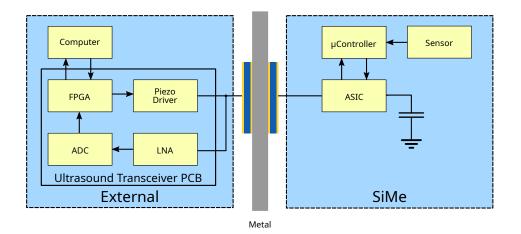

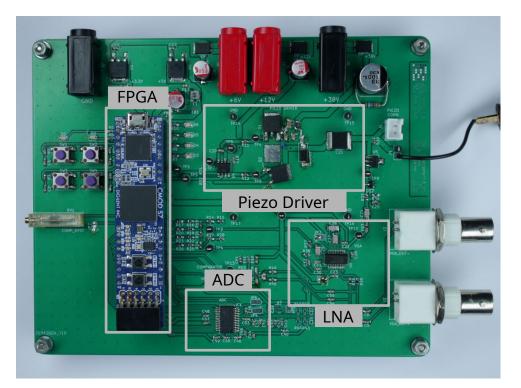

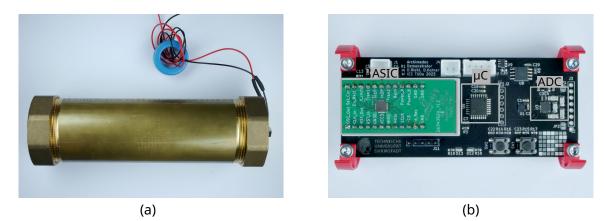

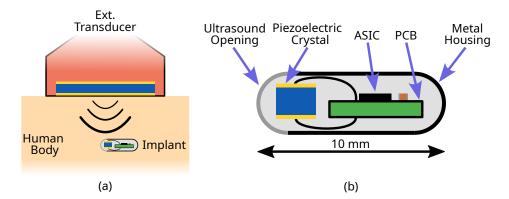

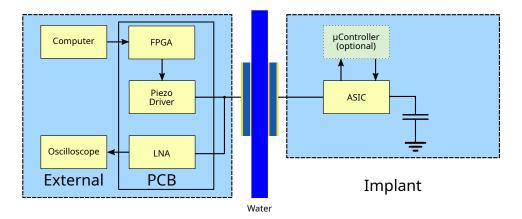

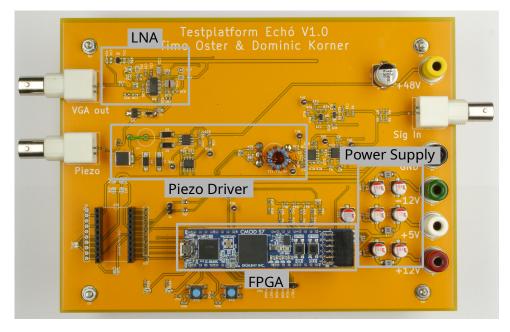

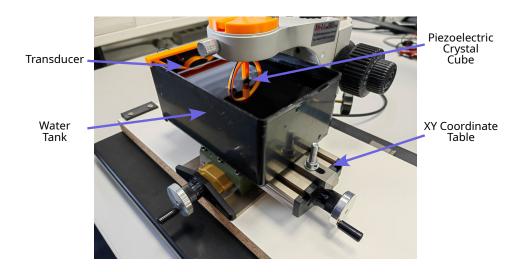

Forecasting the remaining lifetime of critical machine elements can prevent production downtimes and reduce operating costs. By monitoring individual parts of the machine, the maintenance schedule can be extended, while detecting imminent failures in advance. The monitoring of individual devices can be achieved by a SiMe, embedded directly in the machine element [50, 51]. Usually, a commercially available sensor element is attached to the machine, while an external Analog-to-Digital Converter (ADC) reads out the analog signal. An external sensor and evaluation circuit requires a modification of the machine element, a solution with a standardized component is preferred. An example of this can be a standardized bolt developed by Herbst et al. [9]. The developed bolt has an internal multi-axis force sensor for measuring the bolting torque. Three strain gauges are glued on a deformation body inside a cavity in the bolt. The cavity weakens the strength of the bolt by approximately one strength class. The cavity has a size of  $12 \text{ mm} \times 20 \text{ mm}$  for the force sensor and  $16.4 \text{ mm} \times 6.4 \text{ mm}$  reserved for the electronics [95]. The cavity's cap closes with a metal sheet, forming a Faraday cage. Since the strain gauge's ADC must measure voltage differences in the range of microvolts, the cavity provides an ideal low-noise environment. Additionally, the metal closed cavity makes the bolt resistant to chemicals or environmental influences. Figure 5.1(a) shows a rendering of the sensor integrated bolt with the integrated strain gauge and the electronic, protected by the closed metal housing. Since the screw is completely encapsulated by metal, wireless energy and data transfer is hardly possible with an RF transmission. Instead, ultrasonic communication and energy transfer are suitable to penetrate the metal housing [53, 54]. Figure 5.1(b) shows a sectional view of the bolt's head. It has an external removable ultrasonic transducer on the outer side and an internal piezoelectric crystal as a receiver. An ASIC for the energy transfer and communication keeps the internal electronic as small as possible.

The focus of this chapter is on the development of the ASIC and on ultrasonic energy and data transmission. The first section covers an ultrasonic bidirectional communication protocol. In the following sections, the ASIC implementation is shown, followed by measurement results and a brief summary. This project is motivated by the DFG priority program 2305 [55], in which different energy harvesting and communication systems for machine elements are evaluated.

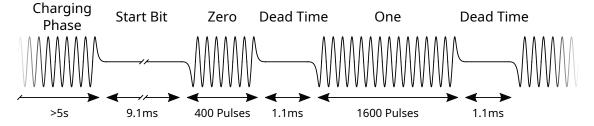

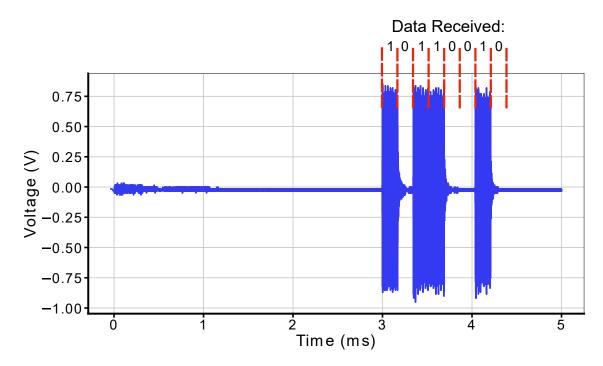

### 5.1. Bidirectional Ultrasonic Communication

The sensor-integrated bolt measures the tightening torque and bending of the bolt and saves it to the internal memory. Additional sensors like temperature and acceleration can be used to detect vibration in the machine. All recorded data are transmitted to the external transducer via ultrasound. The energy required for the transmission and the measurements must first transmitted to the bolt. Therefore, a bidirectional communication for sending commands to the ASIC and receiving the recorded data with an energy transfer is necessary.

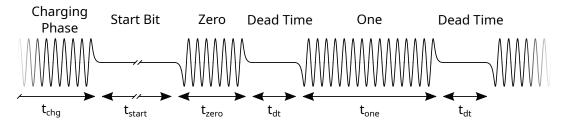

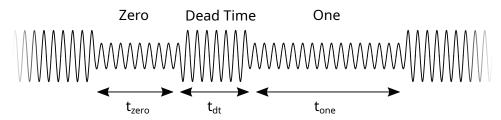

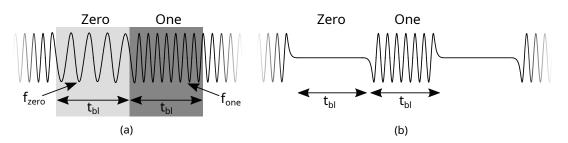

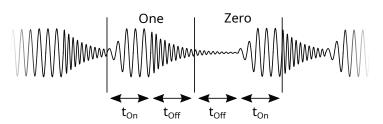

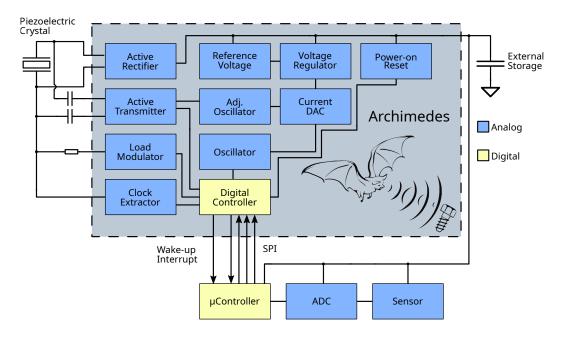

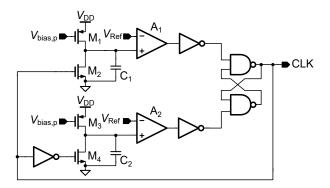

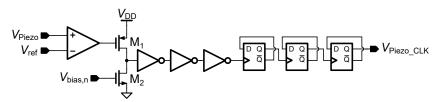

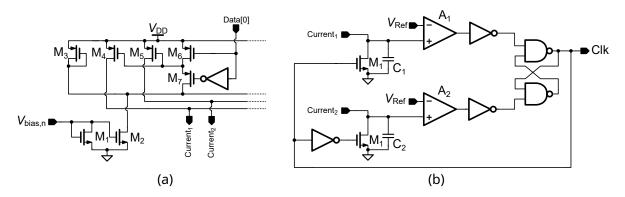

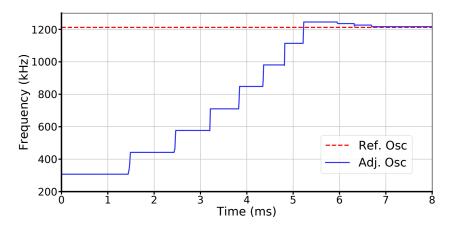

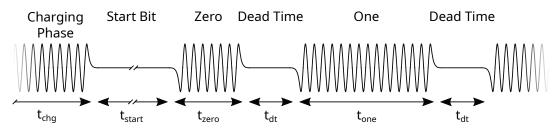

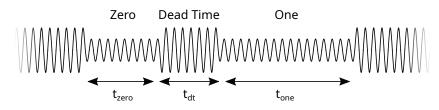

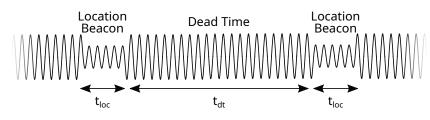

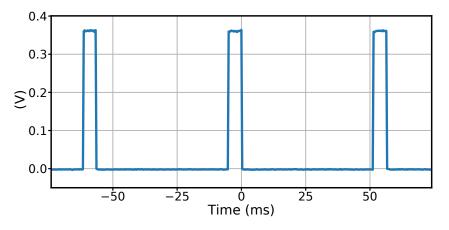

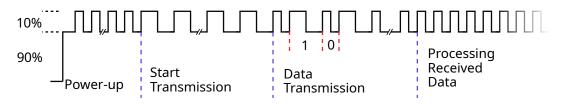

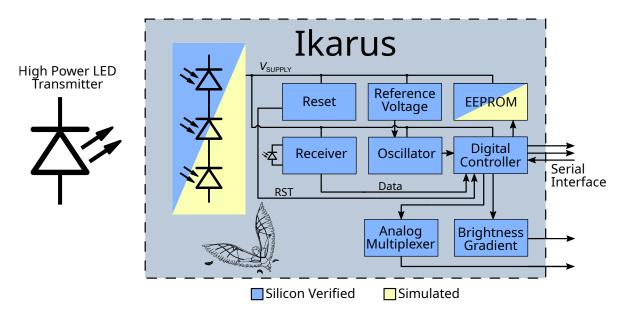

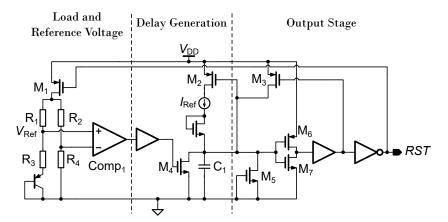

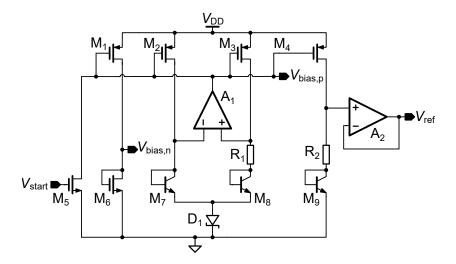

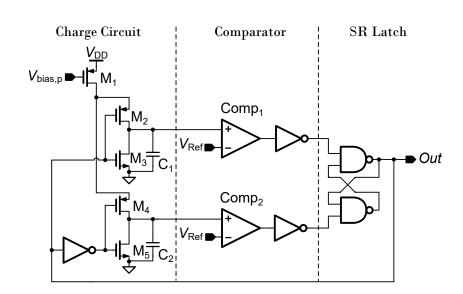

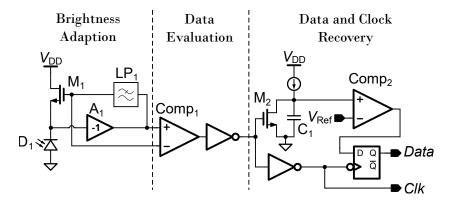

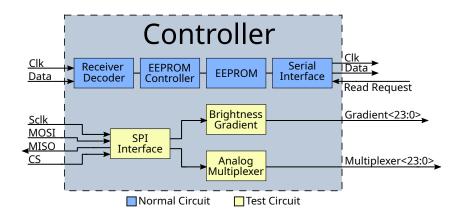

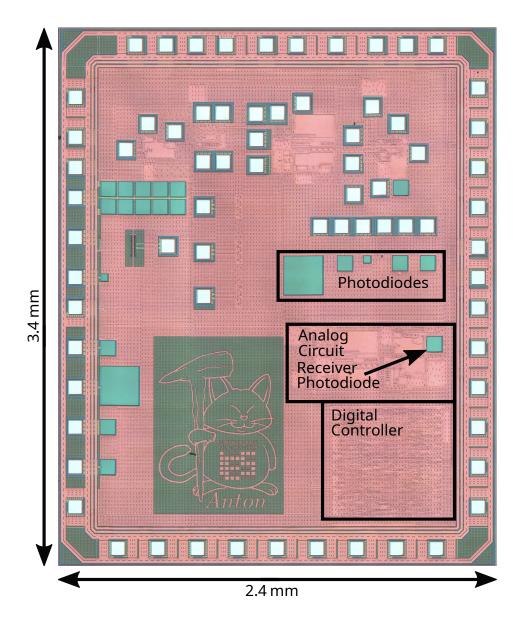

#### 5.1.1. Receive Protocol