#### Data Driven Compact Modeling of a Reconfigurable FET

#### DISSERTATION

Vom Fachbereich Elektro- und Informationstechnik der Technischen Universität Darmstadt

zur Erlangung des akademischen Grades eines Doktors der Ingenieurwissenschaften (Dr.-Ing.)

genehmigte Dissertation

von

#### Maximilian Jürgen Reuter

Erstgutachter: Zweitgutachter: Prof. Dr.-Ing. Klaus Hofmann Prof. Dr.-Ing. Dr. h. c. Jürgen Becker

Tag der Einreichung:2Tag der mündlichen Prüfung:2

25.06.2024 28.10.2024

Darmstadt 2024

Maximilian Jürgen Reuter: Data Driven Compact Modeling of a Reconfigurable FET

Darmstadt, Technische Universität Darmstadt Jahr der Veröffentlichung auf TUprints: 2024 URN: urn:nbn:de:tuda-tuprints-286299 Tag der mündlichen Prüfung: 28.10.2024

Veröffentlicht unter CC BY-SA 4.0 International https://creativecommons.org/licenses/

"Essentially, all models are wrong, but some are useful." — George Box & Norman Draper [1]

#### Abstract

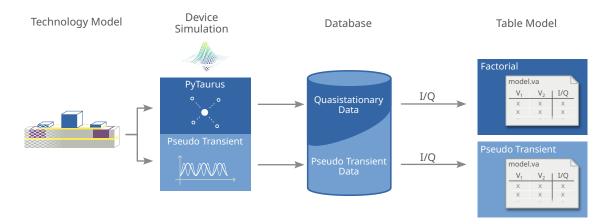

This work contributes to predictive circuit simulation of emerging semiconductor devices by proposing two approaches to obtain characteristic device data from technology simulation, resulting in table models. From these intermediate table models, two different machine learning approaches provide candidates of machine learning based compact models. The methods are demonstrated for an ambipolar transistor, called the *planar RFET*, which allows dynamic reconfiguration of channel polarity at runtime through an additional gate electrode. As a first approach, a cluster simulation tool *PyTaurus* is proposed and allows efficient setup, simulation and refinement of table models from a factorial setup of DC parameter sweeps. To reduce model building time, PyTaurus provides a cluster simulation functionality and distributes the simulation deck to available computation nodes. A second approach, *pseudo transient simulation*, covers the bias space of the device under test within a single slowly proceeding transient simulation. Nesting of input voltages is achieved by a systematic setup of frequencies, that drive the respective harmonic electrode voltage signals. The resulting data sets satisfy structural constraints for table models in Verilog-A.

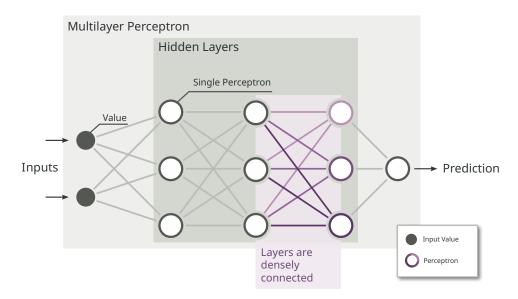

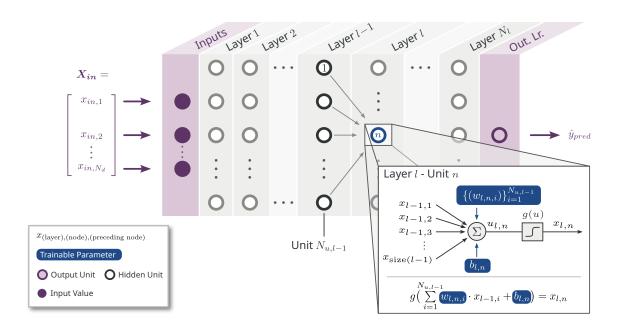

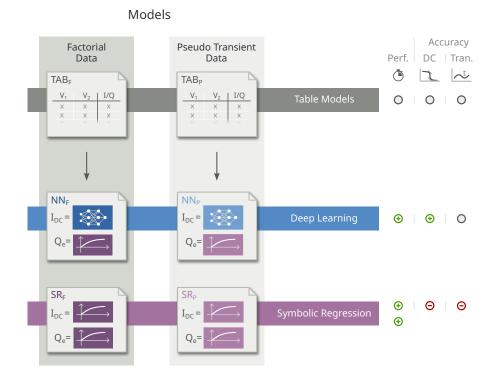

Beyond the use as plain table models, however, the obtained data sets are transformed to predictive compact models using machine learning. The high dynamic range, that the drive current of the planar reconfigurable FET (RFET) features throughout the operating regions, leads to a solution with an ensemble model. A linear model focuses on high drive currents, while a second model is trained on logarithmically transformed current samples to provide accuracy into the regime of leakage current. For the respective models, two approaches are evaluated: The deep learning approach leads to multilayer perceptrons, which are then sequentially implemented in Verilog-A. The predictions are obtained through inference of the compact model voltages in each simulator step. As a second approach, symbolic regression is employed to optimize an analytical model without structural constraints. The obtained closed form expressions can directly be implemented in Verilog-A. In addition to the DC drive current model, a transient model is formed by symbolic regression, exclusively, as the dynamic range and the expected complexity of the charge model are lower than with drive current.

The resulting neural network-based models show improvement over table models when it comes to DC simulation of digital cells. Transient simulation for timing characterization leads to similar accuracy than the table models, with a maximum deviation of 5.1% from the technology CAD (TCAD) reference. Neural network-based models accelerate the simulation with a factor of up to  $17\times$ . Symbolic regression-based drive current models further improve computational efficiency, but show insufficient accuracy for predictive circuit simulation.

The concluding result of this work is that it is recommended to transform a table model into a neural network-based compact model using the proposed data driven approach, which requires minimal domain knowledge. Symbolic regression is successfully employed for modeling of electrode charges, but accurate drive current modeling requires further work.

### Zusammenfassung

Diese Arbeit trägt zur prognostischen Schaltungssimulation von neuartigen Halbleiterbauelementen bei, indem zwei Ansätze für das Erstellen von charakteristischen Datensätzen aus Technologiesimulation gezeigt werden, die in Tabellenmodellen resultieren. Basierend auf diesen vorläufigen Tabellenmodellen erzeugen zwei unterschiedliche Ansätze aus dem Bereich des maschinellen Lernens Kompaktmodellkandidaten. Die Methoden werden anhand eines ambipolaren Transistors, genannt planarer RFET, gezeigt, welcher die dynamische Rekonfiguration der Kanalpolarität zur Laufzeit mit Hilfe eines einer zusätzlichen Gate-Elektrode erlaubt. Als erster Ansatz wird ein Programm zur Verteilung Simulationsanordnungen, welches das effiziente Erstellen, Simulieren und Verbessern von Tabellenmodellsimulationen aus faktoriellen Anordnungen von DC Parameter-Sweeps. Um die Modellierungszeit zu verkürzen erlaubt es PyTaurus die Simulationen an verfügbare Netzwerkknoten zu verteilen. Ein zweiter Ansatz, die pseudotransiente Simulation, deckt den Raum der Eingangsspannungen des Bauelements innerhalb einer einzelnen langsam voranschreitenden Transientensimulation ab. Die Verschachtelung von Eingangsspannungen wird hierbei durch die systematischen Anordnungen von Frequenzen der harmonischen Eingangsspanungssignalen erreicht. Der resultierende Datensatz erfüllt die strukturellen Bedingungen für Tabellenmodelle in Verilog-A.

Uber die direkte Nutzung als Tabellenmodell hinausgehend, werden die generierten Datensätze durch Methoden des maschinellen Lernens in prognostische Kompaktmodelle überführt. Der große Dynamikumfang, den der Kanalstrom des planaren RFET in verschiedenen Arbeitsbereichen zur Verfügung stellt, führt zu einer Lösung mit einem zusammengesetzten Modell. Ein lineares Modell fokussiert sich auf hohe Kanalströme, während ein weiteres Modell auf den Daten von logarithmisch transformierten Kanalströmen trainiert wird um Genauigkeit bis in den Bereich von Leckströmen zu erhalten. Für die jeweiligen Modelle werden zwei Ansätze evaluiert: Der Deep-Learning Ansatz führt zur Struktur eines Multilayer Perceptrons, welches dann sequenziell in Verilog-A implementiert wird. Die Vorhersagen werden durch Inferenz mit den Eingangsspannungen des Kompaktmodells in jedem Simulatorschritt erzeugt. Als zweiten Ansatz wird symbolische Regression eingesetzt, welche ein analytisches Modell ohne strukturelle Eingrenzungen optimiert. Die dadurch erhaltenen Ausdrücke in geschlossener Form können direkt in Verilog-A implementiert werden. Zusätzlich zum DC Kanalstrommodell wird ein Transientenmodell ausschließlich durch symbolische Regression erzeugt, da der Dynamikumfang und die erwartete Komplexität des Ladungsmodells geringer sind als des Kanalstrommodells.

Die resultierenden auf neuronalen Netzen basierenden Modelle zeigen Verbesserungen gegenüber den Tabellenmodellen bezüglich DC Simulation von digitalen Zellen. Transientensimulation für die Charakterisierung von Zeitverhalten führt, mit einer Abweichung von der TCAD-Referenz von maximal 5.1%, zu einer ähnlichen Genauigkeit, wie sie die Tabellenmodelle zeigen. Die auf neuronalen Netzen basierenden Modelle beschleunigen außerdem die Schaltungssimulation um bis zu  $17 \times$ . Auf symbolischer Regression basierende Kanalstrommo-

delle verbessern die Effizienz der Berechnung noch weiter, bieten jedoch nicht die notwendige Genauigkeit für prognostische Schaltungssimulation.

Das zusammenfassende Ergebnis dieser Arbeit ist die Empfehlung ein Tabellenmodell in ein auf neuronalen Netzen basierendes Kompaktmodell zu überführen, indem der vorgeschlagene, auf wenig Spezialwissen basierende Ansatz verwendet wird. Symbolische Regression wird erfolgreich für Ladungsmodelle der Elektroden eingesetzt, für die präzise Modellierung von Kanalströmen ist jedoch weitere Arbeit nötig.

## Acknowledgements

My special thanks go to Klaus Hofmann, who provided me with the mixture of guidance and freedom a junior scientist can only dream of.

Jens Trommer and Johannes Pfau have my gratitude for all the positive spirit, encouragement and dedicated collaboration during our joint research projects PARFAIT I, II and SENSOTERIC.

For exceptional assistance with technology models – day and night – I thank Tillmann Krauss.

Further, I would like to thank Andreas Kramer for his thorough and valuable feedback.

My parents enabled my career in the first place, for which I am very thankful.

Thank you, Dorsa, for your loving support and all the shared excitement.

## Contents

| List of Figures xiii |                      |                                        |    |  |  |  |

|----------------------|----------------------|----------------------------------------|----|--|--|--|

| Lis                  | List of Tables xv    |                                        |    |  |  |  |

| Lis                  | List of Acronyms xvi |                                        |    |  |  |  |

| List of Symbols xix  |                      |                                        |    |  |  |  |

| 1                    | Intr                 | oduction                               | 1  |  |  |  |

|                      | 1.1                  | Research Scope and Objective           | 1  |  |  |  |

|                      | 1.2                  | Thesis Outline                         | 3  |  |  |  |

| 2                    | Fun                  | damentals and State of the Art         | 5  |  |  |  |

|                      | 2.1                  | Reconfigurable FETs                    | 5  |  |  |  |

|                      |                      | 2.1.1 RFET Fundamentals and Prototypes | 5  |  |  |  |

|                      |                      | 2.1.2 The Planar RFET                  | 9  |  |  |  |

|                      |                      |                                        | 11 |  |  |  |

|                      | 2.2                  | 6                                      | 14 |  |  |  |

|                      |                      | 0                                      | 16 |  |  |  |

|                      |                      |                                        | 21 |  |  |  |

|                      |                      | 1                                      | 27 |  |  |  |

|                      | 2.3                  |                                        | 30 |  |  |  |

|                      |                      | -                                      | 31 |  |  |  |

|                      |                      |                                        | 38 |  |  |  |

|                      |                      |                                        | 41 |  |  |  |

|                      |                      |                                        | 43 |  |  |  |

|                      |                      | -                                      | 46 |  |  |  |

| 3                    | Gen                  |                                        | 47 |  |  |  |

|                      | 3.1                  | 0                                      | 48 |  |  |  |

|                      | 3.2                  | 8                                      | 49 |  |  |  |

|                      |                      |                                        | 53 |  |  |  |

|                      |                      |                                        | 56 |  |  |  |

|                      |                      | <sup>o</sup>                           | 58 |  |  |  |

|                      | 3.3                  |                                        | 61 |  |  |  |

|                      |                      |                                        | 62 |  |  |  |

|                      |                      | 1                                      | 65 |  |  |  |

|                      |                      |                                        | 71 |  |  |  |

| 4                    | Data                 |                                        | 75 |  |  |  |

| -                    | 4.1                  | 1 0                                    | 76 |  |  |  |

|                      | 4.2                  | 1                                      | 76 |  |  |  |

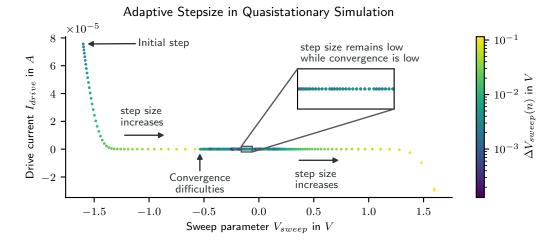

|    |                       | 4.2.1  | Sample Density of Quasistationary Sweeps                       | 78  |  |

|----|-----------------------|--------|----------------------------------------------------------------|-----|--|

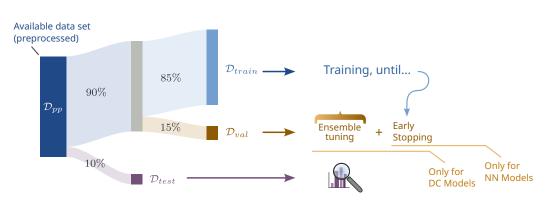

|    |                       | 4.2.2  | Splitting into Training-, Validation- and Test Set             | 79  |  |

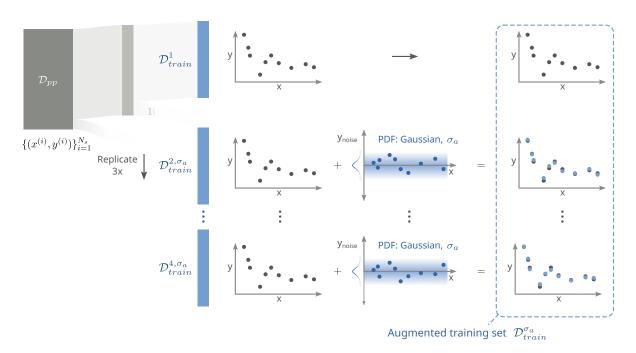

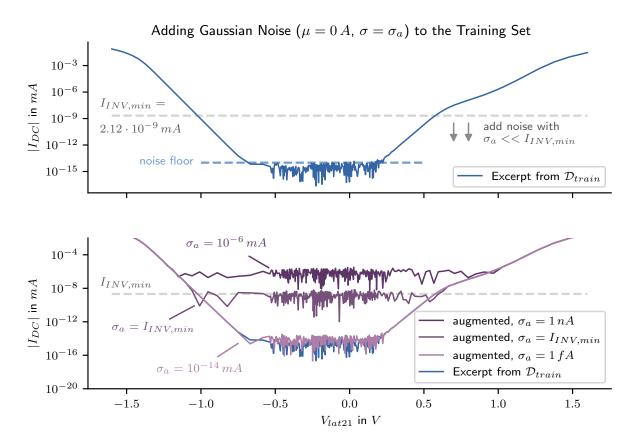

|    |                       | 4.2.3  | Data Augmentation                                              | 80  |  |

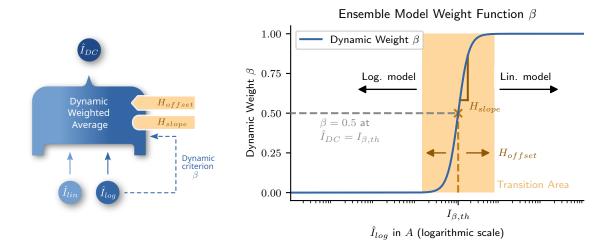

|    |                       | 4.2.4  | The Ensemble Backend                                           | 82  |  |

|    | 4.3                   | The N  | eural Network Models                                           | 84  |  |

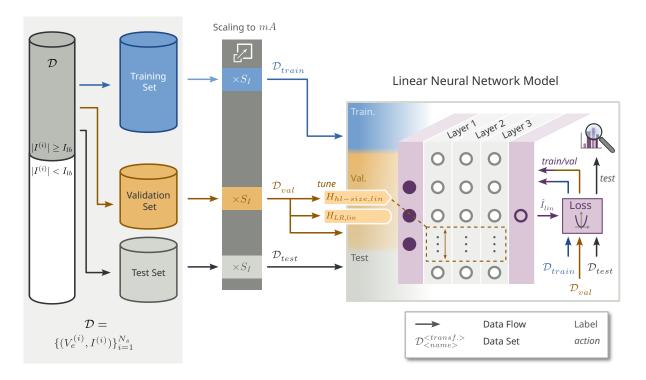

|    |                       | 4.3.1  | The Linear Neural Network Model                                | 87  |  |

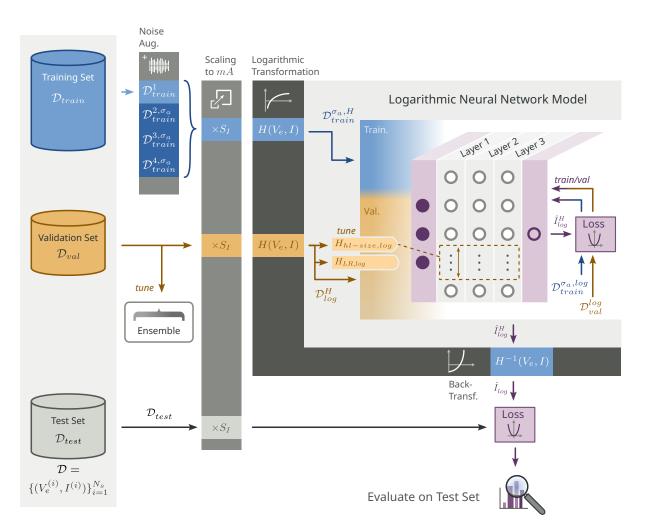

|    |                       | 4.3.2  | The Logarithmic Neural Network Model                           | 88  |  |

|    | 4.4                   | The Sy | ymbolic Regression Models                                      | 89  |  |

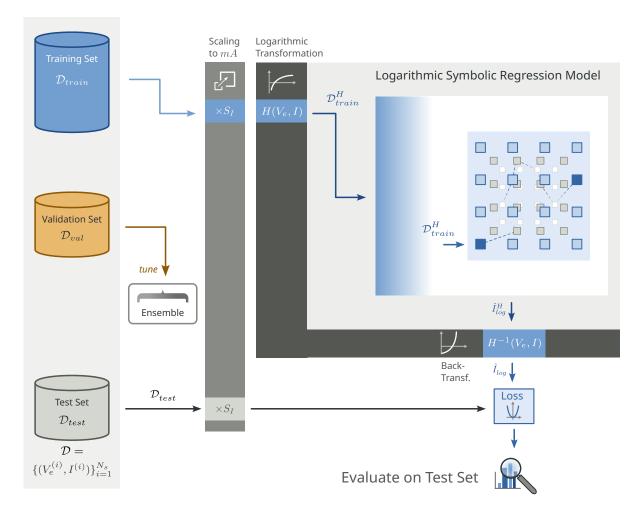

|    |                       | 4.4.1  | The Symbolic Regression-Based Logarithmic Current Model        | 90  |  |

|    |                       | 4.4.2  | Linear Current Model and Charge Model with Symbolic Regression | 91  |  |

|    | 4.5                   | Hypei  | rparameter Training                                            | 92  |  |

|    | 4.6                   | Mode   | l Deployment                                                   | 94  |  |

| 5  | Eval                  | uation |                                                                | 99  |  |

|    | 5.1                   | Evalua | ation of Table Model Approaches                                | 100 |  |

|    |                       | 5.1.1  | Generation Flow: PyTaurus                                      | 100 |  |

|    |                       | 5.1.2  | Generation Flow: Pseudo Transient Approach                     | 102 |  |

|    |                       | 5.1.3  | Circuit Level Evaluation                                       | 109 |  |

|    | 5.2                   | Evalua | ation of Compact Model Approaches                              | 112 |  |

|    |                       | 5.2.1  | Ensemble Model Hyperparameters                                 | 113 |  |

|    |                       | 5.2.2  | Structure and Accuracy of Individual Models                    | 114 |  |

|    |                       | 5.2.3  | Circuit Level Analysis                                         | 118 |  |

|    |                       | 5.2.4  | Cell Timing Analysis                                           | 122 |  |

| 6  | Sum                   | nmary, | Conclusion and Outlook                                         | 127 |  |

|    | 6.1                   | Concl  | usion                                                          | 128 |  |

|    | 6.2                   | Outlo  | ok                                                             | 129 |  |

|    |                       |        |                                                                |     |  |

|    | Bibl                  | iograp | hy                                                             | 131 |  |

| A  | App                   | endix  |                                                                | 149 |  |

|    | А.1                   | Simul  | ation Times of Timing Characterization Simulations             | 149 |  |

| Pu | Publications151       |        |                                                                |     |  |

| Su | Supervised Theses 153 |        |                                                                |     |  |

## List of Figures

| Figure 1.1  | Overview of the implementation part                                        | 2  |

|-------------|----------------------------------------------------------------------------|----|

| Figure 2.1  | Electrostatic doping by volume inversion/accumulation                      | 6  |

| Figure 2.2  | Two types of Schottky barrier RFETs                                        | 7  |

| Figure 2.3  | Overview of fabricated RFET structures                                     | 8  |

| Figure 2.4  | Structure and schematic symbol of the planar RFET                          | 10 |

| Figure 2.5  | Drive current of the planar RFET                                           | 11 |

| Figure 2.6  | Static CMOS gates implemented with RFETs                                   | 12 |

| Figure 2.7  | The 4-transistor XOR core enabled by RFETs                                 | 13 |

| Figure 2.8  | Three ways from technology model to circuit model                          | 15 |

| Figure 2.9  | TCAD data generation flow                                                  | 17 |

| Figure 2.10 | Demonstration of adaptive stepping in Sentaurus Device                     | 19 |

| Figure 2.11 | Full factorial simulation setup with parameter sweeps                      | 20 |

| Figure 2.12 |                                                                            | 23 |

| Figure 2.13 |                                                                            | 24 |

| Figure 2.14 | Linear interpolation on iso lines                                          | 29 |

| Figure 2.15 | -                                                                          | 30 |

| Figure 2.16 | -                                                                          | 31 |

| Figure 2.17 |                                                                            | 32 |

| Figure 2.18 |                                                                            | 33 |

| Figure 2.19 | The respective operation of each neural unit in the neural network         | 34 |

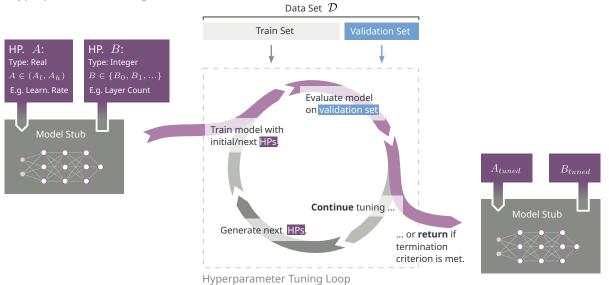

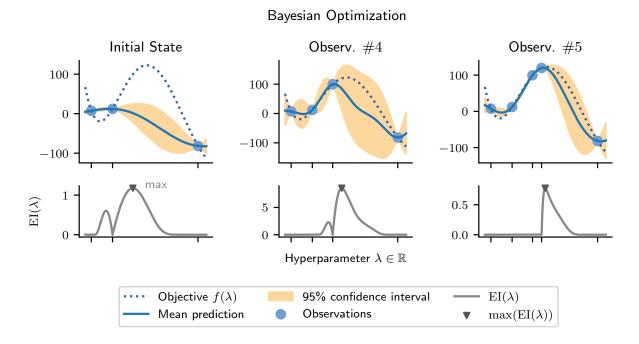

| Figure 2.20 | The hyperparameter tuning loop                                             | 35 |

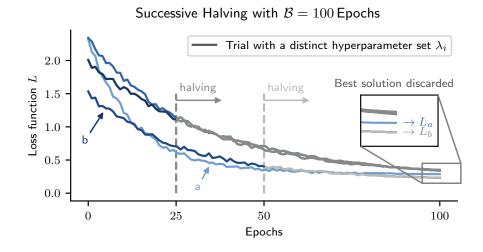

| Figure 2.21 |                                                                            | 36 |

| Figure 2.22 |                                                                            | 37 |

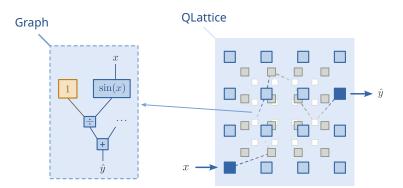

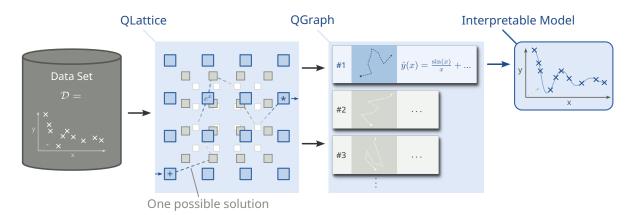

| Figure 2.23 | Symbolic regression by path optimization through a lattice of interactions | 40 |

| Figure 2.24 | QLattice produces multiple model candidates which allow interpretation     |    |

|             | of causalities and mechanisms in $\mathcal{D}$ .                           | 41 |

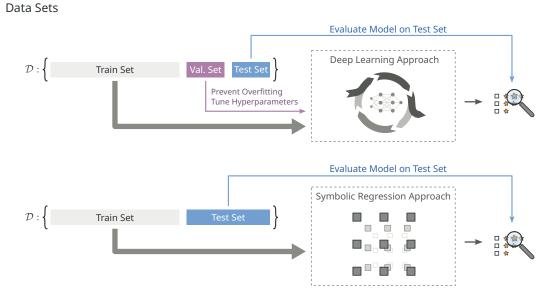

| Figure 2.25 | 3-Split for deep learning and 2-split for symbolic regression              | 44 |

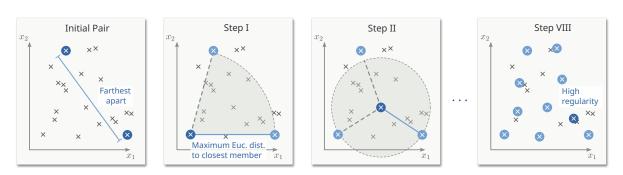

| Figure 2.26 | The Kennard-Stone splitting algorithm                                      | 45 |

| Figure 3.1  |                                                                            | 47 |

| Figure 3.2  | Generating device data in detail                                           | 48 |

| Figure 3.3  | RFETs models required characterization over a wider input range than       |    |

|             | CMOS models.                                                               | 49 |

| Figure 3.4  | PyTaurus simulation cluster overview                                       | 50 |

| Figure 3.5  | Data structure of PyTaurus                                                 | 51 |

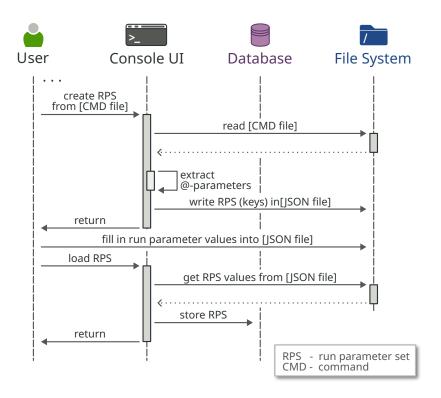

| Figure 3.6  | Sequence diagram of creating a run parameter set                           | 54 |

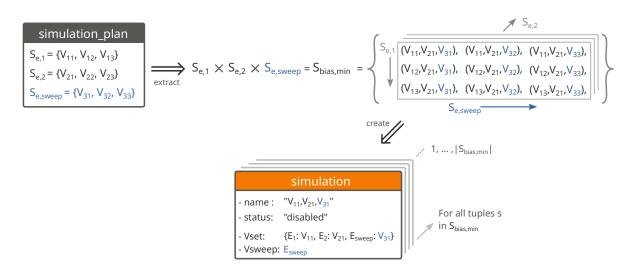

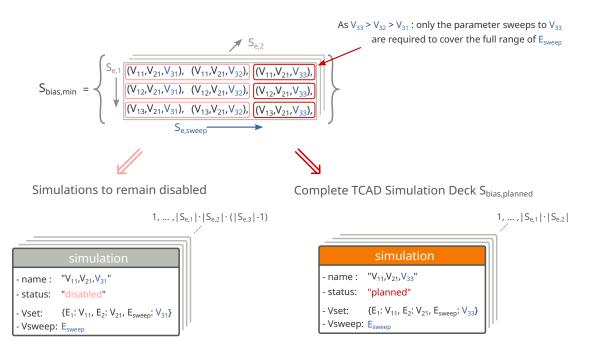

| Figure 3.7  | Setup of simulation documents in generation phase                          | 55 |

| Figure 3.8  | Distinguishing between required simulations and disabled simulations       | 56 |

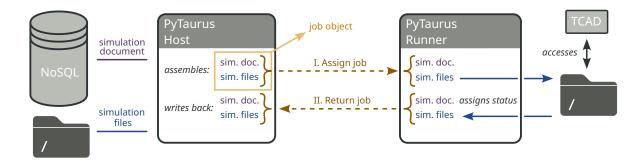

| Figure 3.9  | Data flow diagram of a PyTaurus simulation                                 | 57 |

|             |                                                                            |    |

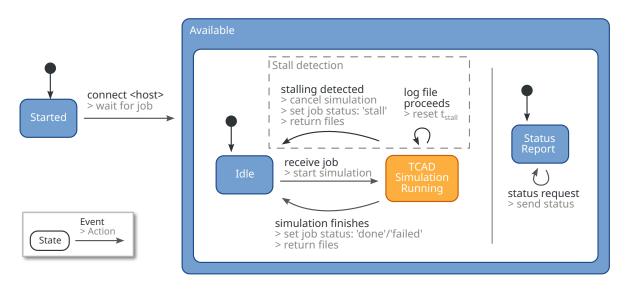

| Figure 3.10 | State diagram of the PyTaurus runner                                                         | 58 |

|-------------|----------------------------------------------------------------------------------------------|----|

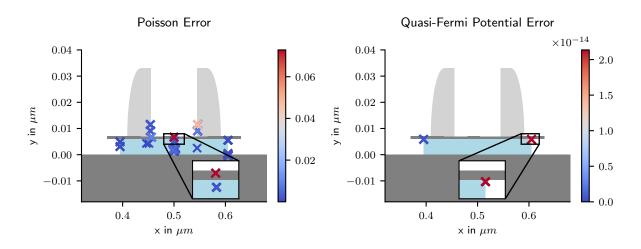

| Figure 3.11 | PyTaurus offers diagrams of critical vertices for all failed simulations                     | 59 |

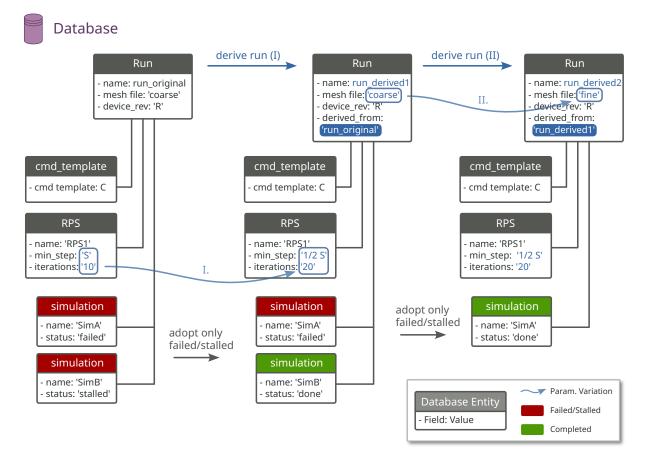

| Figure 3.12 | Refinement of table model runs                                                               | 60 |

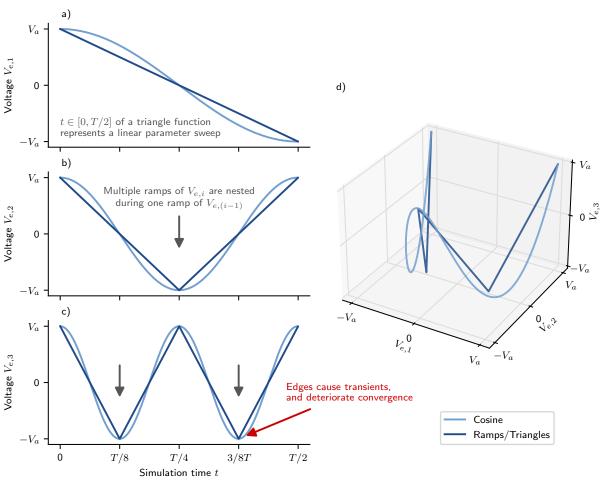

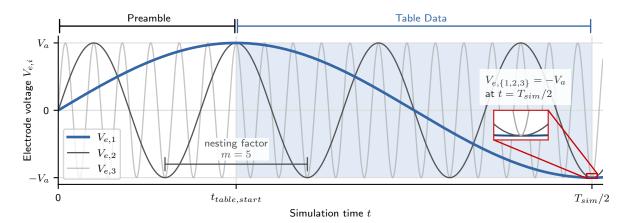

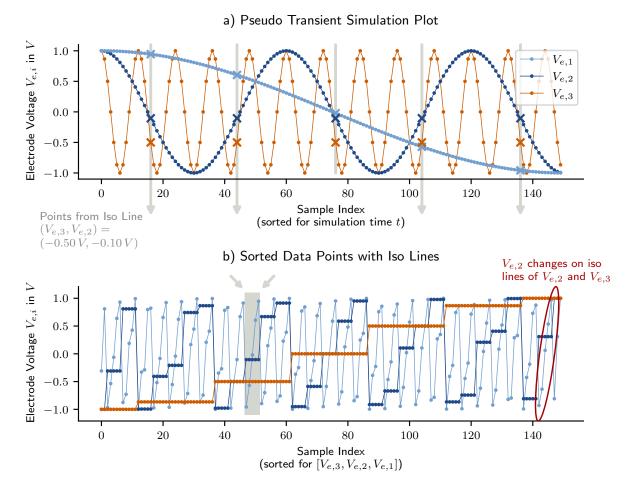

| Figure 3.13 | Pseudo transient simulation with triangle- or cosine function                                | 63 |

| Figure 3.14 | Pseudo transient simulation: sine source avoids initial ramps                                | 64 |

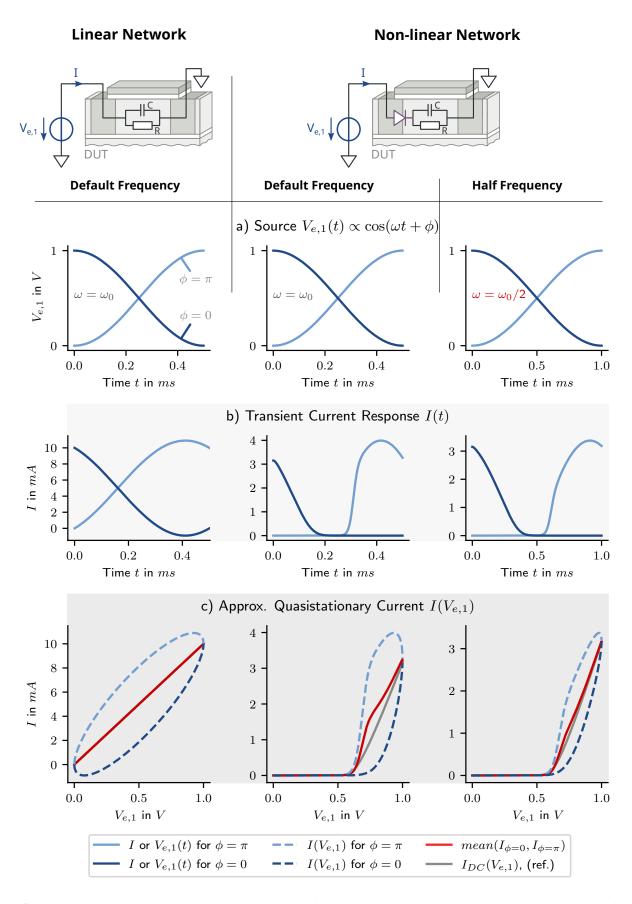

| Figure 3.15 | Transient compensation in linear and non-linear networks                                     | 66 |

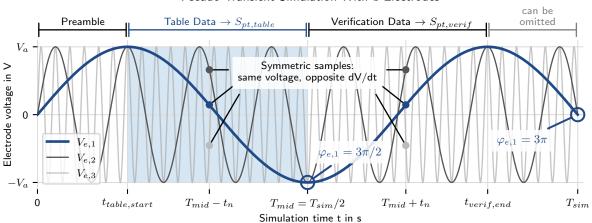

| Figure 3.16 | Symmetry of pseudo transient simulations                                                     | 68 |

| Figure 3.17 | Transient compensation in a parallel RC circuit                                              | 69 |

| Figure 3.18 | Limited numeric precision requires rounding                                                  | 72 |

| Figure 3.19 | Demonstration of regularity of pseudo transient data set                                     | 74 |

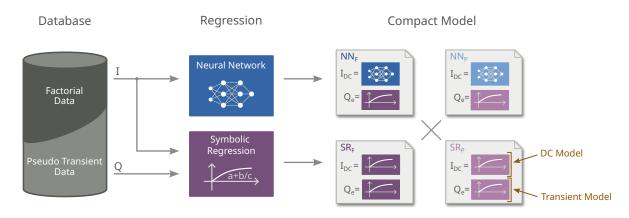

| Figure 4.1  | The four proposed compact models $NN_F$ , $NN_P$ , $SR_F$ and $SR_P$                         | 75 |

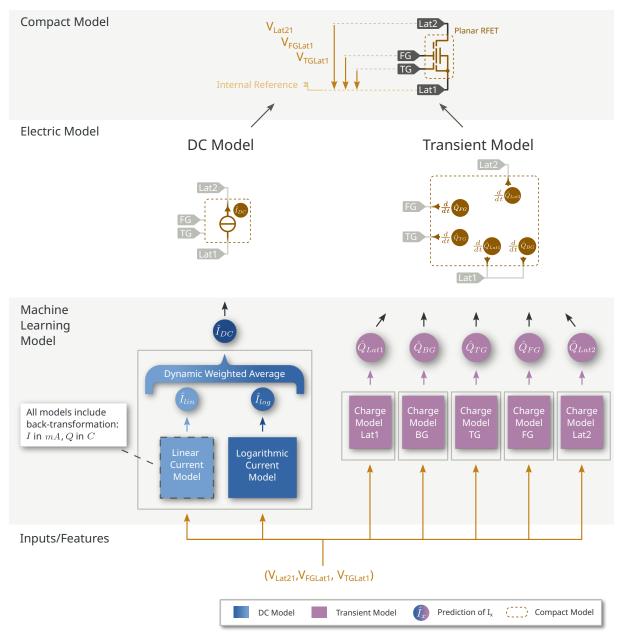

| Figure 4.2  | The architecture of the compact model                                                        | 77 |

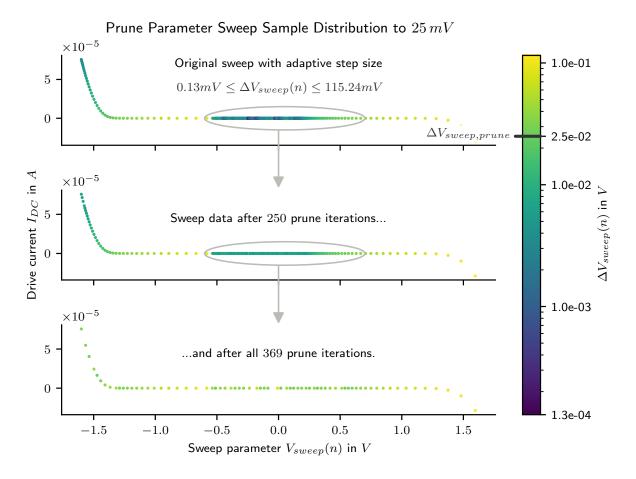

| Figure 4.3  | Pruning the data set to improve balance                                                      | 79 |

| Figure 4.4  | Split ratios of the machine learning models                                                  | 80 |

| Figure 4.5  | Noise augmentation of the training set                                                       | 81 |

| Figure 4.6  | Technology simulation introduces numeric noise                                               | 82 |

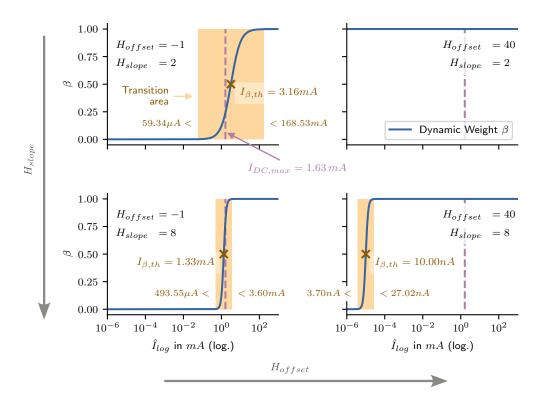

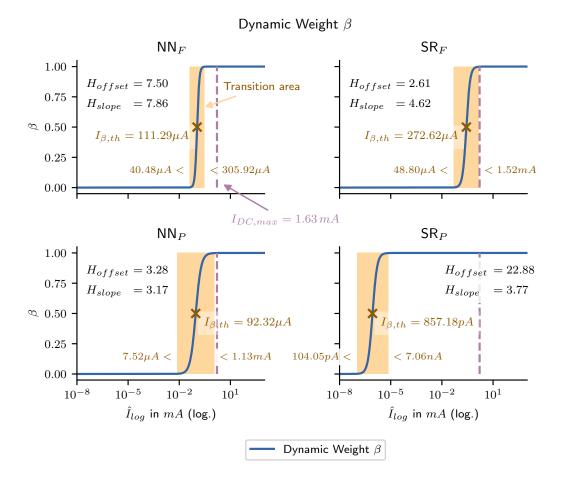

| Figure 4.7  | The dynamic weight function $\beta$ of the ensemble model $\ldots$                           | 83 |

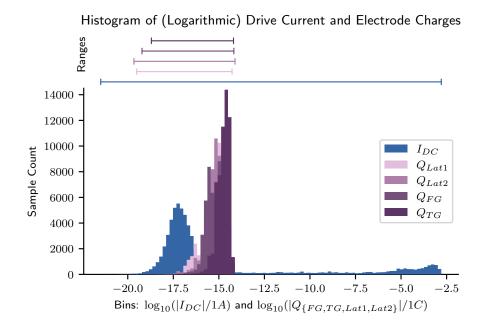

| Figure 4.8  | Histogram of drive current and electrode charge samples                                      | 85 |

| Figure 4.9  | Training of the linear neural network model                                                  | 87 |

| Figure 4.10 | Training of the logarithmic neural network model                                             | 88 |

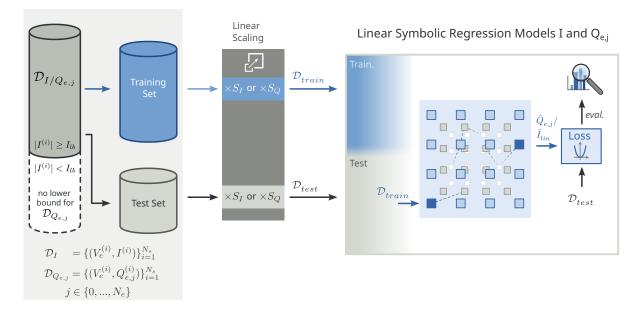

| Figure 4.11 | Training of the symbolic regression-based logarithmic model                                  | 91 |

| Figure 4.12 | The symbolic regression flow for linear current model and charge models                      | 92 |

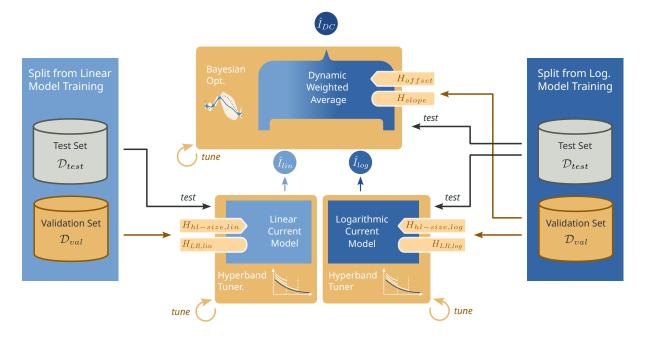

| Figure 4.13 | Overview of hyperparameter tuning with the respective sets                                   | 93 |

| Figure 4.14 | Corner cases of the dynamic weight function $\beta$                                          | 94 |

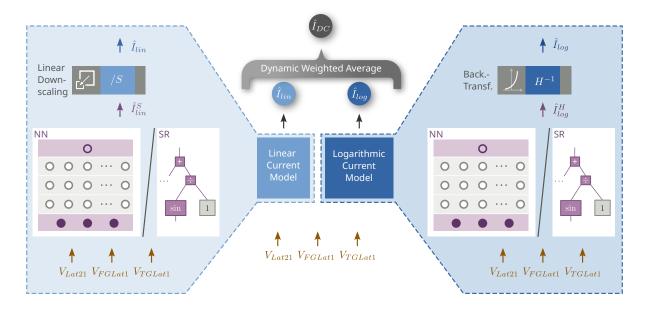

| Figure 4.15 | Deployment of the respective machine learning models                                         | 95 |

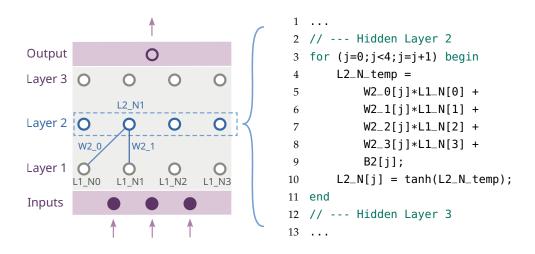

| Figure 4.16 | Implementing neural networks in Verilog-A                                                    | 96 |

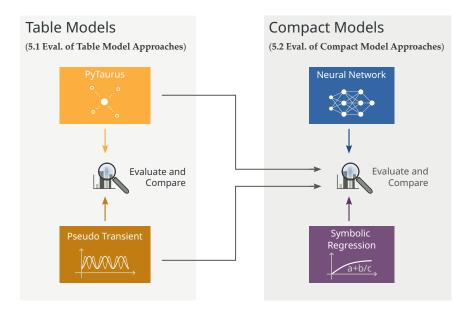

| Figure 5.1  | Evaluation comprises table models and compact models                                         | 99 |

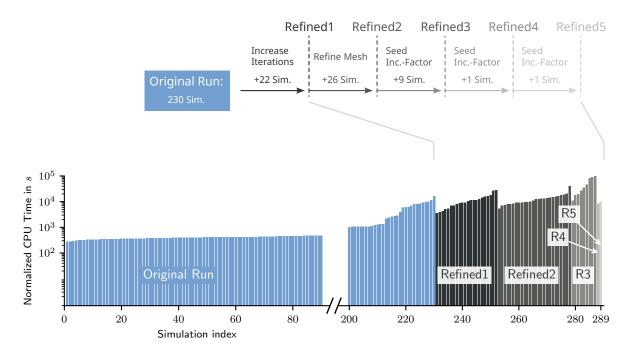

| Figure 5.2  | PyTaurus facilitates refinements for failing simulations                                     | 01 |

| Figure 5.3  | Suppressing the transient component by taking the sample-wise arith-                         |    |

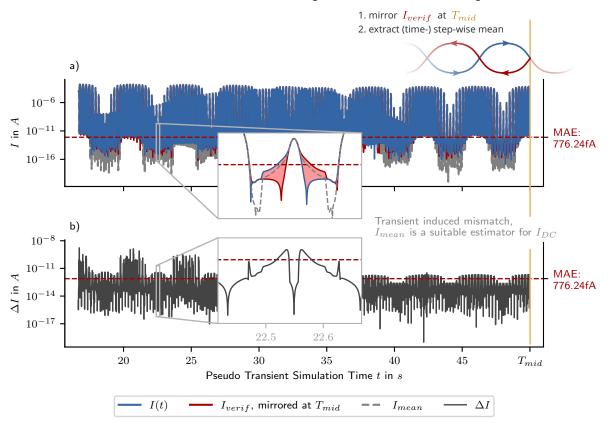

|             | metic mean                                                                                   | 03 |

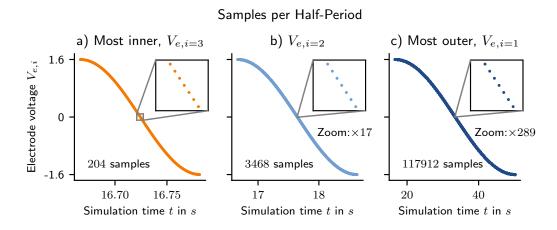

| Figure 5.4  | Pseudo transient method: Density of samples per half-period 1                                | 04 |

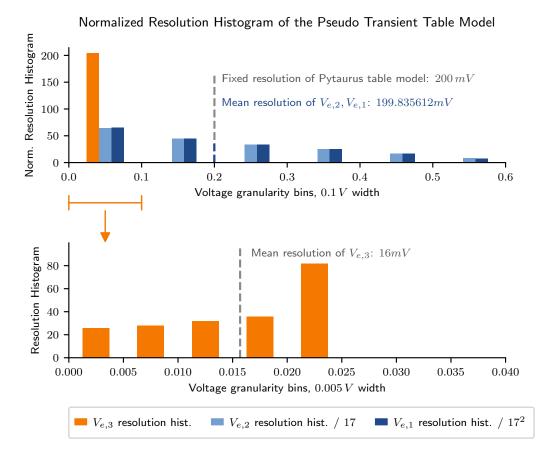

| Figure 5.5  | Histogram of the granularity of voltage steps in pseudo transient simu-                      |    |

|             | lation                                                                                       | 05 |

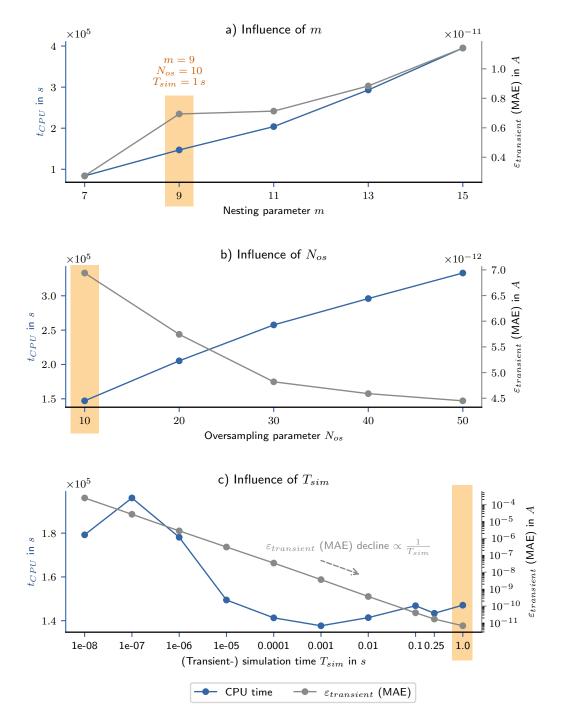

| Figure 5.6  | Individual influence of $m$ , $N_{os}$ and $T_{sim}$                                         | 07 |

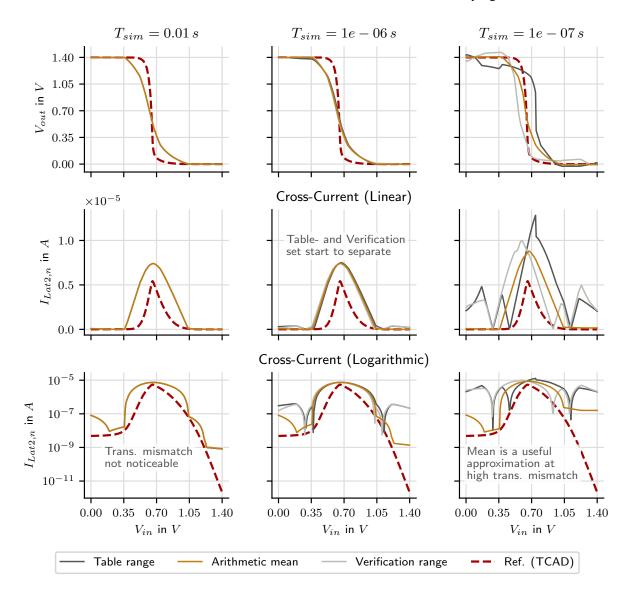

| Figure 5.7  | Evaluation of the transient suppression strategy                                             | 08 |

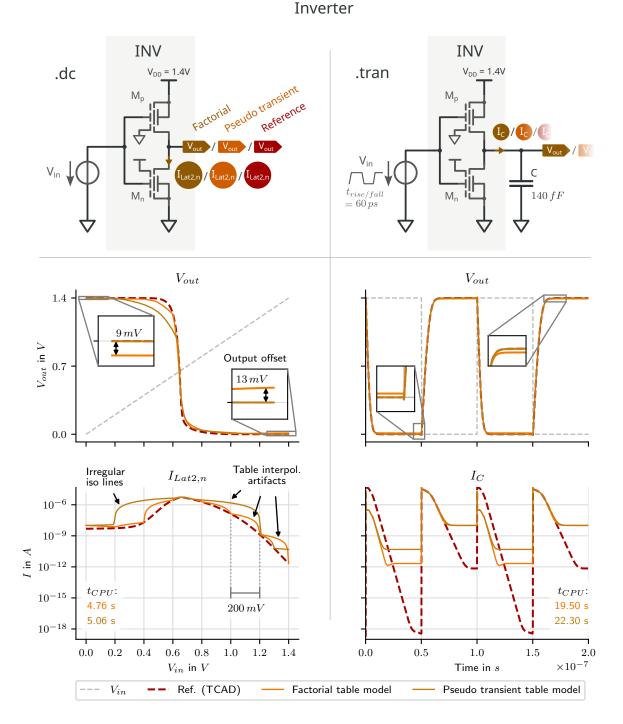

| Figure 5.8  | Inverter simulation featuring table models                                                   | 10 |

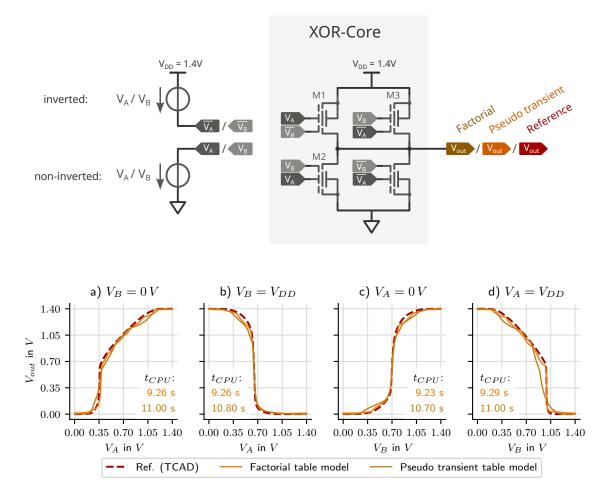

| Figure 5.9  | XOR simulation featuring the table models                                                    | 12 |

| Figure 5.10 | Ensemble hyperparameter training result                                                      | 13 |

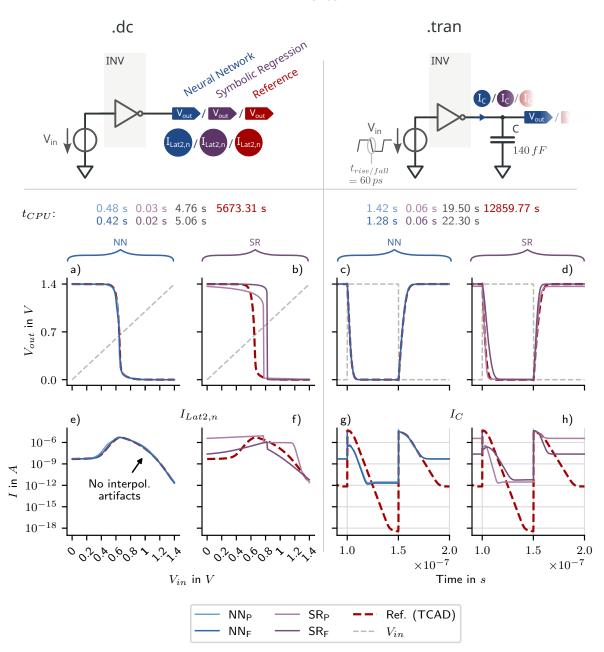

| Figure 5.11 | Inverter simulation with the proposed compact models 1                                       | 19 |

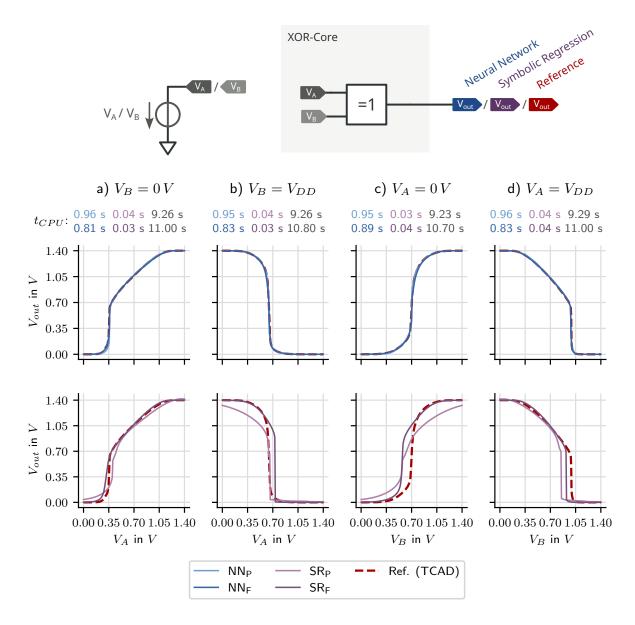

| Figure 5.12 | XOR simulation with the proposed compact models                                              | 20 |

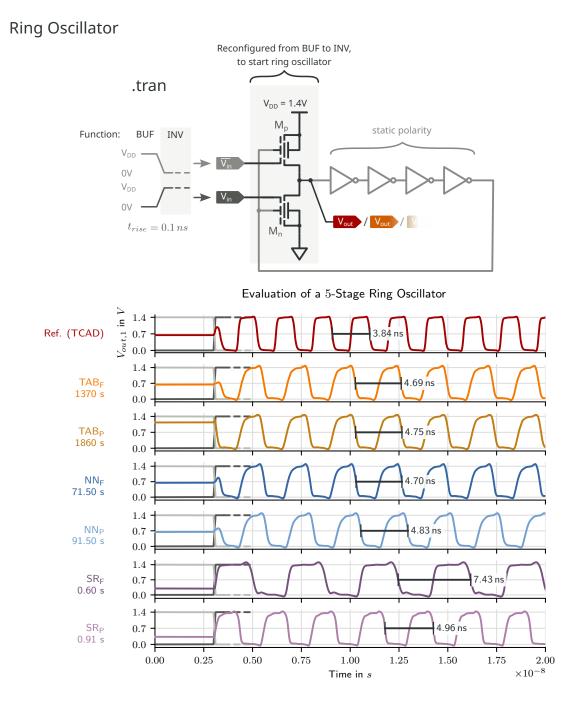

| Figure 5.13 | Simulation of a ring oscillator                                                              | 22 |

| Figure 6.1  | Overview of the models $TAB_{F}$ , $TAB_{P}$ , $NN_{F}$ , $NN_{F}$ , $SR_{F}$ and $SR_{P}$ 1 | 28 |

## List of Tables

| Table 2.1  | Structure of a lookup table                                               |

|------------|---------------------------------------------------------------------------|

| Table 4.1  | Available interactions of QLattice                                        |

| Table 4.2  | Overview of hyperparameters                                               |

| Table 5.1  | Characteristics of factorial and pseudo transient data set                |

| Table 5.2  | Arithmetic operations of the symbolic regression-based current models 115 |

| Table 5.3  | Arithmetic operations of the neural network-based current models 115      |

| Table 5.4  | Accuracy figures of current models                                        |

| Table 5.5  | Operation count of the charge models                                      |

| Table 5.6  | Accuracy figures of charge models                                         |

| Table 5.7  | Timing characterization of a NAND cell                                    |

| Table 5.8  | Timing characterization of a NOR cell                                     |

| Table 5.9  | Timing characterization of an XOR cell (1)                                |

| Table 5.10 | Timing characterization of an XOR cell (2)                                |

| Table A.1  | Simulation time for timing characterization of a NAND cell                |

| Table A.2  | Simulation time for timing characterization of a NOR cell                 |

| Table A.3  | Simulation time for timing characterization of an XOR cell (1) 149        |

| Table A.4  | Simulation time for timing characterization of an XOR cell (2) 150        |

|            |                                                                           |

## List of Acronyms

| ANN             | artificial neural network                                   |

|-----------------|-------------------------------------------------------------|

| AIC             | Akaike information criterion                                |

| API             | application programming interface                           |

| BIC             | Bayesian information criterion                              |

| BG              | back gate                                                   |

| BSIM            | Berkeley Short-Channel IGFET Model                          |

| <b>BSIM-IMG</b> | Berkeley Short-Channel IGFET Model - Independent Multi-Gate |

| BSON            | Binary Java Script Object Notation                          |

| CG              | control gate                                                |

| CMC             | Compact Model Council                                       |

| CMD             | command                                                     |

| CMOS            | complementary MOS                                           |

| CPU             | central processing unit                                     |

| DoE             | Design of Experiments                                       |

| DUT             | device under test                                           |

| DTCO            | design technology co-optimization                           |

| EI              | expected improvement                                        |

| FVM             | finite volume method                                        |

| FET             | field-effect transistor                                     |

| FG              | front gate                                                  |

| FPGA            | field-programmable gate array                               |

| FD-SOI          | fully depleted silicon on insulator                         |

| HiSIM           | Hiroshima-University STARC IGFET Model                      |

| JSON            | Java Script Object Notation                                 |

| Lat1            | lateral terminal 1                                          |

| Lat2            | lateral terminal 2                                          |

| MAE             | mean absolute error                                         |

| MAPE            | mean absolute percentage error                              |

| MLP             | multilayer perceptron                                       |

| MOS             | metal-oxide-semiconductor                                   |

|                 |                                                             |

| MOSCAP  | metal-oxide-semiconductor capacitor                 |  |  |  |

|---------|-----------------------------------------------------|--|--|--|

| MOSFET  | metal-oxide-semiconductor field effect transistor   |  |  |  |

| MSE     | mean squared error                                  |  |  |  |

| NoSQL   | Not only SQL                                        |  |  |  |

| NMOS    | n-type MOSFET                                       |  |  |  |

| OFAT    | one-factor-at-a-time                                |  |  |  |

| PARDISO | PARallel Direct SOlver                              |  |  |  |

| PG      | program gate                                        |  |  |  |

| PMOS    | p-type MOSFET                                       |  |  |  |

| ReLU    | rectified linear unit                               |  |  |  |

| RF      | radio frequency                                     |  |  |  |

| RFET    | reconfigurable FET                                  |  |  |  |

| RPS     | run parameter set                                   |  |  |  |

| SOI     | Silicon-On-Insulator                                |  |  |  |

| SIMD    | single instruction/multiple data                    |  |  |  |

| sMAPE   | symmetric mean absolute percentage error            |  |  |  |

| SPICE   | Simulation Program with Integrated Circuit Emphasis |  |  |  |

| SRAM    | static random access memory                         |  |  |  |

| TCAD    | technology CAD                                      |  |  |  |

| TFET    | band-to-band tunneling transistor                   |  |  |  |

| TG      | top gate                                            |  |  |  |

| TFE     | thermionic field emission                           |  |  |  |

| TMD     | transition-metal dichalcogenide                     |  |  |  |

| TRL     | technology readiness level                          |  |  |  |

| UI      | user interface                                      |  |  |  |

| VLSI    | very-large-scale integration                        |  |  |  |

| VTC     | voltage transfer characteristic                     |  |  |  |

|         |                                                     |  |  |  |

## List of Symbols

| Symbol                             | Unit          | Denotation                                                          |

|------------------------------------|---------------|---------------------------------------------------------------------|

| $\gamma$                           | $\sqrt{V}$    | Body effect factor                                                  |

| $\Delta I$                         | A             | Transient mismatch in pseudo transient simulation                   |

| $\Delta \Phi_e$                    | V             | Work function difference between electrode $e$ and a ref-           |

|                                    |               | erence electrode                                                    |

| $\Delta V_{sweep,prune}$           | V             | Minimum granularity of a parameter sweep with respect               |

|                                    |               | to a sweep variable $V_{sweep}$                                     |

| $\eta_r$                           | -             | Performance score of runner $r$                                     |

| heta                               | -             | Space of parameters for symbolic regression                         |

| $\lambda$                          | -             | Set of hyperparameters                                              |

| $\sigma_a$                         | A             | Variance of Gaussian noise for augmentation                         |

| arphi                              | -             | Probability density function                                        |

| $\phi$                             | -             | Space of analytical expressions for symbolic regression             |

| $\Phi$                             | V             | Electrostatic potential                                             |

| $\Psi_s$                           | V             | Surface potential at a surface <i>s</i>                             |

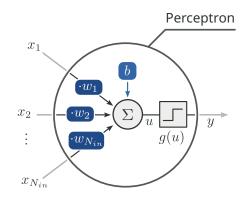

| $b_{l,n}$                          | -             | Bias of a perceptron $n$ in layer $l$                               |

| $C_{ox}$                           | F             | Oxide capacitance                                                   |

| $\mathcal{D}$                      | -             | Set of samples, corresponds to $\{(X_i, y_i)\}_{i=1}^{N_s}$         |

| $\mathcal{D}_{train}^{i,\sigma_a}$ | -             | Training set augmented with Gaussian noise ( $\sigma = \sigma_a$ ), |

|                                    |               | replica <i>i</i>                                                    |

| E                                  | -             | Tuple of device electrodes $E = (E_1, E_2,)$                        |

| $E_s$                              | $\frac{V}{m}$ | Electric field at a surface <i>s</i>                                |

| $f_{e,i}$                          | Hz            | Frequency of electrode <i>i</i>                                     |

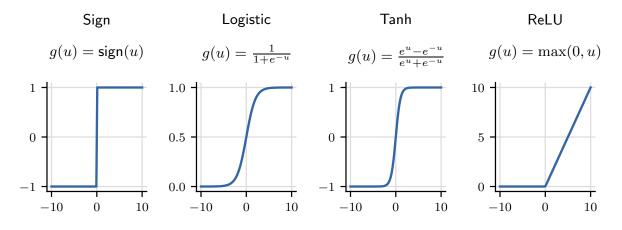

| g(u)                               | -             | Activation function                                                 |

| H                                  | -             | Hyperparameter                                                      |

| $I_{DC}$                           | A             | Transistor drive current (DC)                                       |

| $I_{lb}$                           | A             | Lower bound for current values in a data set                        |

| $I_c$                              | A             | Capacitive current                                                  |

| $I_r$                              | A             | Resistive current                                                   |

| $I_{on}/I_{off}$                   | $A \mid A$    | On-current / Off-current of a transistor                            |

| $L(\hat{y}, y)$                    | -             | Loss function                                                       |

| $m(, m_i)$                         | -             | Nesting factor of a pseudo transient simulation (per                |

| •                                  |               | dimension <i>i</i> )                                                |

| $N_c$                              | $cm^{-3}$     | Density of states in the conduction band of silicon                 |

| $N_d$                              | -             | Dimensionality of inputs (e.g. for a neural network                 |

|                                    |               | model)                                                              |

| $N_e$                  | -  | Number of electrodes; does not include the reference           |

|------------------------|----|----------------------------------------------------------------|

|                        |    | electrode                                                      |

| $N_{ops,nn}$           | -  | Number of scalar arithmetic operations of a neural net-        |

| <b>1</b> )             |    | work model                                                     |

| $N_{os}$               | -  | Oversampling Factor                                            |

| $N_s$                  | -  | Number of samples in a data set                                |

| q                      | C  | Elementary charge                                              |

| $Q_e$                  | -  | Tuple of electrode charges $(Q_{e,1}, Q_{e,2},)$               |

| $S_{e,i}$              | -  | Set of samples per electrode $E_i$ , $S_{e,i} = \{V_x, V_y,\}$ |

| $S_I, S_Q$             | -  | Linear scaling factor of the drive current models and          |

|                        |    | charge models                                                  |

| $t_{CPU}$              | s  | CPU time of a simulation                                       |

| $t_{tr,\{rise,fall\}}$ | s  | Rise-time and fall-time of a digital signal                    |

| $T_{\{si,ox\}}$        | m  | Thickness of silicon body or gate oxide layer                  |

| $V_{ch}$               | V  | Channel voltage, electron quasi-Fermi potential with           |

|                        |    | respect to the source                                          |

| $V_{DD}$ , $V_{SS}$    | V  | Supply voltages                                                |

| $V_e$                  | -  | Tuple of electrode voltages $(V_{e,1}, V_{e,2},)$              |

| $V_{fb}$               | V  | Flat band voltage                                              |

| $V_t$                  | V  | Thermal voltage                                                |

| $V_{th}$               | V  | Threshold voltage                                              |

| $w_{l,n,i}$            | -  | Input weight of a perceptron $n$ in layer $l$ for input $i$    |

| $W_e$                  | eV | Work function of electrode $e$                                 |

| $oldsymbol{W}_l$       | -  | Weight matrix of a layer $l$ within a multilayer perceptron    |

| $oldsymbol{X}_{in}$    | -  | Input vector of a neural network                               |

| $oldsymbol{X}_l$       | -  | Output vector of a layer $l$ within a neural network           |

| $\hat{y}$              | -  | Prediction of <i>y</i>                                         |

| $ar{y}$                | -  | Average of ground truth values of $y$                          |

|                        |    |                                                                |

## **1** Introduction

The world we live in today embraces emerging technologies more than ever, and this is only partly owed to a spirit of pioneering and curiosity. We foresee that continuous improvement of existing technologies is unlikely to be the solution for the challenges of the 21st century. A fair amount of work should be dedicated to enable and facilitate progress during the early stages of inventions, that shape our environment.

Particularly, semiconductors enhance our life in various aspects, as they provide processing of information in an increasing number of every-day appliances. Processing capabilities largely depend on the amount of transistors integrated into a unit area, so that integration density has become one of the most important figures to describe the performance of a semiconductor technology. A key to success of very-large-scale integration (VLSI), however, lies not only in the actual manufacturing capabilities. Sophisticated device models, based mostly on analytical formulations of the physical mechanisms in a transistor, enable reliable design processes for well established technologies. On the one hand, the semiconductor industry owes at least part of its success to the traditionally rather incremental improvements [2]. On the other hand, incremental improvements of a device or a process sooner or later run into limitations, which are typically physical in nature. In order to extend Moore's law [3] into the next decades, the search for disruption is, to the present day, in full swing and allows novel device concepts to emerge.

In the domain of field-effect transistors (FETs), the journey to a robust and powerful semiconductor model, a compact model, is challenging. It is often easier to refine models along with modest changes in the target technology, than to describe fundamentally new mechanisms and structures. Accuracy of a productively used compact model is essential to design a functioning integrated circuit. In emerging technologies, however, the focus is typically not on conducting a complete integrated circuit design flow. Required is rather the prediction of the performance of a device, characterized either by measurement or technology simulation, in the simulation of circuits. Although accuracy remains one of the central aspects, this imposes different requirements on predictive models: Predictive device models can spare many of the parameters, which do not contribute to technology assessment at an early stage. Parameters such as temperature or channel length, featured by industrial compact model, are typically not of interest for predictive circuit simulation. Instead, the creation of the model has to be quick and straightforward, in order to gain performance estimates in an early phase of the endeavor, and most importantly to predict behavior in a system-environment. These estimations can then be incorporated into the decision about adoption of a technology.

#### 1.1 Research Scope and Objective

This work contributes to predictive circuit modeling of emerging devices, by streamlining the generation of table models and the subsequent transition to analytic compact models. The focus

lies on the methods to be data driven with as little domain knowledge as possible, in order to apply them to semiconductor devices, where detailed analytic models of conduction are not yet available. In particular, the predictive, and yet accurate, simulation of digital circuits is the goal, which requires the model to provide accuracy over a wide range of bias regions. Efficient implementation is a key factor to allow the simulation of circuits with a high transistor count. The specific device under test (DUT) and subject of demonstration is a planar reconfigurable FET (RFET), which, due to its reconfigurable polarity, cannot be represented by conventional and industry-standardized compact models.

The scope of this work starts where the technology model of the DUT is available. Improvements on technology level are not subject of this work and neither is physical characterization. In consequence, this ensures that the proposed methods of generation and transformation of the data remain general and applicable to a wide range of emerging technologies. Table models are an established method for circuit simulation of emerging devices, but the methods to generate them are often cumbersome. The intermediate objective is therefore the generation of characteristic device data, which allow direct use as a table model. Particular attention is paid to efficient simulation design of technology simulation, as generation of characteristic datasets from technology simulation is the most time-consuming step in this work. Table models are typically inferior to compact models, with respect to performance and accuracy. The main objective is therefore to exploit the generated data set to form predictive compact models for the planar RFET by using machine-learning based modeling approaches.

The fundamental question that resonates with these objectives is: Is the machine learningbased compact model an improvement over the direct use of the original table model?

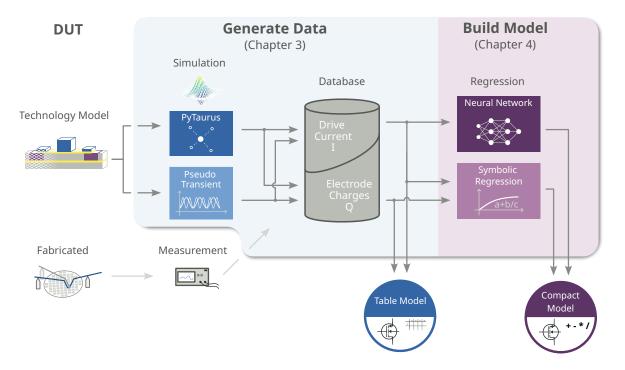

**Figure 1.1:** The implementation part of this work includes two methods of generating characteristic device data, which are then used to build data driven compact models using machine learning.

#### 1.2 Thesis Outline

The remainder of this work is structured as follows: The fundamentals of RFET technologies, the DUT and possible application in circuits are explained in Section 2.1. The various semiconductor modeling approaches on different abstraction levels, from technology modeling and data generation to compact models, are subject of Section 2.2. Lastly, the fundamentals of this work comprise the topic of regression-based machine learning and introduce deep learning and symbolic regression in Section 2.3.

Figure 1.1 provides an overview over the implementation part of this thesis. The proposed methods to obtain characteristic device data for table models, the factorial simulation cluster PyTaurus and the pseudo transient approach, are described in Chapter 3 and lead to 2 table models. Having generated a data set of bias points, in Chapter 4 symbolic regression is applied to the electrode charges, in order to obtain analytic equations for a transient model. One modeling approach for a DC model is based on deep learning, while a competing candidate is created by using symbolic regression. In total, two approaches to data sets (PyTaurus and pseudo transient approach) and two approaches to DC models (deep learning and symbolic regression) result in 4 compact model candidates.

The 4 compact model candidates, along with the 2 table model candidates are evaluated in Chapter 5.

# **2** Fundamentals and State of the Art

The technology modeling approaches proposed in this work, although based on data-driven methods, require understanding of the target technology to some extent. The modeled technology, RFETs, are described in Section 2.1. Within the scope of data driven modeling, the fundamentals consist of the methodology to produce device characteristic data (Section 2.2.1), state-of-the-art modeling techniques, such as compact models (Section 2.2.2), and how to construct data driven device models (Section 2.2.3). The proposed compact modeling approaches rely on machine learning methods, namely symbolic regression and deep learning, which are introduced in Section 2.3.

#### 2.1 Reconfigurable FETs

Conventional metal-oxide-semiconductor field effect transistors (MOSFETs) technologies rely on chemically doped semiconductors, providing two complementary device types: n-type (NMOS) and p-type (PMOS). The distinction comes from the type of dopant and is therefore decided at design time. Static complementary MOS (CMOS) logic design incorporates both transistor types, achieving rail-to-rail output with strong drive capability. In this section, an emerging device type, the RFET, is introduced, which features tuneable polarity at runtime. The mechanisms behind this feature are analyzed in Section 2.1.1. In order to provide general insights into the device which serves as DUT in this thesis, the planar RFET, Section 2.1.2 presents structure and characteristics. The proposed modeling approach in this work targets circuit simulation of logic cells, hence Section 2.1.3 provides an overview of established circuit topologies, which feature RFETs. The predicted implications and opportunities for circuit design are summarized.

#### 2.1.1 **RFET Fundamentals and Prototypes**

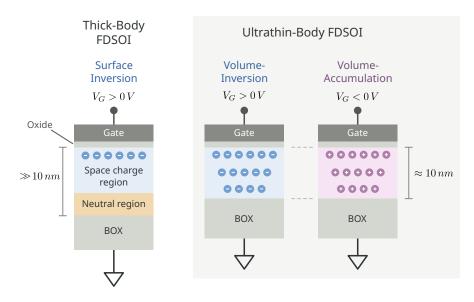

Coming from the background of conventional MOSFETs, where digital circuits typically consist of two types of devices with similar structure and complementary chemical dopants, the general principle of RFETs is not far off: Doping is still required, but instead of chemically induced impurity doping, the effect is caused by the electric field in semiconductor material and hence called *electrostatic doping* [4], [5]. Conventional CMOS FETs use the electric field caused by applying a voltage between gate and bulk electrode to create an inversion layer near the gate dielectric interface, which leads to a conductive channel. This channel then enables charge transport by providing free minority carriers. Similarly, electrostatic doping describes the influence on the concentration of free charge carriers in semiconductor material by biasing an adjacent gate [6]. However, one of the main differences is, that electrostatic doping leads to volume inversion or volume accumulation – a feature of ultrathin-body technologies, with a maximum body thickness of approximately 10 nm [7]. This distinction can be seen in

Figure 2.1, where a metal-oxide-semiconductor capacitor (MOSCAP) in thick-body Silicon-On-Insulator (SOI) technology is shown, along with an ultrathin-body fully depleted silicon on insulator (FD-SOI) MOSCAP. While the 2D inversion layer of the thick-body structure is described by classical physics, quantum mechanical effects in ultrathin bodies cause the charge carriers to escape 2D confinement at the interface, when a sufficiently high electrostatic field is applied. The substrate then enters volume inversion/-accumulation [8], [9]. As a result, the concentration of free carriers is distributed throughout the ultrathin body, resembling a chemically doped region in the semiconductor [5].

Unlike chemical doping, however, electrostatic doping can be applied dynamically at any time by biasing the according gate electrode. A typical application for electrostatic doping is when it comes to low dimensional materials such as transition-metal dichalcogenides (TMDs) and graphene, where the introduction of impurities into the atomic lattice without damaging the device is challenging. For these materials, electrostatic doping is already the standard doping technique [10]. Further, it is likely, that electrostatic doping can compensate increasing issues of chemical doping in highly scaled semiconductors, such as the formation of high doping gradients and the general spatial distribution due to complex geometry and growth dynamics [10]–[13].

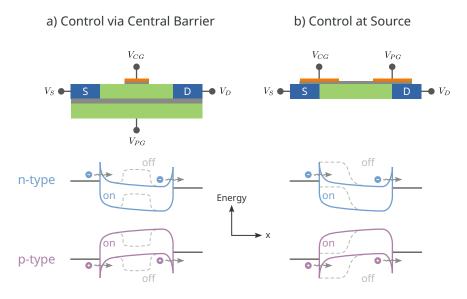

**Figure 2.1:** Unlike thick body technologies, ultrathin bodies down from  $\approx 10 nm$  thickness offer volume inversion/accumulation, providing free charge carriers. The effect is similar to impurity doping [5].

Electrostatic doping is one of the enabling mechanisms for RFETs, as it allows the reconfiguration of device polarity between n-type and p-type by providing the respective spatial carrier concentration. While there are other working principles, such as band-to-band tunneling [14], single-electron and spin transport [13], [15], this work focuses on the large group of Schottky barrier implementations. The principle of Schottky barrier RFETs is to program the doping of the transistor body, causing band bending with respect to Schottky barrier junctions at source and drain and selecting the conduction type [13]. Source and drain are typically silicide contacts. Two types of Schottky barrier implementations are distinguished by Mikolajick et al. [13] as shown in Figure 2.2. In type a) the polarity of the body region is selected by a buried program gate (PG) over the entire channel length. The electrostatic doping caused by  $V_{PG}$  in type a) results in band bending along the channel with respect to the Schottky barriers and enables either n- or p-type conduction between the silicide regions, which form source and drain. Charge transport is then controlled via a centered gate electrode, the control gate (CG), which modulates a potential barrier in the respective channel segment below. Depending on  $V_{CG}$ , a depletion region forms in the middle of the channel and impedes the drive current.

**Figure 2.2:** Two types of Schottky barrier RFETs are distinguished by Mikolajick et al. [13]: Type a) tunes polarity through the back gate (BG) and locally depletes the channel through a central top gate (TG). Type b.) directly influences the Schottky barriers at source and drain.

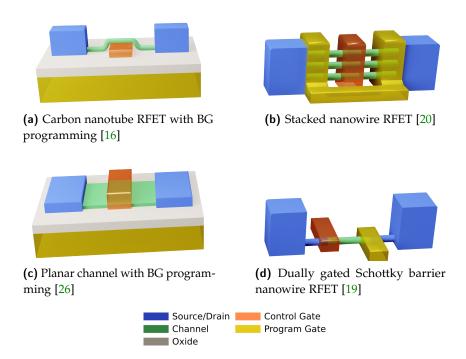

Type a) is attributed to Lin et al. [16], [17] in 2004, who achieve the elimination of ambipolar charge transport in favor of clear n-/p-type conduction in a carbon nanotube channel, placed over an aluminum gate electrode, as shown in Figure 2.3a. The BG electrode is used for polarity configuration, while the centered aluminum gate between BG oxide and the carbon nanotube switches the transistor on and off. In pursuit of improving the programming capabilities, which have up to then typically been offered by the BG [18], [19], De Marchi et al. [20] present a top-down fabricated stacked silicon nanowire RFET, shown in Figure 2.3b. Placing the PG over and especially around the Schottky junctions at source and drain increases the on-/off current ratio and the use of weakly p-doped nanowires benefit symmetry of n- and p-type conduction. Vertically stacking the nanowire channels further increases the drive current without demanding more area. The resulting device achieves drive currents up to  $75 \,\mu A$  for the n-type configuration at a programming voltage of  $V_{PG} = -4V$ ; a logic gate demonstration shows a symmetric inverter with a steep transition for  $V_{DD} = 1 V$ . Another device with a central CG emerges by Wessely et al. [21], [22] in 2012, who use a silicon nanowire channel above which the CG electrode is placed. The trend at Technical University of Darmstadt, however, moves towards planar devices as Krauss et al. [23]-[27] show reconfigurability of

**Figure 2.3:** Distinct RFET prototypes, based on different structures and materials, have been proposed in literature.

FD-SOI based planar channel geometries down to a length of 250 nm, as shown in Figure 2.3c. Drive currents in  $\mu A$  region are reached by a BG bias of at least  $|V_{PG}| = 2 V$  and  $|V_{DS}| = 1 V$ . These planar devices are the predecessors of the planar RFET, which is characterized in this work and described in Section 2.1.2.

Devices of type b) in Figure 2.2 allow the control of carrier injection directly at source, while the PG bias at drain blocks the respectively other carrier type [13]. This RFET type goes back to Weber et al. [19] who propose a dually gated silicon nanowire FET. During annealing, the nanowire forms nickel-silicide (NiSi) segments, extending the nickel source and drain regions from both sides towards the channel [18]. As shown in Figure 2.3d, the CG is placed over the Schottky junction at source to control the on/off state of the device. Located at the drain side, the PG allows selection of device polarity. Heinzig et al. [28] propose a similar top-gated silicon nanowire RFET but achieve an enhancement regarding  $I_{on}/I_{off}$  ratio from  $\approx 10^3$ , reported by Weber et al. [19], to  $10^8/10^9$  in highly symmetrical p-/n-type mode. Follow-up devices feature further improvements by inducing mechanical stress as a measure to precisely tune symmetry, which then allows the fabrication of a CMOS style inverter [29], [30]. Another significant step ahead is the co-integration of back gated RFETs within the GlobalFoundries 22FDX platform by introducing NiSi drain and source regions without changes to design rules and without the need for additional masks [31], [32]. Logic operation at  $V_{DD} = 0.8V$  is enabled by a program voltage of  $|V_{PG}| = 5.2V$  at the BG, which allows currents of up to  $10 \,\mu A/\mu m$  [31].

Symmetry between p- and n-type conduction is particularly important for a device, which aims at providing the flexibility of runtime polarity configuration. Conventional CMOS technologies can adapt to material properties and allow scaling of n-type MOSFET (NMOS) and p-type MOSFET (PMOS) channel width according to their targeted drive capabilities, but this is only possible because their respective role within the circuit is predetermined at design time. For devices where the decision between n- or p-type conduction is not made ahead of fabrication, structural adaptations cannot be exploited to balance drive strength and switching symmetry. As a consequence and similar to conventional CMOS scaling attempts, other materials are explored to eventually replace silicon and provide better symmetry, higher  $I_{on}/I_{off}$  ratios and lower supply voltages [33]. An important path is taken by Trommer et al. [34], who compensate the lower band gap energy (0.66 eV) of a germanium nanowire transistor with electrostatic control over the respective Schottky barriers. With this approach, off-state leakage is suppressed and the advantages of germanium, i. e. low threshold voltages  $V_{th,n} = 0.4 V, V_{th,p} = -0.2 V$  and high on currents, can be exploited. Germanium nanowire FETs offer an additional feature: Böckle et al. [35] find distinctive electrostatically tuneable negative differential resistance at room temperature in a germanium nanowire transistors, which is subsequently incorporated into a germanium nanowire RFET by Sistani et al. [36].

From a material point of view, the combination of Schottky junctions with fully depleted body appears to be suitable for operation in an extended temperature range, as two major sources of temperature dependent leakage are avoided: Firstly, the PN junctions between source/drain and the channel, and secondly the body diode between drain and bulk [37]-[39]. Especially for RFETs with virtually intrinsic body, the lack of chemical doping induced impurities is expected to further reduce phonon scattering effects and carrier freezeout, and therefore temperature dependence [37], [40]. Galderisi et al. [41] analyze the characteristic of a three-gated RFET over the temperature range of 80 K to 475 K and observe that the leading conduction mechanism at low temperature, thermionic field emission (TFE), leads to increasing threshold voltage at decreasing drive current towards the lower end of the observed temperature range. It is further stated, that this effect can be mitigated with thinner Schottky barriers, e.g. through higher PG bias, which increases temperature independent tunneling [41]. In high temperature regions up to 425 K, the threshold voltage decreases only marginally for ambipolar conduction mode, indicating that the device proposed in [41] can be a suitable candidate for harsh temperature environments. In general, the  $I_{on}/I_{off}$ -ratio in Schottky barrier FETs is limited by the band gap of the channel material, and the respective range of current, in case of the three-gated RFET, shifts significantly within the analyzed temperature range [41]. However, apart from material engineering, there is a second way to influence  $I_{on}/I_{off}$ , which is the suppression of leakage by exploiting additional PGs [34], [42]. Inherently provided by RFET devices, PGs allow the adjustment of  $I_{on}$  and  $I_{off}$  independently, as the Schottky barrier can be actively adjusted by electrostatic doping depending on device state and operating temperature.

#### 2.1.2 The Planar RFET

The device subject to characterization in this work follows the line of top-down planar devices by Krauss et al. [23]–[27]. The name of the device concept originates from a specific switching principle, which can be understood as a combination of enhancement- and depletion mode transistor, as described by type a) in Figure 2.2. Similarity to enhancement mode devices arises as the virtually intrinsic body, with a p-type boron background doping of  $1 \cdot 10^{15} cm^{-3}$ , is electrostatically doped via the BG. The BG, in form of an n-type substrate with chemical doping

#### 10 FUNDAMENTALS AND STATE OF THE ART

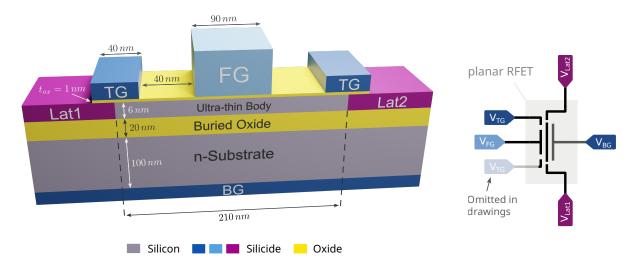

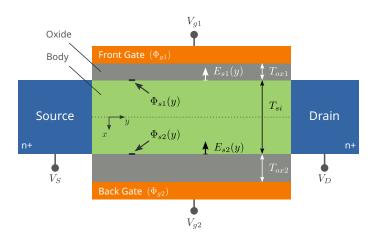

**Figure 2.4:** The planar RFET is based on a ultrathin-body FD-SOI technology. The BG and the top gates (TGs) allow programming of device polarity, while the front gate (FG) modulates the drive current. Only one TG is drawn in the schematic symbol, as the TGs are electrically connected. Figure is not to scale. [43]

of  $5 \cdot 10^{19} \, cm^{-3}$ , generates the respective n- or p-type channel in the body. From the top side of the device, the centered front gate (FG) locally depletes the channel by formation of a potential barrier, resembling depletion mode operation. The name *Dehancement Mode FET*, or short *DeFET*, emerges and Krauss [27] describes the respective technology simulation, fabrication and design space evaluation of the dual gate RFET.

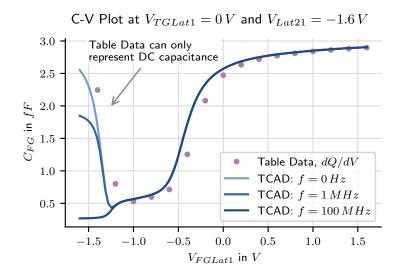

In an attempt to increase the control over the mid-gap Schottky barriers at source and drain, and similar to the stacked nanowire approach [20], Krauss et al. [27], [44] propose an extension to the dual gated DeFET concept. To enhance electrostatic doping of the Schottky barriers at source and drain, two gate electrodes, called *top gates*, are placed over the junctions, as shown in Figure 2.4. For the TG variant on a 6 nm thin and 210 nm long body the name planar RFET is adopted from [45] to make a clear distinction to the predominantly low dimensional material based RFET prototypes referred to in Section 2.1.1. The FG control mechanism is similar to the devices of type a) in Figure 2.2, while the arrangement of the TGs resembles the structure of type b). The two TGs are, to this date, exclusively used in combination and therefore regarded as a single electrode, modulating channel polarity and therefore Schottky barrier height at the source and drain junctions equally. What started out as an enhancement to BG programming was found to be a good replacement instead, as TG-only programming allows a threshold voltage of  $V_{th} \approx 500 \, mV$  in logic cells of  $V_{DD} = 1.4 \, V$ . The symmetric structure of the device allows both channel adjacent terminals to act as source and drain of the charge transport, depending on the respective operating point. For the purpose of modeling, this work refers to both channel adjacent terminals as *Lat1* and *Lat2*.

The structure of the planar RFET along with the circuit symbol, which represents the planar RFET in this work, proposed in [46], are shown in Figure 2.4. Although both TGs are used in a configuration where they are electrically connected, the symbol is designed to show only

one TG connection to improve schematic readability. The one input at  $V_{TG}$  represents both electrically connected TGs.

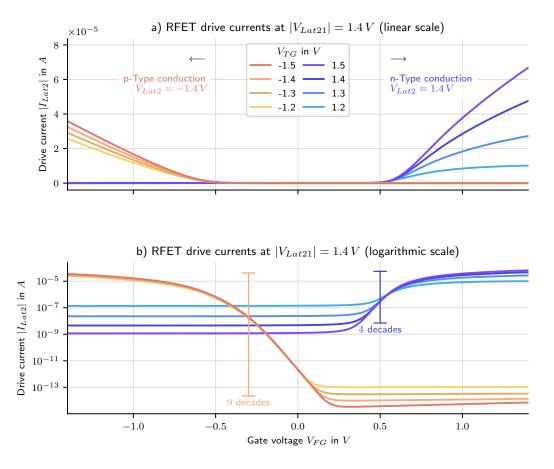

**Figure 2.5:** The planar RFET, shows a balanced maximum drive current for  $|V_{Lat21}| = 1.4 V$ . The  $I_{on}/I_{off}$  ratio for n- and p-type conduction modes, however, lacks symmetry [43].

With a background doping of  $5 \cdot 10^{17} cm^{-3}$  and work functions  $W_{TG} = 5 eV$  and  $W_{FG} = 4.75 eV$ , the RFET is optimized for symmetric  $I_{on}$  in digital cells of  $V_{DD} = 1.6 V$ . Following the approach in [43], in this work, the device is employed to digital cells with  $V_{DD} = 1.4 V$ , which leads to the characteristic shown in Figure 2.5. At  $V_{Lat21} = 1.4 V$ , the  $I_{on}/I_{off}$  ratio of p-type conduction with  $\approx 10^9$  exceeds the n-type conduction  $I_{on}/I_{off}$  ratio of  $\approx 10^4$ , while the maximum drive current remains in a similar regime of  $40 \mu A$ .

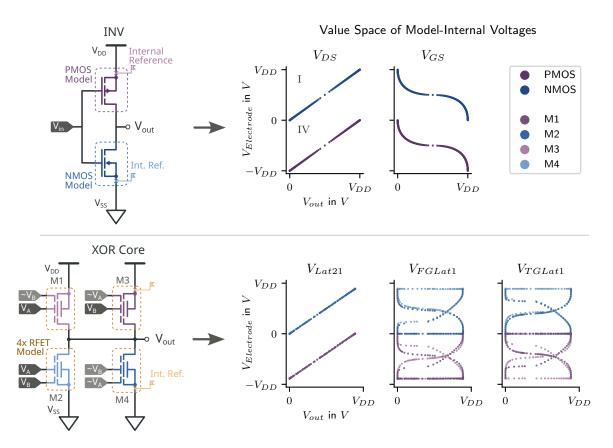

#### 2.1.3 Circuits with Reconfigurable Devices

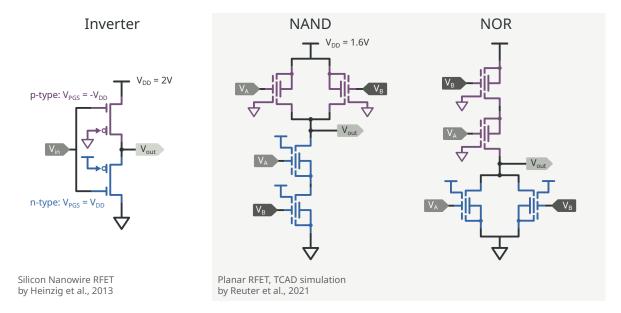

The goal to reduce chip area, aligned with the typical VLSI trends, extends to RFETs on device level, where a FG length of 20 nm is already demonstrated [31]. In general, conventional static CMOS circuits can be implemented in RFET technologies, by programming the electrostatic doping of the respective devices in a static way, e.g. by hard-wiring PGs to a supply voltage. With only  $V_{DD}$  and  $V_{SS}$  available, the involved voltages between PGs and the respective source terminal have to be brought to the range of  $|V_{PGS}| \leq 2V$  and still provide clear polarity control. Enabled by the high symmetry between p- and n-type conduction in [28], Heinzig et al. [29]

present the first inverter circuit based on two statically configured silicon nanowire transistors for  $V_{DD} = 2V$ , as shown in Figure 2.6. The proposed RFET inverter resembles the conventional static CMOS inverter, with the PG of the pull-down device connected to  $V_{DD}$  and the PG of the pull-up devices connected to  $V_{SS}$ . In the schematic drawing of Figure 2.6 the inverter is depicted as a dual gate device and uses a circuit symbol representation from [13]. The principle of replicating static CMOS logic topology with RFETs can be applied to other common logic gates. INV, NAND, NOR gates show correct switching behavior in technology CAD (TCAD) simulation and their performance is comparable to an SOI technology of similar feature size, as shown in [45]. Using RFETs as statically configured devices in CMOS-style topologies further allows threshold voltage scaling over a wide range, similar to the body-biasing in FD-SOI [47]. A possible use-case for the wide range tuning ability of the planar RFET is region-based dynamic scaling of threshold voltage, e.g. in field-programmable gate arrays (FPGAs), as proposed by Pfau et al. [48].

**Figure 2.6:** RFETs can be programmed statically, by hard-wiring the PG to a supply rail. This allows static CMOS topologies to be adopted for RFET technologies. Heinzig et al. [29] propose a silicon nanowire inverter, *NAND* and *NOR* implementations with the planar RFET are demonstrated in [45].

The mere replacement of NMOS/PMOS devices with statically configured RFETs, however, subjects the success of the RFET technology to a similar down scaling pace as conventional CMOS technologies. Instead, a way to outperform chemically doped CMOS technology can be to exploit the inherent features, such as dynamic reconfiguration. RFETs allow the design of circuits which either change behavior in order to provide multiple functions or to use the PG as additional signal input for reduced transistor count per logic function [49]. Examples of both cases have already been demonstrated in the early phases of RFETs, after Lin et al. [16] proposed the polarity tuneable carbon nanotube RFETs. With similar carbon nanotube structures as [16], O'Connor et al. [50] propose two stage dynamic logic cells, where the PG of the logic devices is used to configure the cell function. Pre-charge and evaluation transistors

are configured with static polarity. 8 different forms of binary logic functions using *AND* and *OR* conjunctions are possible with 3 logic transistors in [50]. *XOR* operation requires 5 logic transistors implemented with RFETs.

Fully complementary digital circuits with full output swing are subject to structural constraints: The pull-up branch consists of p-type devices and the pull-down branch consists of n-type devices. Deviation from this topology results in reduced output swing, and devices with wrong polarity in their respective branch are called *misconfigured* [51], [52]. A basic example for this constraint is the transmission gate, where two complementary devices are required for strong drive, to avoid the loss of threshold voltage  $V_{th,n/p}$  over the driving transistor. For conventional doped CMOS, this requirement can easily be regarded during logic cell design. But reconfiguring an RFET from n- to p-type conduction in a pull-down branch, and vice versa for a pull-up branch, results in a significant deterioration of output swing. Ben Jamaa et al. [53] conclude that polarity reconfiguration with full output swing in CMOS-style topologies can be established by providing the branches in each pull network as parallel RFETs. The resulting topology is similar to a transmission gate and pairs devices of the respectively wrong polarity configuration with their complementary counterpart. The demonstration, based on a carbon nanotube RFET, includes statically configured circuits, such as the logic cells shown in Figure 2.6, but extends up to more complex static CMOS gates.  $Y = (A \oplus B) \cdot (C \oplus D)$  is realized with 8 devices, where signal inputs are used for polarity configuration of transmission gate pull branches [53].

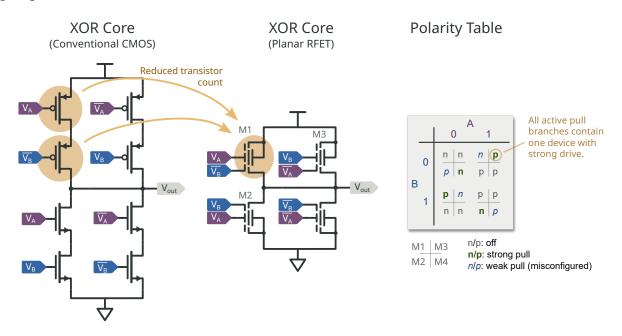

**Figure 2.7**: The *XOR* gate shows how RFETs can reduce the transistor count by providing higher expressiveness than a conventional MOSFET [45], [54].

A basic example for transistor count reduction, by using PGs as inputs, is the *XOR* gate proposed by Gaillardon et al. [54]. The core of the *XOR* cell consists of 4 RFETs and relies on the availability of inverted inputs. This *XOR* core is analyzed with 4 planar RFETs in [52],

as shown in Figure 2.7. The key to the transistor count reduction is the integration of the logic functionality of two serial MOSFETs into one, by using the PG as signal input [53]. The resulting polarity states of each device for each input combination of *A* and *B* of the planar RFET implementation is shown in Figure 2.7 and reveals that the active pulling branches in every state consist of a strong pull device, paired with a weak pull device [52]. The left side of the *XOR* core, M1 and M2, can be interpreted as an inverter of *A*, if *B* = 1, as both devices are configured with correct polarity and therefore provide strong pull, respectively. Therefore, the transitions of *A* with  $V_B = V_{DD}$  are dominated by the FG switching behavior of the RFET. Further, there are transitions where the switching comes from flipping the polarity of strong pulling devices, such as the transition of *A*, if *B* = 0. Here, the full swing output is provided by the planar RFET in particular, and for a sufficiently high  $I_{on}/I_{off}$  ratio in general. The principle of integrating the functionality of multiple MOSFETs into one extends to more than two inputs: Trommer et al. [55] show an RFET with 4 independent gates, which provides wired-*AND* functionality.

While the higher expressiveness of the single device provides further benefits on circuit level, e. g. for compact multiplexing [56], implementation of area-efficient neuromorphic circuits [57], hardware security through key based authentication [58] and tuneable differential stages [59], at the point of physical implementation, this can come at a cost. The availability of additional PGs aggravates routing congestion and calls for novel place and route strategies [49], [60]–[62].

The scope of this work is restricted to basic digital circuits, such as the shown *INV*, *NAND*, *NOR* and *XOR* cell, which have been demonstrated with the planar RFET in [45], in order to evaluate the proposed device modeling approaches on fundamental static and reconfigurable logic gates.

#### 2.2 Modeling Semiconductor Devices

On a low technology readiness level (TRL), the evaluation of fabricated emerging devices typically focuses on device level characteristics, such as leakage, drive current and sub-threshold slope. Early prototype devices are typically fabricated in arrays of solitary devices, which can be subject to substantial process variation. On the one hand, evaluation in form of comparison against devices from established technology nodes is fair, as the plain characteristic values allow to grasp the achieved performance of the emerging device. On the other hand, semiconductor devices are typically parts of integrated circuits, rendering circuit level evaluation a convincing argument for acceptance of emerging device concepts. And then there are devices with novel features, such as RFETs, which are unlikely to compete with established and highly scaled technology nodes on device level, while their benefits play out on circuit level [13]. One way to demonstrate these benefits is the actual fabrication and measurement of circuits. But fabrication of emerging technologies typically means going off the beaten track and the resulting DUTs often suffer from issues such as low yield, high process variation and degradation during measurement. For compact circuits with low transistor count, such as logic cells, this can be a feasible approach [29], [54]. Simulation is, in turn, often more cost-efficient and leads to reproducible results with fully controllable device variation without degradation during characterization. As this work contributes to predictive modeling and simulation of emerging

semiconductor devices, it is important to inspect existing tools and work out capabilities and limitations.

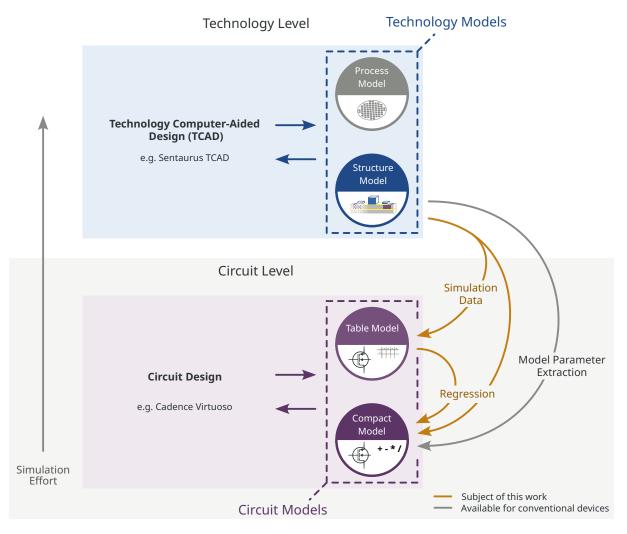

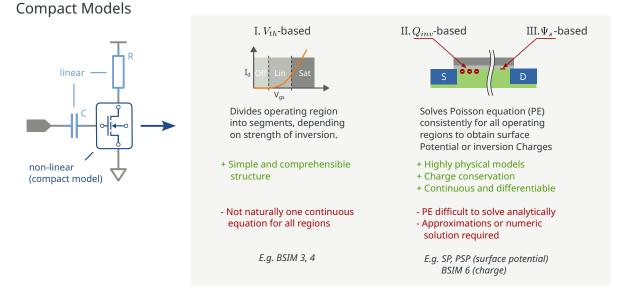

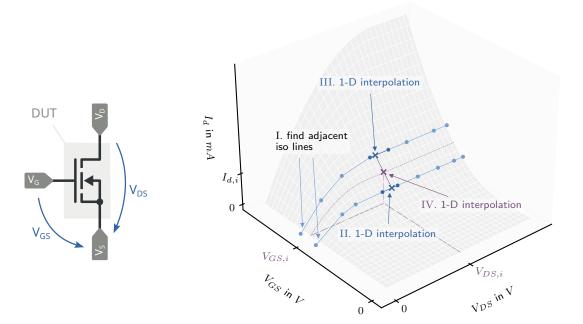

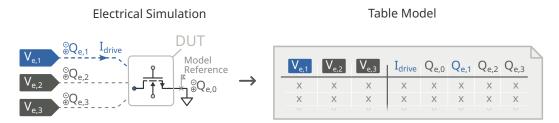

**Figure 2.8:** Conventional semiconductor devices can be modeled using industry standard compact models. A typical approach for emerging devices is to build a table model. Further, this work explores machine learning-based regression methods.

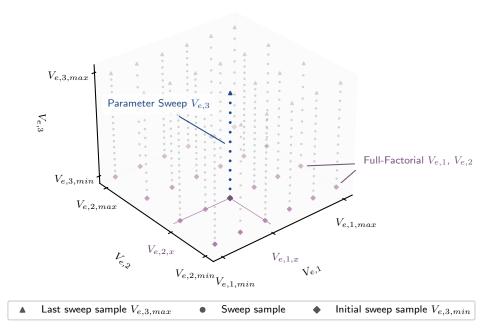

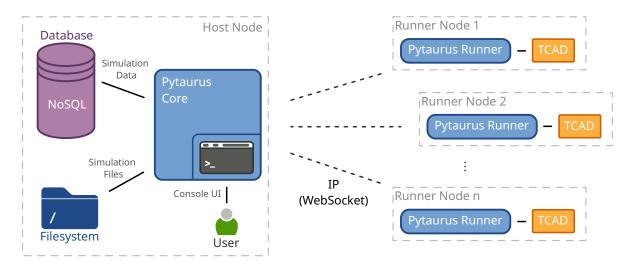

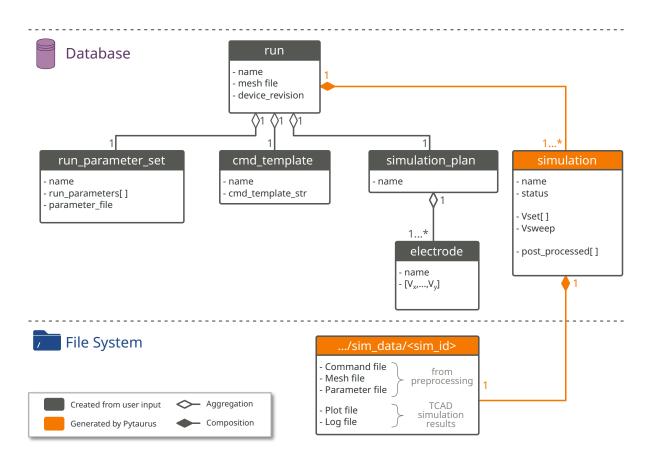

Two abstraction levels of simulation models are relevant for this work and therefore shown in Figure 2.8, namely technology models and circuit models. In circuit simulation physical details of conduction mechanisms become less relevant and efficiency gains importance. In consequence, models with less computational effort, e.g. through abstraction, have to be constructed. The step from technology simulation to circuit simulation can be overcome in various ways. Figure 2.8 shows the three commonly taken paths. On the technology level, TCAD suites provide tools for model parameter extraction, such as TCAD2SPICE in Synopsys TCAD. If structure and working principles of the DUT are represented by an existing and supported compact model, the path from technology model to a parameter set for an already established compact model is quick and typically automatic. In this work, conventional parameter extraction methods are not possible, as there are no available compact models for the planar RFET device concept. Because of their importance in the state of the art, compact models are introduced in Section 2.2.2. The second approach, the table model, is a data driven approach, where the characteristic data from TCAD simulation are provided to the circuit simulator and interpolated at runtime. Performance and accuracy are to be balanced, as higher sample count leads to higher sample density, which in turn negatively affects memory requirement and execution time of the interpolation algorithm. Table models are covered in Section 2.2.3. A third way is using the characteristic data, e. g. the table model, to perform regression and obtain analytic expressions which then form a compact model. Previous work in the area of regression-based modeling, to which this work contributes, is summarized in Section 2.2.2.

The particular TCAD suite used for this work is Sentaurus TCAD by Synopsys and the program structure on which the methods in Chapter 3 are build upon are introduced in Section 2.2.1. Circuit level simulation is conducted in Cadence Custom IC Design Environment (2022) [63], using the Simulation Program with Integrated Circuit Emphasis (SPICE) simulator SPECTRE.

#### 2.2.1 Technology Models and TCAD Simulation

TCAD refers to a suite of tools for design technology co-optimization (DTCO), which target predictive technology- and process modeling. Technology modeling resorts to physical models implemented by the TCAD tool, to be solved numerically in discretized parts of a structural semiconductor model. The computational effort of technology simulation depends on the granularity of the computational mesh and is typically substantial, compared to circuit level device models. In return, technology simulation provides insights into the internal physical parameters of the model beyond measurement capabilities. Another strong argument for the use of technology simulation is the arbitrary variation of boundary conditions and material parameters for prediction and optimization. Today, the employed physical models can be considered reliable for extensively studied semiconductor materials such as silicon, decreasing the number of exploratory fabrication runs required [64].

In this work, Sentaurus TCAD is used for generating device characteristic data, which are then either used as a table model or transformed into a compact model. The main use of TCAD for this work lies in generating characteristic device data for the data driven modeling approaches. This section provides an overview of the features relevant to efficiently generate these data samples. Further, details about the Sentaurus TCAD device simulator implementation with respect to the efficient generation of data are provided.

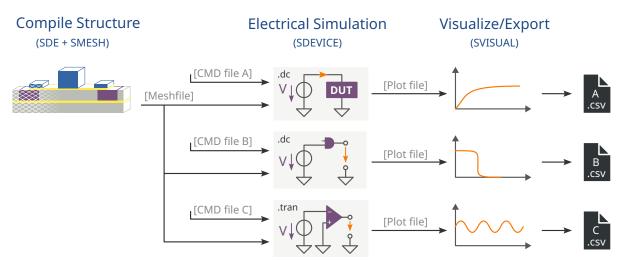

This work builds upon a structural technology model developed in [27] using Sentaurus Structure Editor and focuses on electrical device simulation using Sentaurus Device. The topic of process simulation is out of scope of this work. A typical simulation flow of a structural technology model in Sentaurus TCAD is shown in Figure 2.9. The first step is to create a structural technology model, which defines device geometry along with the respective materials, doping profiles and other spatial properties in either 2 or 3 dimensions. After definition of structural parameters, a mesh is placed onto the structure and defines the discretized volume in which the semiconductor equations are to be solved during electrical simulation using finite volume method (FVM). The interface to electrical simulation is provided in form of equipotential electrode definitions, which form part of the boundary conditions of

the simulation. For electrical device simulation it is important to recognize that convergence and computational effort depends, aside from the numeric setup of the device simulator, heavily on the meshing of the structure model.

Sentaurus TCAD Data Generation