## BEYOND MITIGATIONS: Advancing Attack Surface Reduction and Analysis

Vom Fachbereich Informatik (FB 20) an der Technischen Universität Darmstadt zur Erlangung des akademischen Grades eines Doktor-Ingenieurs genehmigte Dissertation von:

### MSc. Patrick Thomas Jauernig

Referenten: Prof. Dr.-Ing. Ahmad-Reza Sadeghi (Erstreferent) Prof. N. Asokan, Ph. D. (Zweitreferent)

Tag der Einreichung: 16. Oktober 2023 Tag der Disputation: 27. November 2023

System Security Lab Fachbereich Informatik Technische Universität Darmstadt

Hochschulkennziffer: D17

Darmstadt 2023

Patrick Thomas Jauernig: Beyond Mitigations: Advancing Attack Surface Reduction and Analysis, © October 2023

Darmstadt, Technical University of Darmstadt Day of dissertation defense: 27.11.2023 Dissertation publication at TUprints: 2024 URN of the dissertation: urn:nbn:de:tuda-tuprints-265292

DOCTORAL REFEREES: Prof. Dr.-Ing. Ahmad-Reza Sadeghi (1<sup>st</sup> Doctoral Referee) Prof. N. Asokan, Ph. D. (2<sup>nd</sup> Doctoral Referee)

FURTHER DOCTORAL COMMISSION MEMBERS: Prof. Dr. Carsten Binnig Prof. Dr. Sebastian Faust Prof. Dr. Marco Zimmerling

Veröffentlichung unter CC-BY-NC-ND 4.0 International Namensnennung, nicht kommerziell, keine Bearbeitung https://creativecommons.org/licenses/

#### Erklärung gemäß §9 der Promotionsordnung

Hiermit versichere ich, die vorliegende Dissertation selbstständig und nur unter Verwednung der angegebenen Quellen und Hilfsmittel verfasst zu haben. Alle Stellen, die aus Quellen entnommen wurden, sind als solche kenntlich gemacht. Diese Arbeit hat in gleicher oder ähnlicher Form noch keiner Prüfungsbehörde vorgelegen.

Darmstadt, Germany, October 2023

Patrick Thomas Jauernig

## Abstract

In recent decades, we have witnessed an arms race between software attacks and defenses. This ongoing battle has seen modern computer systems incorporating a multitude of defenses, working collaboratively to shield sensitive applications and data from malicious attacks. Despite growing layers of security measures, vulnerabilities persist, often circumventing the most advanced safeguards and putting entire systems at risk. But how can we end this relentless cycle of attack and defense? One crucial aspect to systematically tackle the problem at hand is *attack surface reduction*, i.e., reducing the code that 1) is reachable by an attacker and 2) can also reach sensitive information. Attack surface reduction is not only applicable to code within an application but also extends to the broader software stack, including libraries and the operating system, which are inherently trusted components, often referred to as the Trusted Computing Base or TCB. Another crucial element is attack surface analysis, which assesses how vulnerable a program is. This analysis plays a pivotal role in uncovering vulnerabilities across the entire software stack, thereby bolstering the security of critical software components like the Trusted Computing Base (TCB). Although attack surface analysis is a well-established concept, recent advances, particularly in the realm of fuzzing, have begun to pave the way for its gradual adoption by the industry. Nonetheless, numerous challenges within this field still must be addressed to make it an integral part of the industry's software development process.

In this dissertation, we design, implement, and evaluate 1) novel attack surface reduction architectures using in-process isolation and enclaves, 2) protocols using these architectures as powerful primitives, and 3) an algorithmic improvement to fuzzing for attack surface analysis.

**Secure In-Process Compartments.** In-process isolation is an important building block for attack surface reduction within an application by segregating regular and sensitive data. Previous approaches primarily focused on broadly applicable isolation primitives, which allow developers to compartmentalize their applications at the cost of significant hardware and performance overheads.

In IMIX, we propose an instruction set extension for in-process memory isolation that allows high-frequency domain switching. IMIX is a minimally invasive approach to reduce the attack surface for highly sensitive data such that this data can only be accessed by the dedicated part of the application code. In contrast to state-of-the-art randomization schemes, IMIX safeguards the run-time defenses' metadata in a process deterministically. We implemented a prototype of IMIX to protect the metadata of the Code Pointer Integrity scheme with practical performance. **Flexible Enclaves for Application-driven Security.** While in-process isolation can create different security domains within an application, Trusted Execution Environments (TEEs) allow the entire sensitive application to run within an isolated compartment (a so-called enclave) without trusting the operating system or hypervisor. Traditionally, these enclave architectures only provide a single enclave type per platform, which forces developers to adapt the application to the enclave's execution environment. This either increases the attack surface unnecessarily or restricts the sensitive app's functionality.

In CURE, we introduce the first TEE for flexible attack surface reduction based on the requirements of the sensitive application. CURE leverages system bus filtering to create different types of enclaves, enabling flexible per-enclave resource assignments for peripherals and even DMA devices. We prototype CURE for the open RISC-V architecture and evaluate its performance overhead and the hardware area overhead on an FPGA- and simulator-based setup.

**Enclaves as Security Primitives in Protocols.** While attack surface reduction with TEEs is a cornerstone of modern software protection, TEEs can also be leveraged as a security primitive to create powerful and efficient protocols. In this dissertation, we present TEE-based protocols for off-chain smart contract execution, and machine learning model protection.

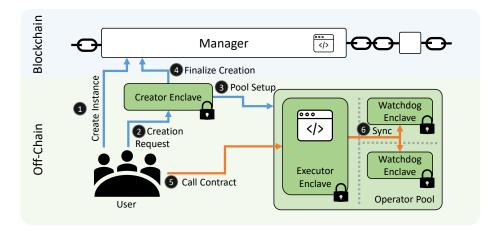

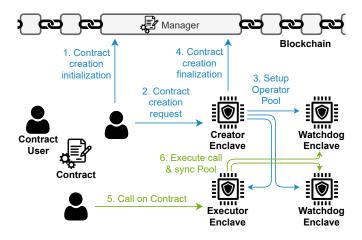

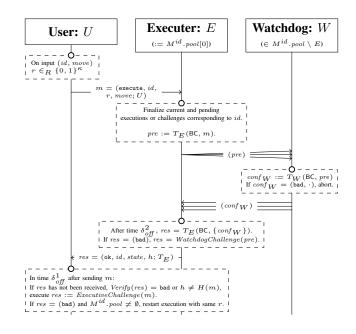

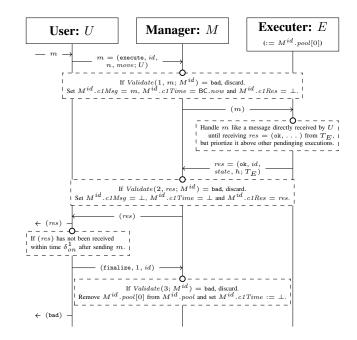

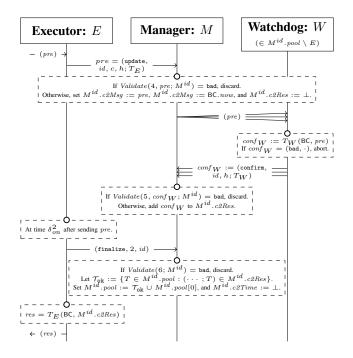

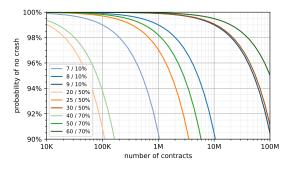

Originally envisioned as the world computer, the smart contract ecosystem of Ethereum and other blockchains still largely consists of simple token manager contracts. As blockchain interactions are costly and rather slow, a crucial research area in this field is speeding up smart contract execution by performing the computation off-chain. Pure protocol-based works in this area only work for simple coin transfers, require frequent blockchain interactions, depend on collateral, or only marginally improve execution speed. TEEs proved to be a viable way to alleviate these shortcomings, as a single TEE can already give correctness guarantees for smart contract execution. However, the missing availability guarantees of TEEs prevents prior approaches from guaranteeing the complete execution of the smart contract. With POSE, we design a novel TEE-based off-chain smart contract execution protocol that is the first to provide strong liveness guarantees, while achieving private state without relying on collateral. We designed and implemented a prototype for Ethereum based on Arm TrustZone. We show that POSE is practical by evaluating numerous smart contracts, e.g., federated learning and Poker, and by measuring the time to execute individual steps of the protocol.

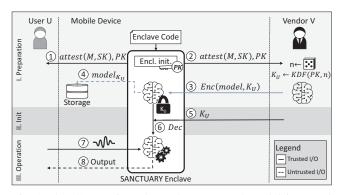

Another megatrend in computing is machine learning, especially artificial intelligence (AI), which is evolving quickly. As products increasingly rely on AI, machine learning models have become a high-value intellectual property for companies. Meanwhile, on the end-user device, privacy-sensitive user information is used to give personalized answers. Still, previous approaches for secure inference only addressed one of these aspects, incurred impractical requirements on the model, or had performance limitations. In OMG, we design a TEE-based protocol to protect both the machine learning model and the user's privacy. OMG leverages user-space enclaves to prevent model stealing attacks and protect sensitive user inputs. We implemented an offline wake word detection based on the TensorFlow lite for microcontrollers framework and the SANCTUARY enclave

architecture. We show that the machine learning inference protected within the strongly isolated exhibits unchanged accuracy and native inference speed.

Attack Surface Analysis with Fuzzing. Protecting blockchain and machine learning execution facilities with TEEs is effective and efficient. Yet, enclave code—same as regular applications—may contain vulnerabilities. Also, other components of the TCB may contain vulnerabilities. Hence, attack surface analysis is an essential cornerstone for modern security. In recent years, dynamic testing in the form of fuzzing has become increasingly popular. Fuzzers repeatedly execute a target, which can be software or even hardware, with random inputs and monitor the target for misbehavior or crashes. Fuzzing, in contrast to cumbersome manual approaches like unit testing, can test thousands of cases per second—from randomly generated inputs up to highly structured inputs, e.g., based on formal grammars. While initial research focused on technical advances to speed up the process and make targets fuzzable, current work also aims to optimize the fuzzer's internal algorithms to increase efficiency.

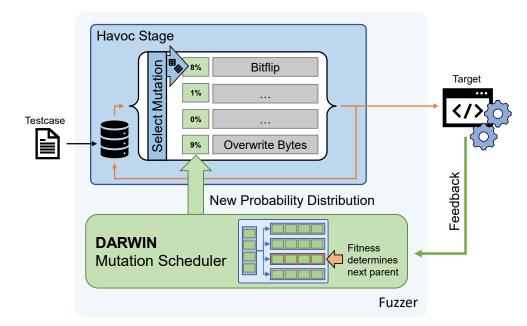

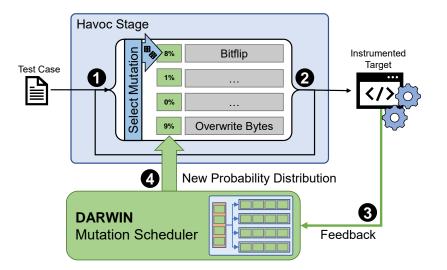

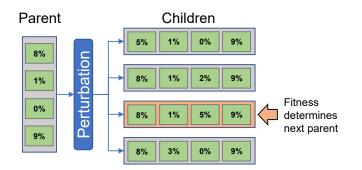

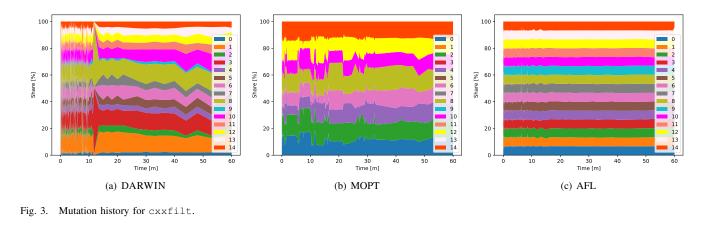

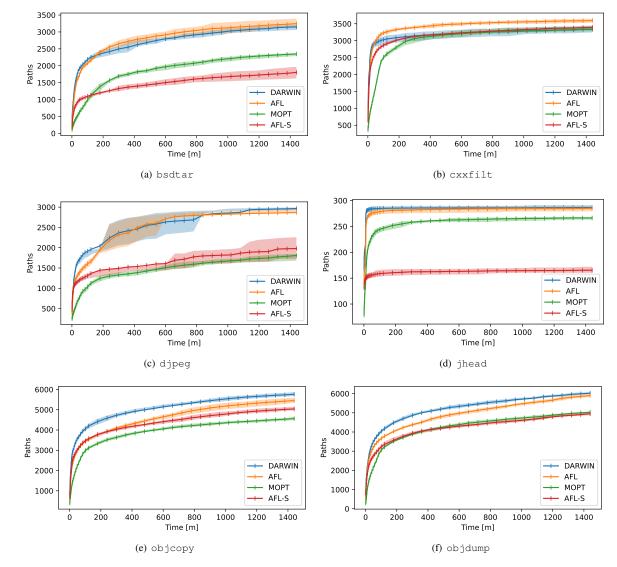

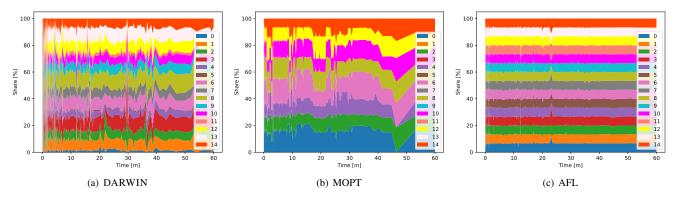

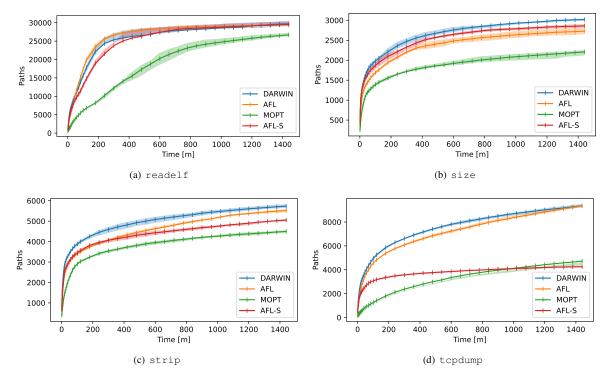

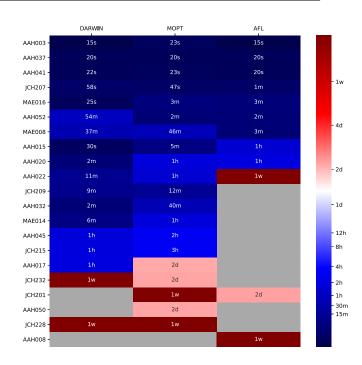

Lastly, in our work DARWIN, we propose a novel mutation scheduler for mutational fuzzing, designed for efficient and optimal selection of mutation operators with minimal performance impact on the fuzzing process. Further, DARWIN is straightforward to integrate into existing fuzzers and does not expose any target-dependent parameters. Thus, DARWIN can be integrated into most modern fuzzers. We show that DARWIN significantly improves time to coverage/bug while uncovering a completely novel bug in the extensively tested objcopy, which persisted for more than two decades.

# Zusammenfassung

In den letzten Jahrzehnten haben wir ein Wettrüsten zwischen Software-Angriffen und Abwehrmaßnahmen erlebt. Dieser ständige Kampf hat dazu geführt, dass moderne Computersysteme eine Vielzahl von Schutzmaßnahmen enthalten, die zusammenarbeiten, um sensible Anwendungen und Daten vor bösartigen Angriffen zu schützen. Trotz der zunehmenden Zahl von Sicherheitsmaßnahmen gibt es nach wie vor Schwachstellen, die oft auch die fortschrittlichsten Schutzmaßnahmen umgehen und ganze Systeme gefährden.

Aber wie können wir diesen unerbittlichen Kreislauf von Angriff und Verteidigung beenden? Ein entscheidender Aspekt, um das Problem systematisch anzugehen, ist die Reduzierung der Angriffsfläche (*Attack Surface Reduction*), d. h. die Reduzierung des Codes, der 1) für einen Angreifer erreichbar ist und 2) auch sensible Informationen erreichen kann.

Die Reduzierung der Angriffsfläche gilt nicht nur für den Code innerhalb einer Anwendung, sondern erstreckt sich auch auf den breiteren Software-Stack, einschließlich der Bibliotheken und des Betriebssystems, bei denen es sich um inhärent vertrauenswürdige Komponenten handelt, die oft als Trusted Computing Base (TCB) bezeichnet werden. Ein weiteres wichtiges Element ist die Analyse der Angriffsoberfläche (*Attack Surface Analysis*), mit der die Anfälligkeit eines Programms bewertet wird. Diese Analyse spielt eine entscheidende Rolle bei der Aufdeckung von Schwachstellen im gesamten Software-Stack, wodurch auch die Sicherheit kritischer Softwarekomponenten wie der TCB erhöht wird. Obwohl die Analyse der Angriffsoberfläche ein etabliertes Konzept ist, haben die jüngsten Fortschritte, insbesondere im Fuzzing-Bereich, den Weg für ihre allmähliche Integration durch die Industrie geebnet. Nichtsdestotrotz müssen noch zahlreiche Herausforderungen in diesem Bereich bewältigt werden, um sie zu einem integralen Bestandteil des Softwareentwicklungsprozesses der Industrie zu machen.

In dieser Dissertation entwerfen, implementieren und evaluieren wir 1) neuartige Architekturen zur Reduzierung der Angriffsfläche durch in-process Isolation und Enclaves, 2) Protokolle, die diese Architekturen als leistungsfähige Primitive nutzen, und 3) eine algorithmische Verbesserung des Fuzzing zur Analyse der Angriffsfläche.

Secure In-Process Compartments. Die in-process Isolation ist ein wichtiger Baustein für die Reduzierung der Angriffsfläche innerhalb einer Anwendung. Hierbei werden reguläre und sensible Daten voneinander getrennt. Bisherige Ansätze konzentrierten sich in erster Linie auf breit anwendbare Isolationsprimitiven, die es Entwicklern ermöglichen, ihre Anwendungen auf Kosten eines erheblichen Hardware- und Leistungs-Overheads zu isolieren.

In IMIX schlagen wir eine Befehlssatzerweiterung für die in-process Isolation vor, die ein hochfrequentes Domain Switching ermöglicht. IMIX ist ein minimal-invasiver Ansatz zur Reduzierung der Angriffsfläche für hochsensible Daten, so dass diese Daten nur vom dedizierten Teil des Anwendungscodes abgerufen werden können. Im Gegensatz zu modernen Randomization-Ansätzen sichert IMIX die Metadaten der Laufzeitverteidigung in einem Prozess deterministisch ab. In unserer Arbeit haben wir einen Prototyp von IMIX implementiert, um die Metadaten des Code Pointer Integrity Schemas mit minimalem Performance-Overhead zu schützen.

Flexible Enclaves for Application-driven Security. Während die in-process Isolation verschiedene Sicherheitsdomänen innerhalb einer Anwendung schaffen kann, ermöglicht TEEs die Ausführung der gesamten sensiblen Anwendung innerhalb eines isolierten Bereichs (einer so genannten Enclave), die dann weder Betriebssystem noch Hypervisor vertrauen muss. Traditionell bieten diese Enclave-Architekturen nur einen einzigen Enclave-Typ pro Plattform, was die Entwickler zwingt, die Anwendung an die Ausführungsumgebung der Enclave anzupassen. Dies vergrößert entweder die Angriffsfläche unnötig oder schränkt die Funktionalität der sensiblen Anwendung ein.

In CURE stellen wir das erste TEE zur flexiblen Reduzierung der Angriffsfläche auf der Grundlage der Anforderungen der sensiblen Anwendung vor. CURE nutzt ein System-Bus-Filtering, um verschiedene Typen von Enclaves zu kreieren, die eine flexible Ressourcenzuweisung pro Enclave für Peripheriegeräte und sogar DMA-Geräte ermöglichen. Wir implementieren einen Prototyp von CURE für die offene RISC-V-Architektur und evaluieren den Leistungs- und Hardwareflächen-Overhead auf einem FPGA- und Simulator-basierten Setup.

**Enclaves as Security Primitives in Protocols.** Während die Reduzierung der Angriffsfläche mit TEEs ein Eckpfeiler des modernen Softwareschutzes ist, können TEEs auch als Sicherheitsprimitiv genutzt werden, um leistungsstarke und effiziente Protokolle zu erstellen. In dieser Dissertation stellen wir TEE-basierte Protokolle für die Ausführung von Smart Contracts außerhalb der Blockchain und zum Schutz von Machine-Learning-Modellen vor.

Ursprünglich als Weltcomputer konzipiert, besteht das Smart-Contract-Ökosystem von Ethereum und anderen Blockchains immer noch weitgehend aus einfachen Token-Manager-Contracts. Da Blockchain-Interaktionen kostspielig und eher langsam sind, besteht ein wichtiger Forschungsbereich in diesem Bereich darin, die Ausführung von Smart Contracts zu beschleunigen, indem die Berechnungen außerhalb der Blockchain durchgeführt werden. Reine protokollbasierte Arbeiten in diesem Bereich funktionieren nur für einfache Coin Transfers, erfordern häufige Blockchain-Interaktionen, sind von einem Collateral abhängig oder verbessern die Ausführungsgeschwindigkeit nur geringfügig. TEEs haben sich als praktikabler Weg erwiesen, diese Mängel zu beheben, da ein einziges TEE bereits Korrektheitsgarantien für die Ausführung von Smart Contracts geben kann. Allerdings verhindern die fehlenden Availability-Garantien von TEEs, dass frühere Ansätze die vollständige Ausführung des Smart Contracts garantieren können. Mit POSE entwerfen wir ein neuartiges, auf TEEs basierendes Protokoll zur Ausführung von Smart Contracts außerhalb der Blockhain, das als erstes starke Liveness-Garantien bietet und gleichzeitig Private State bietet, ohne sich auf ein Collateral zu verlassen. Wir haben einen auf Arm TrustZone basierenden Prototyp für Ethereum entworfen und implementiert. Mit diesem zeigen wir, dass POSE praktikabel ist, indem wir zahlreiche Smart Contracts evaluieren, z. B. Federated Learning und Poker, und indem wir die Zeit zur Ausführung einzelner Schritte des Protokolls messen.

Ein weiterer Megatrend im Bereich der Datenverarbeitung ist das maschinelle Lernen (ML), insbesondere die künstliche Intelligenz (KI), die sich rasch weiterentwickelt. Da sich Produkte zunehmend auf KI stützen, sind die Modelle des maschinellen Lernens für die Unternehmen zu einem wertvollen geistigen Eigentum geworden. Gleichzeitig werden auf den Nutzer-Geräten datenschutzrelevante Benutzerinformationen verwendet, um personalisierte Antworten zu geben. Bisherige Ansätze für eine sichere Inference befassten sich jedoch nur mit einem dieser Aspekte, stellten unpraktische Anforderungen an das Modell oder wiesen Leistungseinschränkungen auf.

In OMG entwickeln wir ein TEE-basiertes Protokoll, das sowohl das ML Modell als auch die Privatsphäre des Benutzers schützt. OMG nutzt User-Space Enclaves um Model-Stealing-Angriffe zu verhindern und sensible Nutzereingaben zu schützen. Wir haben eine Offline-Wakeword-Erkennung implementiert, die auf dem TensorFlow Lite for Microcontrollers Framework und der SANCTUARY Enclave Architektur basiert. Wir zeigen, dass die ML Inference, die innerhalb der stark isolierten Enclave geschützt ist, eine unveränderte Genauigkeit und native Inference-Geschwindigkeit aufweist.

Attack Surface Analysis with Fuzzing. Der Schutz von Blockchain- und Machine-Learning-Ausführungsumgebungen mit TEEs ist effektiv und effizient. Dennoch kann der Enclave-Ccode - ebenso wie reguläre Anwendungen - Schwachstellen enthalten. Auch andere Komponenten der TCB können Schwachstellen enthalten. Daher ist die Analyse der Angriffsoberfläche ein wesentlicher Eckpfeiler für moderne Sicherheit. In den letzten Jahren wurde das dynamische Testen in Form von Fuzzing immer beliebter. Fuzzer führen ein Target, bei dem es sich um Software oder sogar Hardware handeln kann, wiederholt mit zufälligen Eingaben aus und überwachen das Target auf Fehlverhalten oder Abstürze. Im Gegensatz zu mühsamen manuellen Ansätzen wie Unit-Tests, kann Fuzzing Tausende von Fällen pro Sekunde testen - von zufällig generierten Eingaben bis hin zu stark strukturierten Eingaben, z. B. auf der Grundlage formaler Grammatiken. Während sich die anfängliche Forschung auf technische Fortschritte konzentrierte um den Prozess zu beschleunigen und Ziele fuzzbar zu machen, zielen neuere Ansätze auch darauf ab, die internen Algorithmen des Fuzzers zu optimieren, um die Effizienz zu

#### erhöhen.

Schließlich schlagen wir in unserer Arbeit, DARWIN, einen neuartigen Mutation-Scheduler für Mutations-basiertes Fuzzing vor, der für eine effiziente und optimale Auswahl von Mutationsoperatoren mit minimalen Leistungseinbußen auf den Fuzzing-Prozess entwickelt wurde. Darüber hinaus ist DARWIN einfach in bestehende Fuzzer zu integrieren und führt keine neuen Target-abhängigen Parameter ein. Daher kann DARWIN in die meisten modernen Fuzzern einfach integriert werden. Wir zeigen, dass DARWIN die Zeit bis zur Entdeckung eines Bugs erheblich verkürzt und gleichzeitig einen völlig neuen Bug in dem ausgiebig getesteten obj copy aufdeckt, der mehr als zwei Jahrzehnte lang bestehen blieb.

# Contributions

This dissertation is based on five scientific publications, which are the result of excellent collaboration with highly-experienced researchers and students, which I all thank for their valuable contributions. In the following, I outline my contributions to each publication included in this dissertation.

Chapter 2 is based on IMIX [70], a joint work with Tommaso Frassetto, Christopher Liebchen, and Ahmad-Reza Sadeghi. For IMIX, the design was a collaboration between Christopher Liebchen and me. I was the main author of the implementation, and integrated our solution in existing code for a use case. I also performed the performance evaluation. Tommaso contributed to the paper writing. This paper was developed in parallel with my master thesis [99]. While the thesis targets a simplified memory corruption defense as a use case, we extend the implementation to target the Code Pointer Integrity defense. Further, the paper contains newly implemented approximations for related hardware primitives and a new security analysis.

Chapter 3 is based on CURE [13], a joint work with Raad Bahmani, Ferdinand Brasser, Ghada Dessouky, Matthias Klimmek, Ahmad-Reza Sadeghi, and Emmanuel Stapf. Ghada Dessouky, Emmanuel Stapf and myself contributed to the discussions on the design and implementation that resulted in this publication. Emmanuel Stapf conceived the main idea and led the work, and supervised the M.Sc. thesis of co-author Matthias Klimmek whose work focused on the software stack implementation of the CURE architecture and its evaluation. I focused on the implementation of CURE's modifications at the processor and the software stack evaluation. Ghada Dessouky focused on the design, implementation, and evaluation of the cache partitioning for CURE. Emmanuel Stapf focused on the design of CURE's modifications at the processor, the design and implementation of CURE's access control mechanisms at the system bus, and led the evaluation. Raad Bahmani and Ferdinand Brasser contributed to the paper writing.

Chapter 4 is based on a joint works with Tommaso Frassetto, David Koisser, David Kretzler, Benjamin Schlosser, Sebastian Faust, and Ahmad-Reza Sadeghi, and with Sebastian P. Bayerl, Tommaso Frassetto, Korbinian Riedhammer, Ahmad-Reza Sadeghi, Thomas Schneider, Emmanuel Stapf, and Christian Weinert. For POSE [68], David Koisser, David Kretzler, Benjamin Schlosser, Tommaso Frassetto, and myself contributed to the discussions on the design that resulted in this publication. In detail, David Koisser, David Kretzler, and Benjamin Schlosser focused on the protocol, while I was responsible for the design of the off-chain execution environment. David Kretzler implemented the

on-chain manager contract, David Koisser the blockchain interaction, and I focused on the implementation of the system side of POSE and the corresponding evaluation of the off-chain smart contract execution. Benjamin Schlosser and David Kretzler proved the security properties of the protocol, while David Koisser and I analyzed the system's security guarantees. For OMG [17], Sebastian P. Bayerl, Tommaso Frassetto, Emmanuel Stapf, Christian Weinert, and myself contributed to the discussions on the design and implementation that resulted in this publication. I focused on the design of the communication protocol used by the SANCTUARY enclave, the user and the vendor of the machine learning model. Tommaso Frassetto focused on porting the TensorFlow Lite machine learning framework to SANCTUARY. Sebastian P. Bayerl focused on preparing the machine learning model and test data used during the evaluation of SANCTUARY. Emmanuel Stapf focused on the implementation of the keyword recognition algorithm in a SANCTUARY enclave and its evaluation. Christian Weinert contributed to the paper writing.

Chapter 6 is based on DARWIN [97], a joint work with Domagoj Jakobovic, Stjepan Picek, Emmanuel Stapf, and Ahmad-Reza Sadeghi. For DARWIN, Domagoj Jakobovic, Stjepan Picek, and myself contributed to the design of the mutation scheduler. I was the lead author of the design. Domagoj Jakobovic and I implemented the mutation scheduling algorithm, while I performed the evaluation of the prototype. Emmanuel Stapf contributed to the paper writing.

# Acknowledgements

This journey, now drawing to a close, has been shaped significantly by numerous people to whom I owe my deepest gratitude.

Foremost among them is my advisor, Prof. Ahmad-Reza Sadeghi. His unwavering commitment to excellence and his ability to inspire the best in me have been instrumental. His guidance granted me the freedom to explore my research while equipping me with the skills to present our findings in an understandable and concise way, not only in academia but also in numerous industry projects.

I also owe a debt of gratitude to my colleagues, many of whom have become dear friends over the years. Special thanks are due to Ferdinand and Emmanuel, who made my dream of starting a company a reality. I am equally grateful to Tommaso and David, my constant companions in both scientific and personal discussions.

My research projects would not have been possible without the collaboration and insights of my co-authors. Thus, my thanks go to all my colleagues from the System Security Lab and external collaborators. Additionally, I am thankful to Prof. Asokan for graciously accepting the role of my second doctoral referee. My appreciation also goes to the rest of the defense committee members – Prof. Carsten Binnig, Prof. Sebastian Faust, and Prof. Marco Zimmerling – for their engaging and thought-provoking discussions during my dissertation defense.

I must also extend my heartfelt gratitude to my friends, whose constant presence and support played a crucial role in my journey. Their understanding and compassion provided solace during the most challenging times, making this journey more bearable.

Last but certainly not least, I must express my heartfelt thanks to my family, whose unwavering support made it possible for me to pursue this academic path. A special thanks goes to Maren, who endured many missed evenings, weekends, and vacation days to support my journey. Your sacrifice and support have been crucial in bringing this chapter of my life to a successful conclusion.

# Contents

| 1 | Introduction                                                           | 1   |

|---|------------------------------------------------------------------------|-----|

|   | 1.1 Attack Surface Reduction                                           | 2   |

|   | 1.2 Attack Surface Analysis                                            | 4   |

|   | 1.3 Dissertation Outline                                               | 5   |

| 2 | Secure In-Process Compartments                                         | 7   |

|   | 2.1 Our Contributions                                                  | 8   |

|   | 2.2 Related Work                                                       | 10  |

| 3 | Flexible Enclaves for Application-driven Security                      | 13  |

|   | 3.1 Our Contributions                                                  | 14  |

|   | 3.2 Related Work                                                       | 17  |

| 4 | Enclaves as Security Primitives in Protocols                           | 21  |

|   | 4.1 Efficient Off-Chain Smart Contracts                                | 21  |

|   | 4.2 Private and Secure Offline Machine Learning                        | 24  |

|   | 4.3 Related Work                                                       | 27  |

| 5 | Attack Surface Analysis with Fuzzing                                   | 31  |

|   | 5.1 Our Contributions                                                  | 32  |

|   | 5.2 Related Work                                                       | 34  |

| 6 | Conclusion & Outlook                                                   | 37  |

|   | 6.1 Conclusion                                                         | 37  |

|   | 6.2 Outlook                                                            | 38  |

| 7 | List of Own Publications                                               | 41  |

|   | 7.1 Peer-Reviewed Publications                                         | 41  |

|   | 7.2 Invited Publications & Technical Reports                           | 43  |

|   | 7.3 Magazine Articles & Books                                          | 43  |

|   | 7.4 Posters                                                            | 44  |

|   | Bibliography                                                           | 45  |

|   | Lists                                                                  | 68  |

|   | Appendices                                                             | 71  |

| A | IMIX: In-Process Memory Isolation EXtension                            | 73  |

| В | CURE: A Security Architecture with CUstomizable and Resilient Enclaves | 91  |

| С | POSE: Practical Off-chain Smart Contract Execution                     | 111 |

### XVIII CONTENTS

| D | OFFLINE MODEL GUARD: Secure and Private ML on Mobile Devices | 131 |

|---|--------------------------------------------------------------|-----|

| Ε | DARWIN: Survival of the Fittest Fuzzing Mutators             | 139 |

# Introduction

Over the last decades, computers evolved from specialized experimental equipment to the cornerstone of our digital society. New chip designs and vastly improved manufacturing capabilities allowed computer systems to be integrated into every aspect of our lives. To meet the demands of this widespread integration, software development has been in a constant state of evolution, introducing new and complex features at an unprecedented rate. Consequently, code bases have ballooned in size—the Linux kernel, for instance, has roughly doubled its size over the last ten years [152, 113], and it now comprises over 35 million lines of code [183]. However, application software like web browsers has already overtaken Linux [92]. This rapid expansion in software features contributed to an explosion of reported vulnerabilities [219], including catastrophic security flaws [134, 182] that deeply shattered the trust in the computer software.

A significant contributor to today's software security challenges is the prevalence of historically grown, legacy code, often written in memory-unsafe languages such as C and C++. These memory-unsafe languages put the security burden entirely on the developer, as they 1) require active lifecycle management of objects in memory and 2) allow the developer to manipulate references to memory (pointer arithmetic) liberally. Unsurprisingly, these practices have led to a surge in memory-corruption vulnerabilities: memory safety violations that can be exploited to hijack the control flow of an application. Alarmingly, despite the availability of modern, memory-safe programming languages like Rust [105], new memory-unsafe code continues to be written [175], sustaining the cycle of vulnerability creation. Thus, programming errors that lead to memory-corruption vulnerabilities remain a persistent and critical issue in the software landscape [133].

Fortunately, both academic research and industry have not been idle; they have developed a plethora of defenses, commonly known as *mitigations*, aimed at curtailing the impact of these vulnerabilities. Broadly, these mitigations can be classified into two categories: integrity-based and randomization-based approaches. The former ensures the integrity of the control flow, e.g., by comparing each control-flow transition against precomputed ground truths [3, 31, 69], or by ensuring the integrity of high-value data like code pointers and other program structures [112, 32, 216]. Recently, these mitigations have been implemented as hardware primitives to be used by software [120, 122, 121, 168], which further reduces the mitigations' attack surface towards a software adversary.

#### 2 INTRODUCTION

However, these methods often hinge on dedicated metadata for ensuring data integrity, e.g., to compare a potentially tampered code pointer to a backup in the metadata structure. This creates a potential weak point: if this metadata is compromised, the mitigation can be entirely subverted [36, 65, 112].

In contrast, randomization-based approaches leverage the high entropy of virtual address spaces to shuffle the memory layout [23, 47, 27, 50]. Thus, to successfully exploit a vulnerability, an adversary needs to reverse this randomization to find the address of valuable data, e.g., using an information leak [172]. Indeed, many deployed mitigations have been bypassed [172, 46, 65, 166, 212, 12, 18, 45], making memory-corruption vulnerabilities remain an important attack vector in practice.

To finally address the problem at hand systematically, two factors are critical: 1) clear attack surface reduction, where a large proportion of the legacy software's dependencies (e.g., libraries or its execution environment) cannot affect the security of sensitive code anymore, and 2) more advanced ways to analyze the attack surface to assess the remaining risk for vulnerabilities within the code.

In this dissertation, we not only explore advances in attack surface reduction and analysis techniques but also how attack surface reduction primitives can help to construct efficient and powerful protocols.

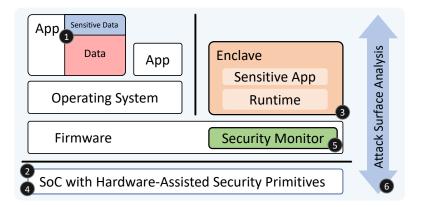

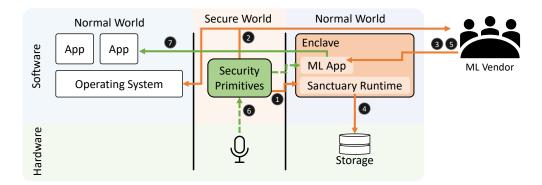

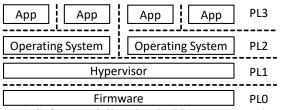

Figure 1: High-level overview of the complex software stack on a modern system.

### 1.1 Attack Surface Reduction

Attack surface refers to all the entry points that the software exposes which can potentially be leveraged by an adversary to attack a target. However, knowing which part of the software belongs to the attack surface is highly challenging as it requires a deep understanding of the software architecture, design, and functionality. In addition, the software, and hence, also the attack surface, is not static but can change over time due to updates. Hence, defensive measures need to concentrate on the highly sensitive parts of the software. Guarding these sensitive parts, such that an adversary cannot reach them, is what compartmentalization and trusted execution environments address.

#### **In-Process Compartmentalization**

Memory corruption attacks remain a significant issue in computer security, despite the use of various preventive measures such as safe programming languages, static and dynamic analysis, and run-time defenses (also called mitigations). Especially the latter has been subject to extensive research. These run-time defenses can be broadly classified into randomization-based and integrity-based approaches. Randomization-based approaches seek to obscure the location of critical code or data blocks in an application by randomly rearranging or hiding them within the virtual address space of the application. While this can be effective in some cases, it is ultimately a probabilistic defense that can be bypassed with enough tries or if an attacker can discover information leaks that reveal the location of these blocks [172].

Instead, integrity-based approaches aim to enforce an application's correct behavior, e.g., by verifying the integrity of code pointers or checking for valid control-flow transitions. These approaches are often more robust against information leaks, yet may require more coarse-grained checks to maintain an acceptable performance overhead. However, most integrity-based techniques rely on metadata to ensure the integrity of code or data blocks. As memory-corruption adversaries are commonly assumed to have full read and write access to the application's memory (except code pages which are nowadays protected by execute-only permissions), the metadata is also at risk. Once this metadata is corrupted, the defense is broken entirely.

Protecting this metadata is challenging, as integrity-based approaches must frequently access this data. While hiding the metadata in virtual memory is fast, information leaks or brute-force attacks endanger the security of the integrity scheme [65]. As shown in Figure 1, secure compartments 1 can prevent illegal access to this metadata deterministically (opposed to probabilistic protection of randomization), either as pure software-based approaches [193, 167, 23, 108], or leveraging hardware primitives. Indeed, several hardware-assisted compartments 2 are already available in practice, most notably Intel MPX [144] for bounds checking, Arm Memory Domains [217] (not available anymore in recent architectures) and Memory Protection Keys (MPK) [104] for creating memory domains with dedicated access rights. However, these approaches do not support frequent switching between the different memory domains they create [108], e.g., between regular code and mitigation code. Recently, Intel introduced Control-flow Enforcement Technology (CET) [169], which aims to address this by adding hardware support for indirect branch tracking (to implement CFI checks) and a shadow stack, which adds hardware instructions to create and verify backups of the return addresses on the stack. However, this mechanism is only designed for shadow stacks. Hence, CET is not flexible enough to safeguard other mitigations.

#### **Trusted Execution Environments**

While in-process compartmentalization helps to better protect individual applications from compromises, each application must be protected individually. If only one application is compromised, the large attack surface of the operating system (OS) and third-party device drivers create a significant risk for other applications. Further, e.g., in cloud scenarios, customers might not trust the cloud vendor's hypervisor and fear direct attacks or side-channel leakage to other tenants.

To address this growing problem, sensitive applications' attack surface must be reduced tremendously. One promising technology for achieving this is Trusted Execution Environment (TEE), also called enclave architectures. TEEs provide strongly isolated compartments (a), known as enclaves, which protect sensitive applications, i.e., sensitive parts of an application, from other applications and privileged software such as the OS and the hypervisor. This isolation is enforced by hardware primitives (a) configured by a small trusted software (b), often called the security monitor. TEEs offer a promising approach to enhance the security of sensitive applications by reducing their attack surface and providing more robust protection against malicious attacks. TEEs are available on many commercial CPUs already, e.g., Arm TrustZone-A [9] and TrustZone-M [210], Arm Confidential Compute Architecture [128], Intel Software Guard Extensions (SGX) [94, 48] and Trust Domain Extensions (TDX) [93], AMD Secure Encrypted Virtualization (SEV) [102, 6, 103, 7], or IBM Protected Execution Facility [86]. However, most of these architectures were already bypassed to leak secrets from enclaves [213, 190, 137, 191].

**Enclave Applications.** Enclaves are a simple and effective way to protect an application from the large attack surface of a regular system. They have been used for this purpose in various scenarios, such as databases, digital rights management, and software containers. In addition to their use as single-purpose high-security vaults, enclaves also serve as powerful security primitives that can be integrated into higher-level protocols to improve security, performance, and scalability. However, TEEs are not a foolproof technology and do neither guarantee availability for the service in an enclave, nor the confidentiality or timeliness for communication between enclaves and external services (e.g., network or filesystem). As a result, designing protocols for applications in scenarios such as blockchain is highly challenging.

### **1.2** Attack Surface Analysis

Enhancing the security of sensitive applications often involves the use of isolation mechanisms like enclaves to shield them from external threats. However, the isolation enforced by the enclave's enclave architecture is not a panacea; both the trusted software components of the enclave architecture and the sensitive applications it hosts could contain vulnerabilities. Given these complexities, the dual strategies of attack surface reduction and attack surface analysis become even more critical. Attack surface reduction serves to minimize the avenues through which an adversary could compromise a system, thereby reducing the risk profile of both enclaves and the applications they safeguard. Conversely, attack surface analysis provides a vital complement by systematically identifying residual vulnerabilities and potential entry points ③, including those within the enclave-protected applications themselves. Importantly, this exhaustive scrutiny needs to extend beyond applications to encompass all layers of the computational stack: enclaves, operating systems, hypervisors, firmware, security monitors, and even hardware.

While traditional approaches for attack surface analysis require extensive labor, e.g., in the form of manual writing of unit tests, modern approaches can reduce the effort tremendously by exhaustive automatic analysis. Automatic analysis has two main research directions: static analysis and dynamic analysis. Static analysis extends the compilation process to look for error-prone programming patterns or basic memory mismanagement. However, static analysis does not scale well: it operates on a symbolic representation of the code, requiring the evaluation of every branch under every possible value range within the input domain. Dynamic analysis, in contrast, executes the program directly to find bugs. Recently, fuzzing has emerged as a popular research direction in this area. Fuzzing tests the target program by repeatedly running it with randomly generated inputs. If the target program crashes, a bug has been found. While initially developed for regular applications [74], fuzzing is now used within all software privilege layers and even for testing hardware designs [188, 37].

### **1.3 Dissertation Outline**

In the following, we give a brief outline of the remainder of this dissertation, whereby each chapter presents the respective publication in more detail and situates the publication within the broader context of relevant literature.

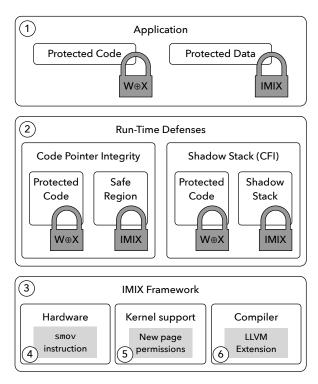

**Chapter 2:** We present IMIX, a novel lightweight intra-process isolation design where memory pages are tagged as security-sensitive, while a specialized instruction in the instruction set architecture (ISA) provides exclusive access to these pages. While IMIX can protect arbitrary sensitive data, IMIX is designed to efficiently safeguard the metadata associated with memory-corruption defenses.

**Chapter 3:** We introduce CURE, the first Trusted Execution Environment (TEE) architecture designed that provides multiple types of enclaves at once, offering a level of flexibility that allows adaptation to the unique requirements of sensitive applications. Additionally, CURE introduces fine-grained resource management capabilities to ensure that enclave resource demands are met without expanding the attack surface unnecessarily.

#### 6 INTRODUCTION

**Chapter 4:** We present POSE and OMG, protocols that harness the power of Trusted Execution Environments (TEEs) to improve security guarantees and performance for blockchain and AI applications. POSE, an off-chain smart contract execution protocol, offers strong liveness guarantees while ensuring private state without collateral requirements. Furthermore, POSE accelerates smart contract execution, enabling modern use cases such as machine learning integration.

Offline Model Guard (OMG), on the other hand, presents a secure and private machine learning approach, even in offline scenarios. OMG leverages TEEs to establish strict isolation between models and users, with additional support for hardware-based machine-learning accelerators.

**Chapter 5:** We introduce DARWIN, a lightweight mutation scheduler for fuzzing based on the Evolution Strategy algorithm. DARWIN optimizes the mutation-selection probability distribution throughout the fuzzing process, utilizing coverage feedback as a fitness function. In contrast to existing approaches, DARWIN improves coverage and bug-finding capabilities while avoiding the introduction of new per-target parameters that necessitate manual tuning.

# Secure In-Process Compartments

As mentioned in Chapter 1, an adversary can exploit memory-corruption vulnerabilities to gain arbitrary code execution within an application at run time (commonly referred to as a *process*). This can be done by manipulating memory locations to either inject new code, reuse existing code, or perform so-called data-only attacks. Code-injection attacks add new, malicious code to the process, while code-reuse attacks recombine existing code of the process to perform arbitrary computations. Data-only attacks try to steer the control flow by modifying data variables, e.g., used to determine branches, within the existing control-flow graph. Research has shown that even data-only attacks can perform arbitrary computations [96].

Thus, code must be hardened against such attacks by integrating defenses to guard (control) data. The most straightforward attack, code injection, can effectively be prevented by enforcing that a memory page can either be writable or executable, but not both ( $W \oplus X$ ). This prevents injected code from being executed and is indeed used in practice since 2004 [178]. Yet, code-reuse and data-only attacks are still possible, and hence, countless software defenses emerged to prevent these attacks, e.g., shadow stacks [32], Code Pointer Integrity (CPI) [112], or various forms of Control-Flow Integrity (CFI) [3, 46, 31, 69]. However, these defenses can be the target of an adversary themselves, especially as they need to store their own metadata in the same address space. This metadata is crucial for a working mitigation, and an adversary can manipulate this data to bypass a mitigation [65, 32]. While storing the metadata in another process or privilege layer (e.g., in the kernel) seems appealing, software defenses require frequent access to the metadata, e.g., for every code pointer load, and switching between these contexts is slow [108]. Hence, this metadata is usually hidden in the process's virtual address space by exploiting the larger entropy of today's 64-bit systems. Unfortunately, a single information leak (register spilling, brute-force guessing) has been shown to be enough to break this approach completely [172, 65].

Therefore, a deterministic isolation approach, as opposed to probabilistic randomization schemes, is needed. One important primitive that emerged to secure such metadata is intra-process isolation. Intra-process isolation creates an isolated compartment ("safe region") within the process that can only be accessed when in a specific context, e.g., when a return address is stored to/loaded from the shadow stack.

Intra-process isolation is a crucial building block for securing memory-corruption defenses. Designing such a scheme is challenging due to the wide-ranging requirements, namely, the approach must...

- 1. protect a safe region deterministically,

- 2. be easy to integrate into existing applications or memory-corruption defenses, ideally without changing the source code,

- 3. induce very little performance overhead (as this is on top of the defenses' performance overhead),

- 4. leverage an isolation primitive that supports frequent invocations, e.g., for every code pointer dereference.

### 2.1 Our Contributions

This thesis addresses these requirements on intra-process isolation with the following publication, which can be found in Appendix A.

[70] Tommaso Frassetto, Patrick Jauernig, Christopher Liebchen, and Ahmad-Reza Sadeghi. IMIX: In-Process Memory Isolation EXtension. In 27th USENIX Security Symposium, USENIX Security 2018, Baltimore, MD, USA, August 15-17, 2018, pages 83–97. USENIX Association, 2018. CORE Rank A\*. Appendix A.

With IMIX, we propose a novel lightweight intra-process isolation primitive that marks memory pages as security sensitive, which can only be accessed with our newly added instruction in the Instruction Set Architecture (ISA). This efficiently protects the metadata of memory-corruption defenses. Yet, the design of IMIX is not tailored towards a specific memory-corruption defense or ISA. In the following, we provide a more detailed summary of our approach.

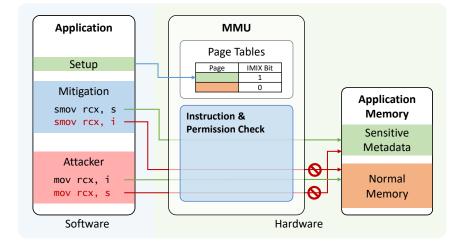

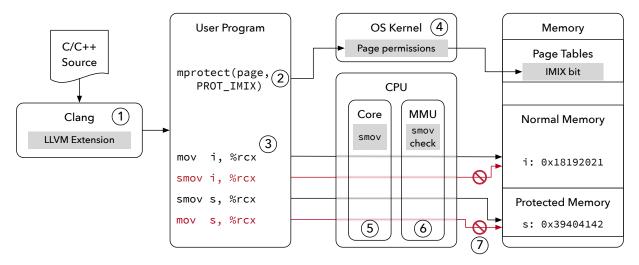

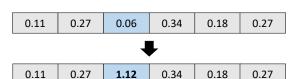

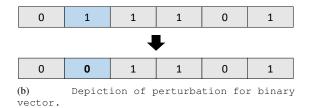

**IMIX.** As shown in Figure 2, IMIX introduces a new permission bit to mark pages as isolated, i.e., belonging to the safe region. This permission bit is similar to the bit flags for read/write/execute. We further added support for IMIX in the kernel, which allows developers to mark a safe region using existing memory management functionality. If an application wants to leverage IMIX to guard a sensitive region, it first has to mark the region as sensitive. On Linux, this would be done with the mmap system call.

Figure 2: High-level overview of IMIX

Further, IMIX adds a new instruction to the ISA, smov, which is a pendant to the regular move instructions. This smov instruction encodes the security-sensitive context, such that only smov instructions can access the safe regions (but not the remaining memory, which prevents data-flow attacks on smov instructions originating from normal memory). Analogously, regular mov instructions can access all normal memory except safe regions. Hence, the application has to ensure that only code belonging to the sensitive region uses the smov instruction, while all other code should use a regular mov instruction. To simplify this, IMIX provides a compiler pass that can be leveraged by mitigations that want to protect their metadata, or by application developers themselves.

**Implementation.** We implemented a prototype of IMIX for x86-64. For every memory page, we maintain a flag in the Page Table Entry belonging to the page to indicate whether it belongs to the safe region. We further extended the Memory Management Unit of the CPU to check whether the current instruction accessing the memory was a smov instruction, and if the flag in the Page Table Entry is set. We implemented this CPU extension in the Windriver Simics simulation framework [1], which enables instrumentation on off-the-shelf Intel CPU designs.

We further extended the Linux kernel to integrate the IMIX permission bits in the memory management functions (e.g., mmap).

For application-side support, we implemented an LLVM-based compiler pass. The compiler pass can emit smov instructions by directly invoking IMIX library functions or by inserting source code annotations. We further implemented a use case based on CPI [112] and modified the code to use smov instructions for storing/loading metadata.

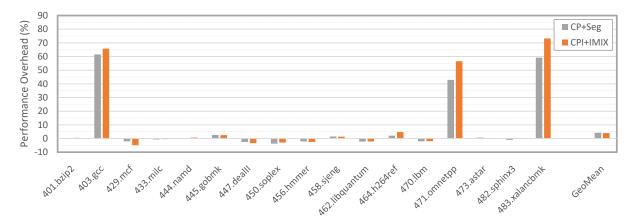

We evaluated CPI using the standard SPEC CPU2006 benchmark suite and compared its performance to plain CPI with direct memory access and randomization-based CPI, i.e., segment-offset-based access. The original memory-hiding-based CPI implementation induced a 4.24% performance overhead (geometric mean), while the IMIX variant induces a 3.99% performance overhead. We further implemented a CPI variant that uses an approximation [108] of Intel's MPK. This variant induced an overhead of 12.43%, showing MPK's shortcomings in high-frequency domain changes.

### 2.2 Related Work

**Retrofitting Existing Isolation Features.** Building an intra-process isolation primitive out of existing hardware features is appealing, as they are available on off-the-shelf hardware. However, approaches leveraging existing hardware functionality often need to work around a caveat of that specific feature—either due to different performance goals (e.g., not made for frequent domain switching) or due to non-optimal requirements (e.g., privileges) of the primitive. This results in additional software components like instruction filters or call gates that require protection themselves.

One research direction leverages the Memory Management Unit (MMU) to implement different views on memory. Software-fault Isolation (SFI) techniques [193, 167, 55, 23] reserve a part of the virtual address space for the safe region and apply offsets to allowed instructions automatically. However, they reduce the available virtual address space. Other SFI approaches leverage hardware-based bounds checking [35, 108] to avoid virtual address space reduction, but do not support frequent switching [144, 108]. Another approach is to use different virtual address spaces for different execution contexts (like for safe regions) [124], however, these techniques do not protect from overflows into the safe region [35]. IMIX checks permissions for mov and smov instructions such that neither can overflow into the other respective region while keeping the whole virtual address space available and enabling fast and frequent domain switching.

A different line of research uses protection keys for user space to design intra-process isolation schemes [217, 108, 189, 83, 149, 165, 207, 53]. Protection Keys for Userspace (PKU) are , e.g., available on recent Intel x86 processors, where the feature is called Intel Memory Protection Keys (MPK). While we will focus on MPK as a representative of general protection key schemes here, other implementations exist, e.g., on older Arm processors [217, 40]. MPK enables developers to assign memory pages to a set of memory domains. Subsequent memory accesses are only possible if the instruction executing is in an allowed domain. Entering this domain is done by setting a dedicated user space register. However, MPK is not designed for frequent switches: for each sensitive data access, the code needs to read the domain register, change the domain register, perform the access, and restore the domain register [108].

In addition, all unprivileged code can tamper with page permissions in the MPK register [189]. Hence, MPK instructions not originating from the intra-process isolation need to be filtered out, as, e.g., proposed in ERIM [189] and HODOR [83]. This 1) is dangerous as parsers are prone to memory-corruption errors themselves, 2) requires ensuring that another process cannot indirectly tamper with the registers through the kernel interfaces, and 3) requires that the filtering step is exhaustive as a single remaining MPK domain change instruction could be used as a primitive by an adversary to break the scheme. In fact, exhaustive filtering is nearly impossible on x86 due to unaligned instructions and has been circumvented [45, 200]. Eliminating the filtering step is not possible for MPK due to the direct user space register access. Further, these approaches need to apply various optimizations to reduce the MPK invocations for a practical performance overhead. Both problems hinder their adoption, especially in JIT engines (just-in-time compilers). Donky [165] does not rely on MPK, and hence, avoids the user space access problems but also has more PKU interactions than, e.g., ERIM. IMIX avoids all these problems 1) by preventing permission changes to safe regions after they have been set up and 2) by allowing fast, frequent domain switching.

**Hardware-based Capability Systems.** Capability systems [202, 58, 173] extend the hardware to enable complex memory-access policies. This is commonly done by augmenting the memory resource (granularity can vary among the approaches) with dedicated tag bits, similar to the domain concept in MPK. A particularly flexible approach is CHERI [202], an ISA extension that adds a new hardware data type to support secure pointer manipulation while providing fine-grained memory protection and access control. The CHERI system relies on software policies to express the allowed memory resources (bounds and permissions) referenced by each pointer. To fully realize the benefits of CHERI, extensive software support is required at various levels, including the operating system, compiler, language runtime, and applications, as well as the underlying microarchitecture for check enforcement.

Similarly, HDFI [173] augments the MMU with an additional tag table to realize finegrained memory access policies. However, this approach requires reading the tag table for each memory read/write, and hence, needs additional hardware units (e.g., caches) to reduce the performance impact.

Finally, PUMP [58] proposes another tag-based capability system but extends all data units to fit the tag directly in the unit itself, avoiding the additional tag table read. While PUMP is a promising approach for enforcing security policies, it also introduces a significant hardware area overhead of around 110%.

However, these systems cannot easily support safe regions for mitigations, as their complex access control prevents frequent domain switches [135], and, unlike IMIX, these approaches are not fail-safe, i.e., uninstrumented code can bypass these policies [218].

PHMon [54] is another approach that uses a programmable hardware monitor to enforce rule-based security policies at run time. PHMon's rules cover the entire predefined architectural state of the processor, including the current instruction, used data, and program counter. PHMon is directly connected to the processor pipeline and receives traces of the processor's architectural state, which are compared against the defined rules. If a violation is detected, an interrupt is triggered.

Yet, PHMon is a reactive approach as it relies on the processor trace and can only detect an attack after it has happened. In practice, this can be enough to escape the actual monitored application and invoke unintended but benign-looking functionality. IMIX already prevents the actual data reads, making it a proactive solution with minimal hardware changes.

# Flexible Enclaves for Application-driven Security

Today, the software stack of a computer system typically comprises an operating system (OS), libraries, runtimes, and a plethora of different services and applications from numerous vendors and open-source projects. A single vulnerability in one of these software components could compromise highly sensitive applications like payment wallets, digital rights management services, or even the whole system. As strong isolation between all software components is not feasible due to their interaction, at least the sensitive applications need to be protected from the rest of the system. This is a traditional application for Trusted Execution Environments (TEEs), sometimes also referred to as enclave architectures, where a security-sensitive application is protected from the remaining software stack within a so-called enclave. While isolating a service with a TEE appears to be a trivial solution for this problem, the diversity of today's software components creates a tremendous challenge. Each sensitive application has unique requirements on features and resources, e.g., communicating with a peripheral securely (like the fingerprint sensor in a phone), multi-process computation with inter-process communication, or integrity- and confidentiality-protected file accesses. Enclaves can leverage the regular operating system to fulfill these requirements, but this directly contradicts the idea of not trusting the other software components on the system.

Fortunately, these unique requirements of sensitive applications have already been studied extensively, and numerous enclave architectures have been proposed to handle a particular type of service and its usual requirements—based on what the enclave architecture designer deemed relevant.

In practice, three major types of enclaves can be used to protect a sensitive application, but usually, only a single enclave type is provided by the TEE. User space enclaves isolate individual user processes, which keeps the enclave's attack surface small by omitting unneeded software components like an operating system. However, this also prevents the application from performing more complex tasks, e.g., accessing peripherals, as there is simply no design feature to allow drivers to run within an enclave. Another type of enclave architecture isolates not only a user process but an additional runtime or kernel (which is then called a kernel-space enclave). While this enables a sensitive application to interact with devices like machine-learning accelerators directly, having a kernel inside an enclave creates a lot of security and management overhead for simple applications. Also, other OS components are now part of the attack surface and need to be updated regularly.

Finally, virtual machine (VM) enclaves, the enclave type found in current-generation commercial TEEs like AMD SEV, isolate whole virtual machines. However, these isolated VMs then depend on services the untrusted hypervisor provides. Typically, these TEEs cannot establish direct secure communication between an enclave and a peripheral.

While there are workarounds for each enclave architecture to emulate one of the other enclave types to offer more enclave types on a single platform, these approaches retrofit tremendous additional software (security) features [10, 170, 187]. This increases the complexity and size of the sensitive application and also forces the developer to be aware of these security features and the associated threat model. For instance, user space enclaves can access the filesystems when leveraging workarounds like Scone [10]. However, then, they rely on OS services, making them susceptible to side-channel/controlled-channel attacks from the OS [145]. So as in the original case of the three basic enclave types, this leaves the burden on the sensitive application developer—the sensitive application has to be adapted to the TEE, not the TEE to the requirements of the sensitive application.

To address this problem holistically, an enclave architecture needs to address several challenges, namely, the approach...

- 1. must be flexible, i.e., offer enclave types that meet the sensitive application's requirements,

- 2. must offer the secure use of peripheral devices to support modern use cases like machine learning,

- 3. has to protect the sensitive application against sophisticated attacks,

- 4. while keeping the enclave runtime minimal.

### 3.1 Our Contributions

This thesis addresses these requirements on practical enclave architectures with the following publication, which can be found in Appendix B.

[13] Raad Bahmani, Ferdinand Brasser, Ghada Dessouky, Patrick Jauernig, Matthias Klimmek, A. Sadeghi, and Emmanuel Stapf. CURE: A Security Architecture with CUstomizable and Resilient Enclaves. In *30th USENIX Security Symposium (USENIX Security 21)*, 2021. CORE Rank A\*. Appendix B. CURE is a novel TEE architecture for high-performance RISC-V systems that is the first to provide multiple types of enclaves. CURE offers strong and flexible isolation that adapts to the sensitive application, not vice versa. Further, CURE enables fine-grained resource management to meet enclave resource requirements without increasing the attack surface unnecessarily. Finally, CURE protects against cache side channels and controlled-channel attacks.

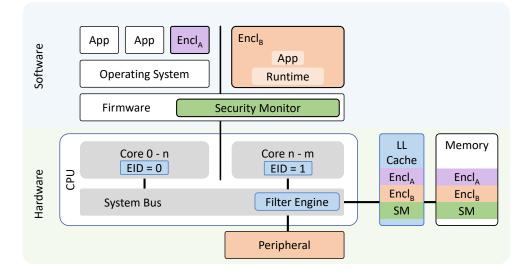

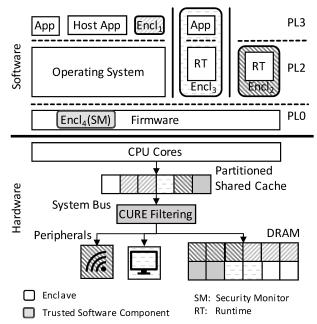

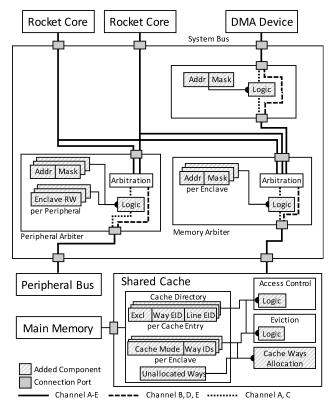

Figure 3: High-level overview of CURE. New or modified hardware components are shown in blue, the software TCB is marked green.

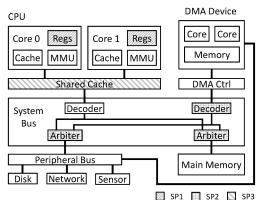

**CURE.** The key idea of CURE, as depicted in Figure 3, is to control access directly on the memory subsystem's central part: the system bus. This is the central point where memory transactions from the CPU or peripherals are routed toward the DRAM, other MMIO-mapped peripherals, or DMA devices. CURE augments the system bus by adding a Filter Engine, which comprises new access-control mechanisms for the system bus at its arbiters and decoders (the ports to the respective child components). These access-control mechanisms maintain permission tables indexed by the address range and the current enclave ID. Every memory transaction is then augmented with an enclave ID such that the Filter Engine can look up the individual permissions per transaction. This enclave ID originates from a per-core CPU register indicating the current enclave execution context. In addition, CURE introduces a new privileged software component, the Security Monitor, to configure the enclave ID and manage the Filter Engine's permission tables.

This unique hardware design enables CURE to support flexible but strongly isolated enclaves. CURE can provide different types of enclaves based on the requirements of the sensitive application: user space, kernel space, or sub-space enclaves. User space enclaves are ideal for smaller workloads that do not need peripherals or rich standard libraries to work, thus profiting from a small TCB. CURE also effectively mitigates pageor interrupt-based controlled-channel attacks. While the OS still provides services to the user-space enclave, CURE prevents controlled-channel attacks 1) by allowing the enclave to register its own interrupt handler to detect attacks, and 2) by moving the corresponding page tables inside enclave memory. For more complex workloads, kernel space enclaves can be used. Kernel space enclaves comprise the sensitive application itself and a runtime, e.g., a kernel. This allows kernel space enclaves to contain drivers that can be used with peripherals. As CURE's Filter Engine also manages permissions for peripherals and Direct Memory Access (DMA) regions, CURE can enable direct enclave-to-peripheral bindings without requiring any changes in the peripheral. This allows kernel space enclaves to support modern workloads that, e.g., outsource machine learning to dedicated hardware accelerators. Finally, CURE supports sub-space enclaves, which isolate only a part of a sensitive application at the same privilege level. This enclave can be used to create lightweight digital rights management solutions right in the sensitive application. For CURE, a sub-space enclave is used to reduce the TEE by separating the Security Monitor from the firmware.

**Implementation.** We implemented a prototype of the CURE hardware extension on RISC-V using Rocket Chip, a state-of-the-art open-source RISC-V System-on-Chip (Soc) design. We extended the TileLink A and C channels to include the enclave ID signal, added a CSR register in the core, and added the Filter Engine in the system bus, where we memory-mapped the permission tables to make them configurable from software. Finally, we implemented a way-based partitioned last-level cache to prevent cache side-channel attacks.

We further implemented CURE's software part by 1) developing a Security Monitor to control the hardware, 2) adding a kernel module to the Linux kernel to handle enclave creation requests, and 3) creating a runtime for kernel space enclaves based on Linux.

The hardware overhead was evaluated by synthesizing our CURE hardware model on a Virtex UltraScale FPGA and comparing CURE to the baseline Rocket Chip. Thus, the hardware overhead is represented in lookup tables (LUTs) and registers. The TileLink extension adds 0.4% more LUTs and registers, while the access-control mechanisms add 8.6% LUTs and 3.8% registers for the main memory, 0.4% LUTs and registers for an MMIO-based peripheral, and 0.2% LUTs and 0.3% registers for a DMA device. The partitioning of the last-level cache adds another overhead of 1.7% LUTs and 1.8% registers. In summary, the changes needed to implement the CURE hardware are minimal. We further used Verilator, a cycle-accurate Verilog simulator, to ensure that our Filter Engine is fully combinational logic, i.e., operates in the same cycle.

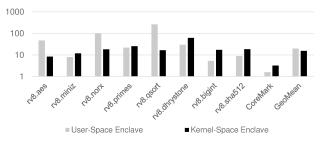

Then, we evaluated the software changes (the security monitor and additional kernel functionality to interact with the security monitor) with microbenchmarks and macrobenchmarks based on the RISC-V ISA simulator SPIKE, and QEMU, which we both

adjusted for the additional cache and TCB flushes that CURE imposes for security. These simulators reach higher execution speeds than RTL (register-transfer level) simulators that simulate the whole synthesized circuit, while not requiring the extensive engineering work to implement, e.g., the frontend CPU to FPGA chip communication, for evaluation directly on an FPGA. The microbenchmarks showed that user space enclaves are significantly faster to set up than kernel space enclaves, even though dynamic memory allocation is slower since the Security Monitor needs to verify the user-space enclave's page tables for every new entry. In the macrobenchmarks, user space enclaves impose a geometric mean overhead of 19.70%, while kernel space enclaves only induce 15.33% overhead (compared to a normal user-space process). The macrobenchmarks run noticeably longer (as they perform more complex tasks), hence, kernel space enclaves benefit from faster dynamic memory allocations to make up for the costly enclave initialization. We further tested kernel space enclaves with the stress-ng benchmark, showing that multi-core kernel space enclaves scale almost the same as native multi-processing (geometric mean overhead of 0.9% with two cores). In conclusion, our performance evaluation shows that CURE is highly practical in terms of software performance overhead and hardware area overhead.

### 3.2 Related Work

In the following, we summarize the related work in the field of Trusted Execution Environments (TEEs). Further, given the recently introduced commercial TEEs and academic works that followed, we put our work into perspective.

#### **Commercial TEEs and Extensions**

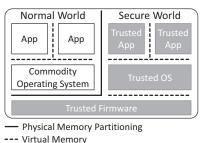

Nowadays, almost all major processor designers/manufacturers offer processors with TEEs. Arm TrustZone [9, 210] was among the first modern TEE architectures. TrustZone is a vital part of Arm processors, which are nowadays used in mobile devices, laptops, servers, and gaming consoles. TrustZone protects against privileged software attackers from the untrusted operating system or hypervisor, but neglects physical adversaries. The core idea of TrustZone is to split the system into two worlds: a normal world and a secure world. The normal world runs the untrusted OS, such as Linux, and all non-sensitive apps, while the secure world runs a Trusted OS (TOS), which manages resources and provides services to so-called Trusted Apps (TAs). These TAs contain sensitive functions which can be invoked from the normal world. The TOS separates the TAs' user-space processes with basic inter-process isolation. Hence, the whole secure world is actually only a single enclave, as a malicious TA could provoke a privilege escalation and corrupt other TAs [63]. This endangers other TAs, most of which are provided by the vendor, such as Google's Widevine, which is why the deployment of TZ services is very restricted nowadays. Apart from TrustZone, one of the most widely deployed solutions is Intel

SGX [94, 48]. SGX offers user space enclaves based on a traditional process model, where the enclave is treated as a child process of the host application. SGX protects these enclaves against a privileged software attacker, which can reside in user space, kernel space, or hypervisor level, and even some hardware attackers, e.g., that try to snoop or tamper with memory transactions on the bus. For this, SGX introduces additional CPU microcode, small hardware changes at the Page Table Walker, and a Memory Encryption Engine (MEE) to protect enclaves from DMA attacks. The MEE encrypts the enclaves' memory and ensures its integrity, so encrypted pages cannot be rolled back or switched. SGX explicitly excludes cache side-channel attacks from its adversary model, which still can have dramatic consequences for approaches that put highly sensitive data in SGX enclaves.

AMD Secure Encrypted Virtualization (SEV) [102, 103, 6, 7] is another TEE architecture for AMD platforms. SEV leverages the AMD Secure Memory Encryption (SME) technology to isolate VM enclaves from each other and the untrusted hypervisor. SEV uses a per-VM key managed by the Platform Security Processor (a dedicated co-processor), which is also responsible for attestation. There are already multiple versions of SEV, as the initial SEV design did not encrypt the processor register state, which was then the target of controlled-channel attacks. The second version, SEV-ES (Encrypted State) [103], covers these, but there still was no integrity protection for VM enclaves' pages. As a result, various controlled-channel attacks on SEV were presented. Finally, to guarantee the integrity of pages, SEV-SNP (Secure Nested Paging) [7] introduces an additional address translation to determine page ownership, building on the newly introduced Reverse Map Table. This mechanism allows only the page owner to modify a page.

Based on the high-level ideas of AMD SEV, the newly introduced Intel TDX [93] uses per-VM encryption to isolate enclaves. In contrast to SEV, TDX uses an encryption scheme that also ensures the integrity of the enclave memory.

Finally, Arm Confidential Compute Architecture (CCA) [128] was proposed, following AMD and Intel's trend of VM enclaves. CCA is a multi-enclave architecture that introduces so-called realms. Each realm is its own VM enclave, completely isolated from other enclaves and interfaced through a privileged realm manager. This realm manager, and the enclaves, are also protected from the hypervisor. The isolation is enforced by a newly added translation level in the MMU. CCA further introduces memory encryption to protect enclaves against physical attacks.

### **Academic Approaches**

In this section, we will give an overview of academic approaches on trusted execution. A broad research direction is realizing lightweight security architectures on smaller embedded systems, which provide security services such as attestation with minimal or no hardware changes. An example of the early works in this area is Flicker [131], which

combines a Trusted Platform Module (TPM) with a dynamic root of trust (in this case, AMD Secure Virtual Machine) to isolate small pieces of code.

SMART [64] establishes a dynamic root of trust functionality by storing the attestation code in read-only memory (ROM) and a securely stored key that can only be accessed if the program counter is pointing to the ROM region. SPM [179] and its follow-up works, such as Sancus [140, 141] extend the Memory Protection Unit with additional permission checks to reduce the TCB to the hardware itself. TrustLite [106] introduces an Execution-Aware Memory Protection Unit (EA-MPU) to define memory access policies based on the position of the program counter, allowing TrustLite to generalize the concept of SMART for independent regions. TyTAN [25] extends this approach with real-time support, secure boot, and secure storage.

However, these approaches are limited in their ability to support modern computing needs, such as multi-core setups, complex resource management, and secure peripheral access. Therefore, there is also research on approaches for more powerful computer systems that can handle more complex code.

Based on widely available virtualization extensions, a large body of work uses virtualization as a primitive for shielding sensitive applications [208, 39, 117, 159, 130, 84]. However, in multi-enclave scenarios, the hypervisor must provide typical virtualization features like para-virtualized device access (to allow all enclaves to access peripherals) and serve as the security monitor. This concentrates a lot of responsibilities in a single component, leading to a larger TCB [39, 208, 84]. Further, virtualization also slows down the untrusted OS.

Another popular research direction is extending commercial TEEs for more versatility and security. For TrustZone, most of these extensions aim to provide new types of enclaves [77, 29]. In particular, TrustICE [180] proposes a TrustZone-based concept for temporal isolation in the normal world. TrustICE suspends the regular OS for every sensitive application execution and invokes the TrustZone secure world to reset the normal world to a trusted state. After execution of the sensitive code, TrustICE cleans up the execution environment and resumes regular OS execution. While TrustIce uses only temporal isolation, SANCTUARY [29] adds spatial isolation to create deprivileged enclaves in the normal world, and hence, does not have to suspend the OS for enclave execution. SANCTUARY creates strongly isolated enclaves by using the TrustZone Address-Space Controller (TZASC) to assign memory regions based on IDs. While this feature is commonly used to DRM-protect media being transferred between CPU and GPU, SANCTUARY assigns IDs to individual CPU cores for fine-grained memory isolation. Other works harden TrustZone against new attack vectors, e.g., by encrypting the secure world memory area to prevent physical attacks [214], or by moving the secure world to a dedicated chip [215]. However, as these approaches cannot change the underlying security primitive used to construct the TEE, efficient side-channel resilience,

#### 20 FLEXIBLE ENCLAVES FOR APPLICATION-DRIVEN SECURITY

and binding a peripheral directly to an enclave in multi-enclave settings remained an open challenge [13].

In order to change the underlying primitive, more control over the hardware is necessary. As such, RISC-V emerged as a promising foundation for academic TEE research. One of the first TEEs on RISC-V was Sanctum [49], which extends the RISC-V architecture to create user space enclaves similar to Intel SGX. Sanctum builds on dedicated page tables per enclave and minor changes to the Page Table Walker to protect these page tables. A modified page table walker (PTW) prevents address translation for virtual addresses mapping to physical addresses used by other enclaves. Sanctum does not encrypt enclave data but can restrict DMA accesses.

Keystone [114] instead provides kernel space enclaves using the RISC-V Physical Memory Protection (PMP) to create isolated memory regions per enclave. Keystone offers a small runtime for driver access directly from enclaves, yet, does not support a direct enclaveto-peripheral binding. Further, Keystone does not isolate its security monitor from the firmware, creating a larger attack surface.

Another work, SERVAS [176], leverages authenticated encryption based on MEMSEC [201] to isolate memory. SERVAS can also protect against physical rollback/replacement attacks by ensuring authentication. In contrast to CURE, SERVAS only supports user space enclaves, does not offer enclave-to-peripheral bindings, and cannot protect against interrupt-based controlled-channel attacks.

Finally, Penglai [66] is one of the most recent RISC-V TEE architectures. Penglai combines page-table-based isolation with memory encryption (with a scheme that also provides integrity) and cache partitioning to provide user space enclaves. In comparison to other RISC-V TEEs like KeyStone, Penglai uses a safeguarded page table to isolate the memory: 1) the page table is moved to a dedicated memory section, 2) the PMP is configured to protect this table, and all memory accesses to this region are trapped by the security monitor, 3) the page table walker (PTW) is extended to only allow page table walks within the protected memory area. This high-level concept is quite similar to Sanctum's memory isolation. In contrast to CURE, Penglai only supports user space enclaves and has no support for enclave-to-peripheral binding.