# Supercapacitors-based Pulsed Power Supply for the ASDEX Upgrade Toroidal Field Coil

### **Doctoral thesis**

Zur Erlangung des akademischen Grades Doktor-Ingenieur (Dr.-Ing.) Genehmigte Dissertation von Antonio Magnanimo aus Neapel, Italien Tag der Einreichung: 23.03.2023, Tag der Prüfung: 28.06.23

Referent: Prof. Dr.-Ing. G. Griepentrog Korreferent: Prof. Dr.sc. M. Heldwein Betreuer am Max-Planck-Institut für Plasmaphysik / ASDEX Upgrade: Dr.-Ing. M. Teschke Darmstadt, Technische Universität Darmstadt Jahr der Veröffentlichung der Dissertation auf TUprints: 2023

TECHNISCHE UNIVERSITÄT DARMSTADT

Department of Electrical Engineering and Information Technology

Institute of Power Electronics and Control Drives

Supercapacitors-based Pulsed Power Supply for the ASDEX Upgrade Toroidal Field Coil Doctoral thesis

Accepted doctoral thesis by Antonio Magnanimo

Date of submission: 23.03.2023 Date of thesis defense: 28.06.23

Darmstadt, Technische Universität Darmstadt Jahr der Veröffentlichung der Dissertation auf TUprints: 2023

Bitte zitieren Sie dieses Dokument als: URN: urn:nbn:de:tuda-tuprints-244120 URL: http://tuprints.ulb.tu-darmstadt.de/24412

Dieses Dokument wird bereitgestellt von tuprints, E-Publishing-Service der TU Darmstadt http://tuprints.ulb.tu-darmstadt.de tuprints@ulb.tu-darmstadt.de

Die Veröffentlichung steht unter folgender Creative Commons Lizenz: Namensnennung 4.0 International https://creativecommons.org/licenses/by/4.0/

# Erklärungen laut Promotionsordnung

### §8 Abs. 1 lit. c PromO

Ich versichere hiermit, dass die elektronische Version meiner Dissertation mit der schriftlichen Version übereinstimmt.

### §8 Abs. 1 lit. d PromO

Ich versichere hiermit, dass zu einem vorherigen Zeitpunkt noch keine Promotion versucht wurde. In diesem Fall sind nähere Angaben über Zeitpunkt, Hochschule, Dissertationsthema und Ergebnis dieses Versuchs mitzuteilen.

### §9 Abs. 1 PromO

Ich versichere hiermit, dass die vorliegende Dissertation selbstständig und nur unter Verwendung der angegebenen Quellen verfasst wurde.

## §9 Abs. 2 PromO

Die Arbeit hat bisher noch nicht zu Prüfungszwecken gedient.

Darmstadt, 23.03.2023

A. Magnanimo

### Acknowledgements

This work has been carried out within the framework of the EUROfusion Consortium and has received funding from the Euratom Research and Training Programme under the Grant Agreement n. 633053.

I would like to offer my special thanks to Prof. Dr.-Ing. Gerd Griepentrog for his professional advice during the last years and for having given me the opportunity to be part of his talented research group.

I express my deepest gratitude to Dr.-Ing. Markus Teschke for supporting me during this amazing research and life experience.

I would like to extend my sincere thanks to all my colleagues and the entire Max-Planck-Institute for Plasma Physics. This institute has been a second family for me. I am forever grateful and I will never forget you.

Dedicated to my extraordinary wife Adriana and my family in Ischia for their unconditional love and immense support. I could have never made it without you.

Grazie.

# Kurzfassung

ASDEX Upgrade ist ein experimenteller Tokamak, in dem die Physik kernfusionsrelevanter Plasmen untersucht wird. Seine elektrische Energie liefern drei Schwungradgeneratoren, die vor Beginn jedes Experiments für einige Minuten mit bis zu 15 MW aufgeladen werden. Die gespeicherte Energie wird dann verwendet, um den hohen Leistungsbedarf während eines Experiments – Plasmapuls genannt – von bis zu 450 MVA zu decken. Der größte der drei Schwungradgeneratoren könnte im Falle eines größeren Schadens nicht ersetzt werden, da derzeit keine vergleichbaren Geräte auf dem freien Markt erhältlich sind. Daher ist die Entwicklung eines alternativen Stromversorgungssystems mit hoher Leistung und Energie und voll regelbarer Leistung geplant. Superkondensatoren sind bekannt für ihre sehr hohe spezifische Leistung. Durch die Kombination dieser Technologie mit einer geeigneten Stromrichtertopologie wie dem modularen Multilevel-Umrichter wäre es möglich, die Spulen zukünftiger Tokamaks mit höherer Leistung und Zuverlässigkeit zu speisen. Diese Topologie ermöglicht in der Tat eine diskret geregelte Ausgangsspannung und kann dank ihrer hohen Modulanzahl auch im Fehlerfall einiger von ihnen kontinuierlich weiter arbeiten, während ein Schwungrad-generator dies nicht kann. Diese Dissertation zeigt das Konzept der genannten Stromversorgung, zeigt Vorteile und Herausforderungen gegenüber bestehenden Technologien auf, konzentriert sich auf Zuverlässigkeit, Skalierbarkeit und Flexibilität mit der Idee, diese Lösung auch für andere Anwendungen in der Zukunft anzupassen. Darüber hinaus wurde ein kleiner Demonstrator aus vier identischen Modulen gebaut und in drei verschiedenen Konfigurationen getestet: seriell, parallel und kombiniert seriell/parallel. Die serielle Konfiguration wurde getestet, um die entwickelte Strategie zur Ansteuerung zu validieren, die parallele ist grundlegend für die Skalierbarkeit des Systems und die letzte Konfiguration validiert ihre Kombination. Die experimentellen Ergebnisse werden gezeigt und mit Simulationen verglichen, um abschließend ein klareres Bild über die Skalierbarkeit des Systems zu entwickeln.

# Abstract

ASDEX Upgrade is an experimental tokamak where the physics of nuclear fusion relevant plasmas is studied. Its electrical power is provided by three flywheel generators that are charged up before the start of each experiment with up to 15 MW for several minutes. The stored energy is then used to satisfy the high power needs during an experiment called plasma pulse - of up to 450 MVA. The largest one of the three flywheel generators could not be replaced in case of a major fault because currently there are no comparable devices available on the free market. Therefore, the development of an alternative power supply system with high power and energy and fully controllable output is planned. Supercapacitors are well known for their very high specific power. Combining this technology with a proper power converter topology such as the modular multilevel converter, it would be possible to feed the coils of future tokamaks with higher performance and reliability. This topology, indeed, allows a discrete-leveled output voltage and, thanks to its high modules number, it can operate continuously even in case of fault of some of them, while a flywheel generator could not. This dissertation shows the concept of the mentioned power supply, highlighting advantages and challenges compared to existing technologies, focusing on reliability, scalability and flexibility with the idea of adapting this solution even for different applications in the future. Furthermore, a small-scale demonstrator composed by four identical modules has been built, and it has been tested in three different configurations: serial, parallel and combined serial/parallel. The serial configuration has been tested to validate the developed control strategy, the parallel one is fundamental for the scalability of the system and the last configuration validated their combination. The experimental results are shown and compared with simulations, and finally a clearer picture about the scalability of the system was developed.

# Contents

| 1 | Intro      | Motive   | <b>n</b><br>ation of the dissertation                                  | <b>1</b><br>1 |

|---|------------|----------|------------------------------------------------------------------------|---------------|

|   | 1.1<br>1.2 |          |                                                                        | 1<br>2        |

|   |            |          | ization of the dissertation                                            |               |

|   | 1.3        | SOITWA   | are used for the dissertation                                          | 2             |

| 2 |            |          | r fusion as an energy source                                           | 3             |

|   | 2.1        | What i   | is fusion?                                                             | 3             |

|   |            | 2.1.1    | The reaction                                                           | 4             |

|   |            | 2.1.2    | The plasma state                                                       | 5             |

|   |            | 2.1.3    | Magnetic confinement                                                   | 5             |

|   | 2.2        | The to   | kamak                                                                  | 6             |

|   |            | 2.2.1    | Lawson criterion                                                       | 8             |

|   |            | 2.2.2    | Energy production in a thermonuclear power plant                       | 9             |

|   |            | 2.2.3    | ASDEX Upgrade                                                          | 10            |

| 3 | Eno        | rav otov | rage systems for pulsed power supplies                                 | 13            |

| ა | 3.1        | •••      | · · · · · · · · · · · · · · · · · · ·                                  | 13<br>13      |

|   | 3.1        |          | 1                                                                      | -             |

|   |            | 3.1.1    | 51                                                                     | 13            |

|   |            |          | 0 1                                                                    | 14            |

|   | 3.2        |          | 0                                                                      | 15            |

|   |            | 3.2.1    | <i>y</i>                                                               | 15            |

|   |            | 3.2.2    |                                                                        | 16            |

|   | 3.3        | _        | 1                                                                      | 21            |

|   |            | 3.3.1    | $\mathbf{J}$                                                           | 21            |

|   |            | 3.3.2    | Electrical simplified model                                            | 23            |

|   |            | 3.3.3    | Existing Supercapacitors-based power supplies for fusion experiments 2 | 24            |

|   | 3.4        | The m    | odular multilevel converter                                            | 27            |

|   |            | 3.4.1    | The topology                                                           | 27            |

|   |            | 3.4.2    | Fundamental equations                                                  | 29            |

|   |            | 3.4.3    | ±                                                                      | 31            |

|   |            |          |                                                                        |               |

| 4 | The  |         | sed MMC-like topology for ASDEX Upgrade TF coils | 33    |

|---|------|---------|--------------------------------------------------|-------|

|   | 4.1  | The co  | oncept                                           |       |

|   |      | 4.1.1   | Topology description                             |       |

|   |      | 4.1.2   | Submodule configuration                          |       |

|   |      | 4.1.3   | Charging process                                 |       |

|   | 4.2  | The co  | ontrol strategy                                  |       |

|   |      | 4.2.1   | The current control                              |       |

|   |      | 4.2.2   | Communication protocol                           |       |

|   |      | 4.2.3   | PLECS model and simulations results              |       |

|   | 4.3  | Paralle | elization of several submodules                  | . 53  |

|   |      | 4.3.1   | Busbars impedance desgin                         | . 53  |

|   |      | 4.3.2   | Supercapacitor modules ageing effect             | . 58  |

|   | 4.4  | Real ti | ime fault detection and management               | . 60  |

|   |      | 4.4.1   | Submodule internal fault                         | . 60  |

|   |      | 4.4.2   | Row internal short circuit                       | . 62  |

|   |      | 4.4.3   | External faults                                  | . 64  |

| 5 | Tho  | dovolo  | ped demonstrator and experimental results        | 67    |

| 5 | 5.1  |         | odule development                                | -     |

|   | 5.1  | 5.1.1   |                                                  |       |

|   |      | 5.1.2   | 130 V / 750 A operation                          |       |

|   | 5.2  |         | -SM prototype                                    |       |

|   | 5.2  | 5.2.1   |                                                  |       |

|   |      | 5.2.1   | Serial operation                                 |       |

|   |      | 5.2.2   | -                                                |       |

|   |      | 5.2.3   | Parallel operation                               |       |

|   |      |         |                                                  |       |

| 6 |      |         | ation and scalability                            | 93    |

|   | 6.1  |         | erter efficiency                                 |       |

|   | 6.2  |         | stimation                                        |       |

|   | 6.3  | Scalab  | pility limits                                    | . 96  |

| 7 | Con  | clusion | 1                                                | 99    |

|   | 7.1  | Valida  | ted results                                      | . 99  |

|   | 7.2  | Critica | al points and challenges for a full-scale device | . 100 |

| 8 | Auth | lor bub | plications, students and curriculum vitae        | 101   |

| - | 8.1  | •       | f main publications                              | -     |

|   | 8.2  |         | f supervised students                            |       |

|   | 8.3  |         |                                                  |       |

|   | 0.0  | Guine   |                                                  | . 105 |

| 9 | Арр | endix  |                         | 105 |

|---|-----|--------|-------------------------|-----|

|   | 9.1 | Used r | neasurement systems     | 105 |

|   |     | 9.1.1  | Voltage measurement     | 105 |

|   |     | 9.1.2  | Current measurement     | 105 |

|   |     | 9.1.3  | Temperature measurement | 105 |

# List of Figures

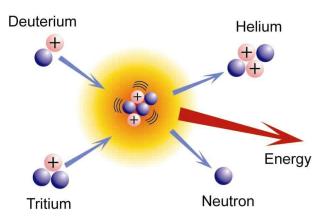

| D-T reaction: this is the most favourable reaction among all the possible ones on the Earth. The fusion of a D and a T nuclei generates a nucleus of helium and a neutron, releasing 17 MeV of energy [8].                                                                                                                                                                                                                                  | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

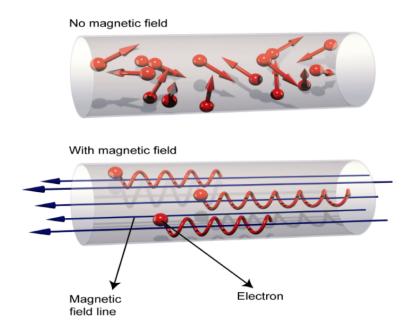

| Magnetic confinement: without any induced external magnetic field in a plasma,<br>electrons are free to move in any directions. By applying a magnetic field instead,<br>they are forced to move in the direction of the magnetic field lines and gyrate<br>around them: this is the principle on which is based the magnetic confinement of                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

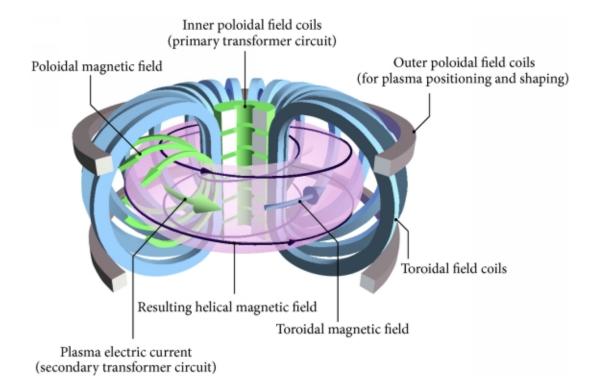

| Main tokamak's coils: the CS coils, $I_P$ , and the poloidal magnetic field are indicated<br>in green; the TF coils and the toroidal magnetic field are shown in blue; the<br>outer poloidal field (or PF) coils are displayed in gray. The confined plasma is                                                                                                                                                                              | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| represented by the magenta torus [7]                                                                                                                                                                                                                                                                                                                                                                                                        | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

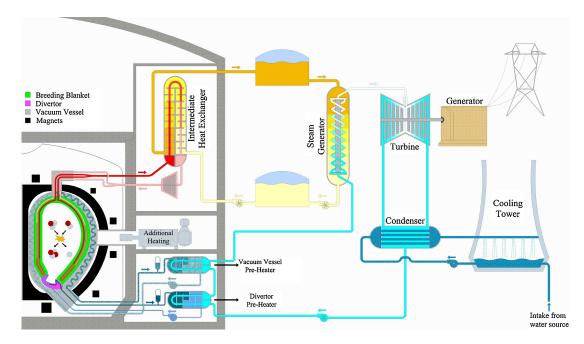

| in terms of electrical energy generation [16]                                                                                                                                                                                                                                                                                                                                                                                               | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

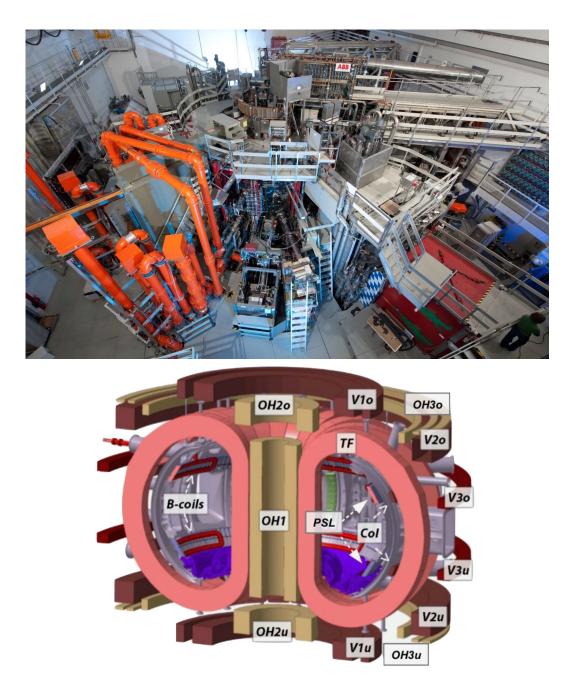

| Panoramic view of the ASDEX Upgrade torus hall (top) and machine coils' configuration (bottom) [19].                                                                                                                                                                                                                                                                                                                                        | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

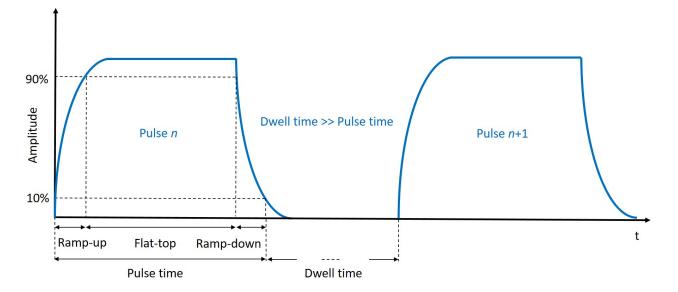

| Typical current shape of a pulsed powered load. The time between consecutive pulses (dwell time) is typically several orders of magnitude longer than the pulse time [20].                                                                                                                                                                                                                                                                  | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

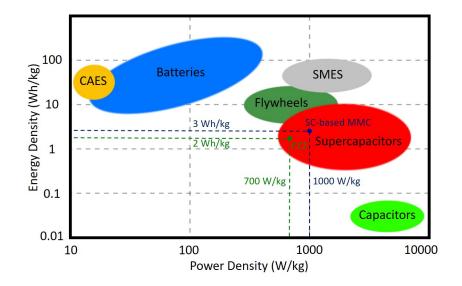

| Comparison among different energy storage systems in terms of energy and power density; CAES and SMES stand for compressed air energy storage and superconducting magnetic energy system, respectively [21]-[22]. The colored zones are only indicative of a family of devices, and further curves could be inserted for a more specific type of device (for instance, type of battery or capacitor) but they are not shown for simplicity. | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

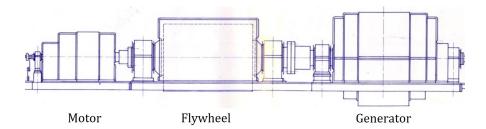

| Typical structure of a flywheel generator: a motor accelerates a flywheel, converting electrical energy into kinetic energy. Once the amount of required energy has been stored within the flywheel, the generator can convert it back into electrical energy again powering the electrical load [19]                                                                                                                                       | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                             | the Earth. The fusion of a D and a T nuclei generates a nucleus of helium and a neutron, releasing 17 MeV of energy [8] Magnetic confinement: without any induced external magnetic field in a plasma, electrons are free to move in any directions. By applying a magnetic field instead, they are forced to move in the direction of the magnetic field lines and gyrate around them: this is the principle on which is based the magnetic confinement of fusion devices [7] |

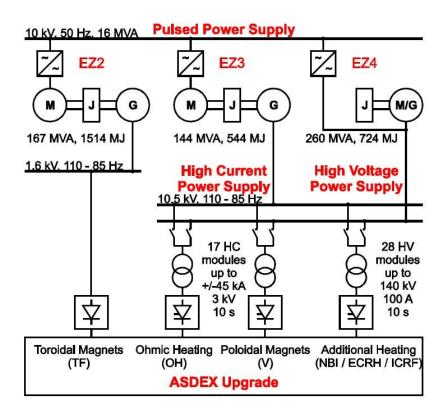

| 3.4  | ASDEX Upgrade's pulsed power supply system. The schema shows the three flywheel generators, each of which supplying a different load: EZ2 provides power to the TF coil while EZ3 and EZ4 supply CS, PF coils and the additional                                                                                                                                                                           |                |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|      | heating systems. The output configurations of EZ3 and EZ4 can be changed and they can both power the mentioned loads [26]                                                                                                                                                                                                                                                                                  | 17             |

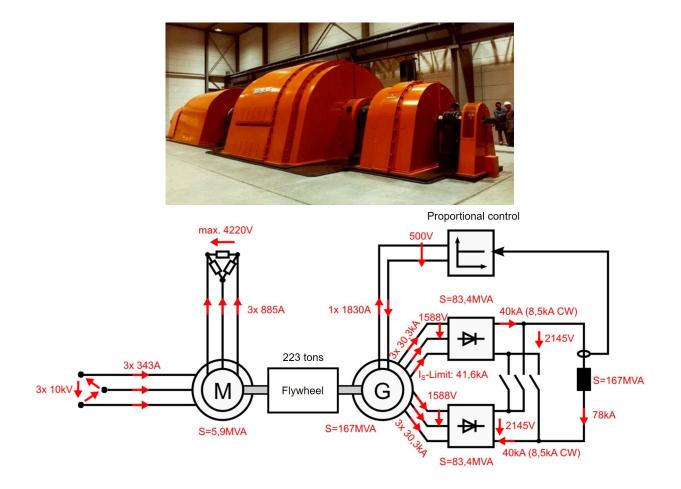

| 3.5  | Flywheel generator EZ2 photo (top) and electrical simplified schema (bottom): the three-phase motor drive takes 5.7 MW from the 10 kV grid storing up to 2 GJ in the flywheel within 30 min; the 167 MVA generator thus can convert the kinetic energy of the flywheel into eletrical energy, generating up to 150 MW for 10 s. Its output power passes through an 20 kA diada restifier directly powering |                |

| 3.6  | 10 s. Its output power passes through an 80 kA diode rectifier directly powering the ASDEX Upgrade's TF coil [26]                                                                                                                                                                                                                                                                                          | 18             |

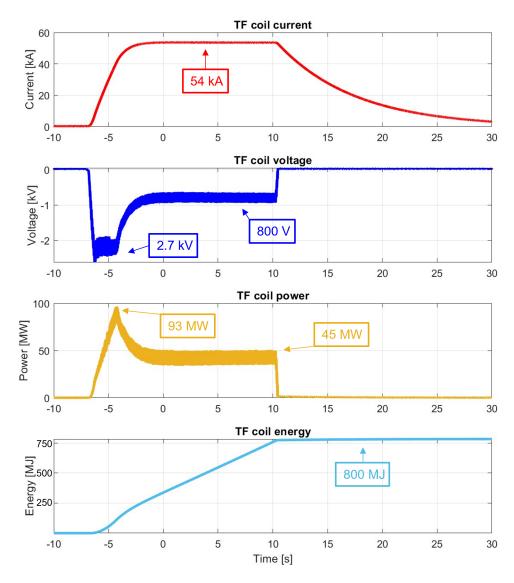

|      | flat-top phase with a limited ripple (<0.1%); the voltage required is 2.7 kV during the ramp-up and 800 V during the flat-top, where only copper losses have to be covered. The whole experiment requires about 800 MJ of energy [27]                                                                                                                                                                      | 20             |

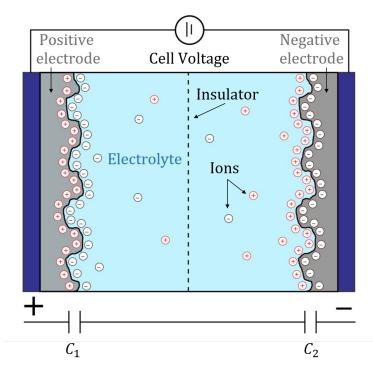

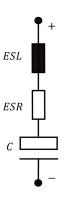

| 3.7  | SC cell simplified inner structure: the cell capacitance <i>C</i> is the equivalent capacitance of the two charge-ion double layers ( $C_1$ and $C_2$ ) at the interface between electrodes                                                                                                                                                                                                                | 22             |

| 3.8  | and electrolyte $(C = \frac{C_1 \cdot C_2}{C_1 + C_2})$ [29]                                                                                                                                                                                                                                                                                                                                               | 22             |

| 3.9  | path. Both the parameters are minimized by manufacturers                                                                                                                                                                                                                                                                                                                                                   | 23             |

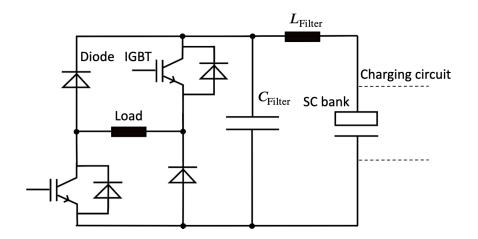

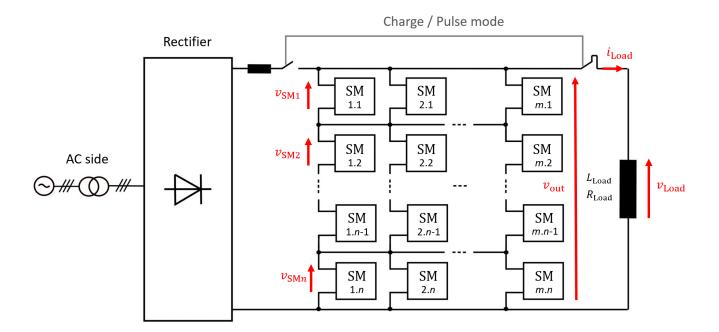

|      | composed by four modules which can be connected in several configurations; a filter ensures to limit the high frequency content of the supercapacitors current and a H-bridge converter is used to control the load current [34].                                                                                                                                                                          | 24             |

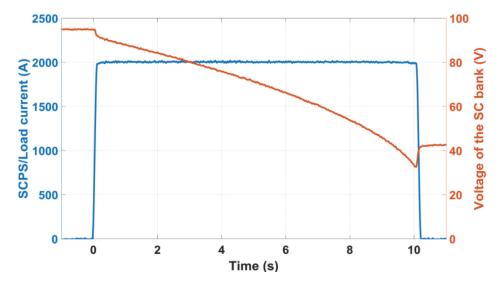

| 3.10 | PROTO-SPHERA typical experiment: the current is ramped-up at 2 kA, kept constant for the flat-top phase (10 s in this case), and finally ramped-down again                                                                                                                                                                                                                                                 | 0.6            |

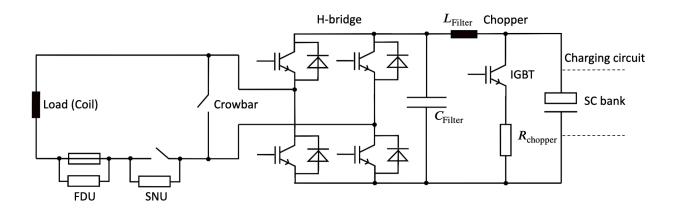

| 3.11 | [34]                                                                                                                                                                                                                                                                                                                                                                                                       | 26             |

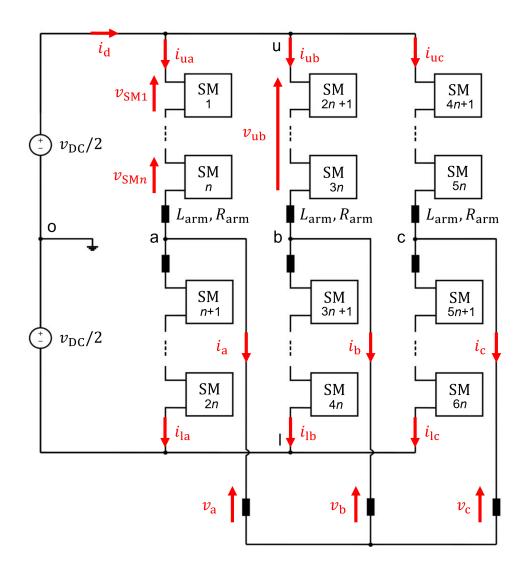

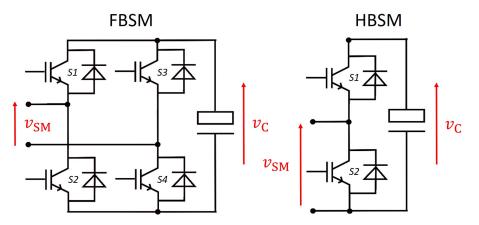

|      | discharge path for the inductive energy of the coils in case of fault. [35] Conventional MMC topology for 3-phase loads [42]                                                                                                                                                                                                                                                                               | 26<br>28<br>29 |

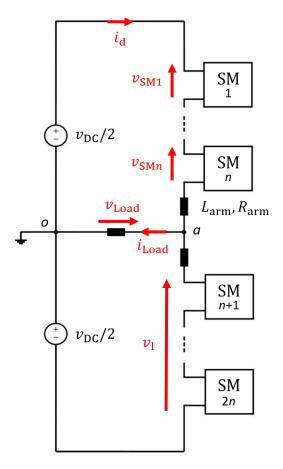

| 3.14 | MMC simplified cicuit for a single-phase AC load [44]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 32 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

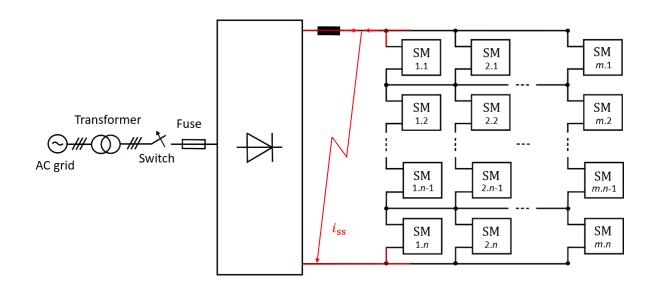

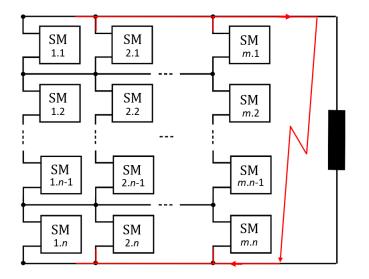

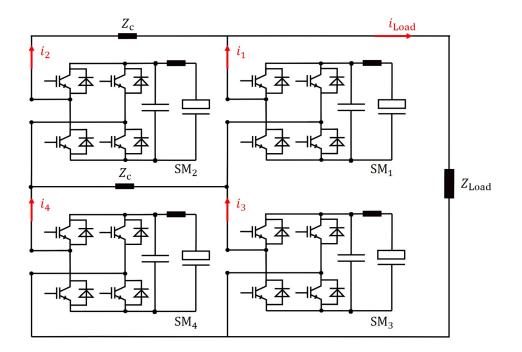

| 4.1  | Revised MMC for the ASDEX Upgrade TF coil pulsed power supply system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 34 |

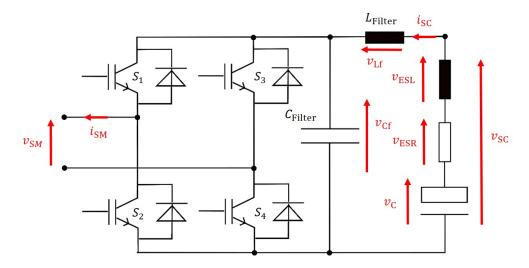

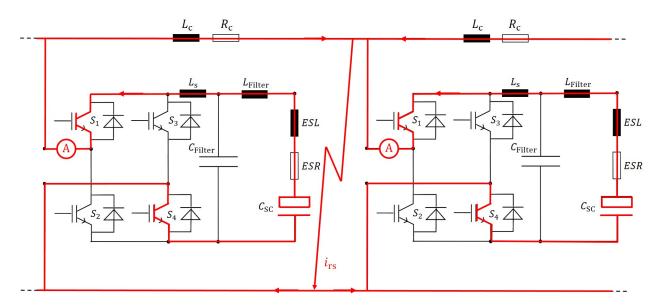

| 4.2  | Proposed submodule simplified circuit: the power stage filter is required to protect IGBT and supercapacitors modules especially during transients.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 36 |

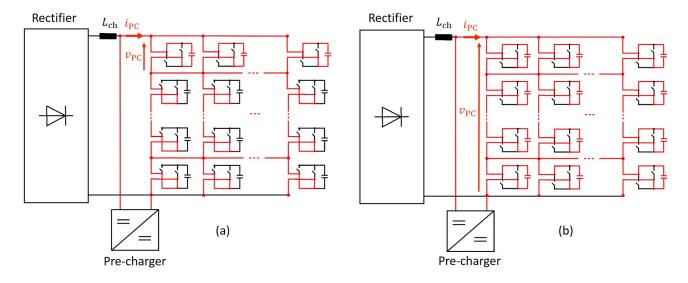

| 4.3  | Pre-charging phase: this phase is required to charge the supercapacitor modules<br>at the mimum voltage required by the boost-charging phase. Considering the<br>rectifier output voltage $v_i$ =800 V, the pre-charger should have an output voltage<br>of 38 V (see Eq. 4.14) if each row is charged individually (a) or 800 V if all the<br>supercapacitors are charged together (b). The charging current has to be at least<br>one order of magnitude larger than the leakage current of the supercapacitors in<br>order to avoid to end up in an infinite pre-charging time. In order to keep the<br>schema clear IGBT and supercapacitor modules symbols used in this picture have<br>been simplified to standard switches and capacitors, respectively | 39 |

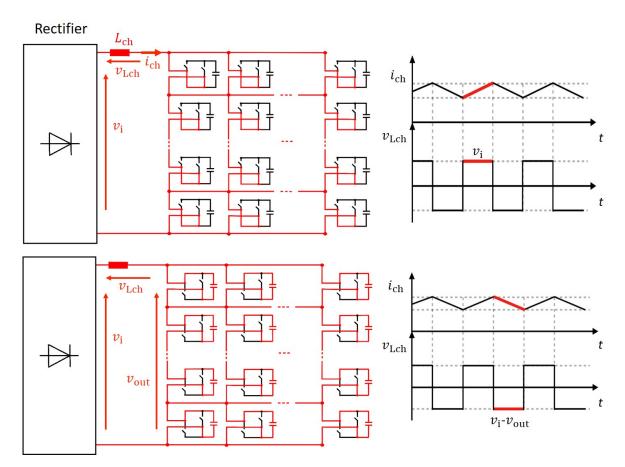

| 4.4  | Boost-charging phase: the charger inductor first stores energy and uses it than to charge the supercapacitor modules, as in a step-up converter. During the second half of each period, the charging current decreases only if $v_i - v_{out}$ is negative, otherwise it would rise in an uncontrolled way. This is the main reason why this charging phase can start only if the supercapacitors have been charged at $v_{out} \ge v_i$ by the pre-charger.                                                                                                                                                                                                                                                                                                   | 41 |

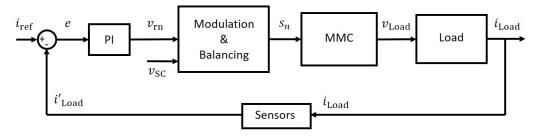

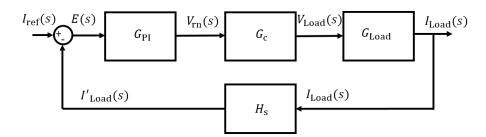

| 4.5  | Closed-loop control scheme.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 42 |

| 4.6  | Closed-loop control scheme in the Laplace domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 43 |

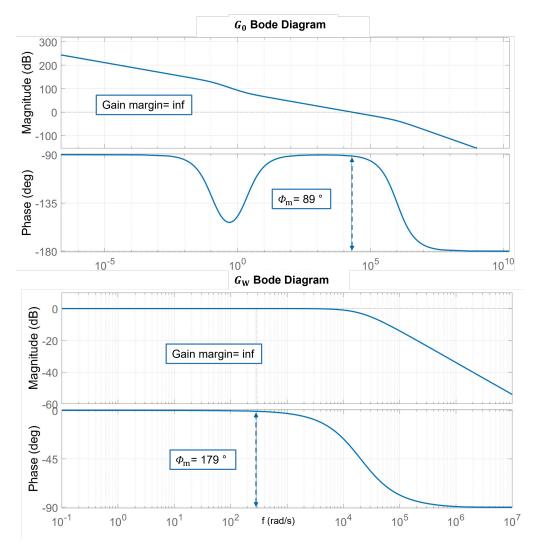

| 4.7  | Bode plots of open-loop and closed-loop transfer functions. The curves have been obtained with the help of Matlab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44 |

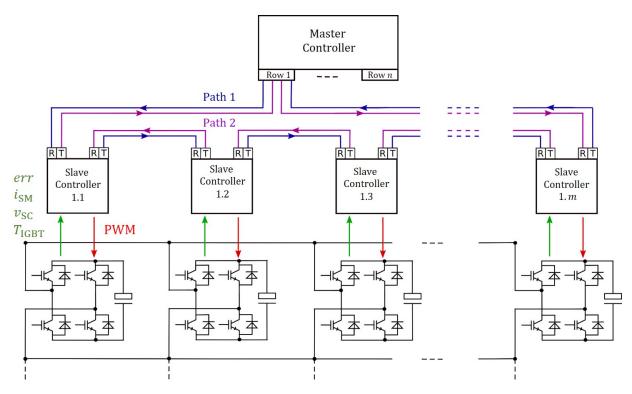

| 4.8  | EtherCAT network simplified schema for the first row of the converter: the master controller communicates with the first and the last slave controllers via two identical (and opposite in direction) paths. Each slave controller reads its subpackage and place its information into it 'on the fly' in order to keep the communication fast. The whole communication is realised via fiber optic thanks to two EtherCAT media converters per terminal, which are not shown in the                                                                                                                                                                                                                                                                           |    |

|      | schema for simplicity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 46 |

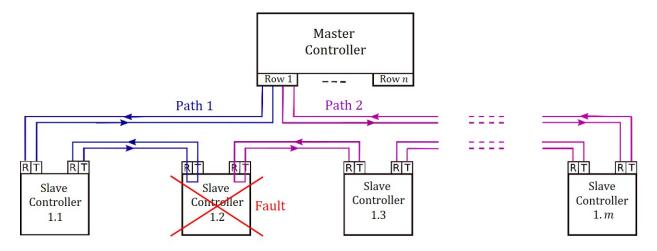

| 4.9  | Fault example in the communication network of the Row 1: the information<br>can be sent back through the two new line topologies formed between slave<br>1.1-master and slave 1.3-master. Due to the missing data into the communication<br>package, the master can identify the failed module and the operation can continue.                                                                                                                                                                                                                                                                                                                                                                                                                                 | 47 |

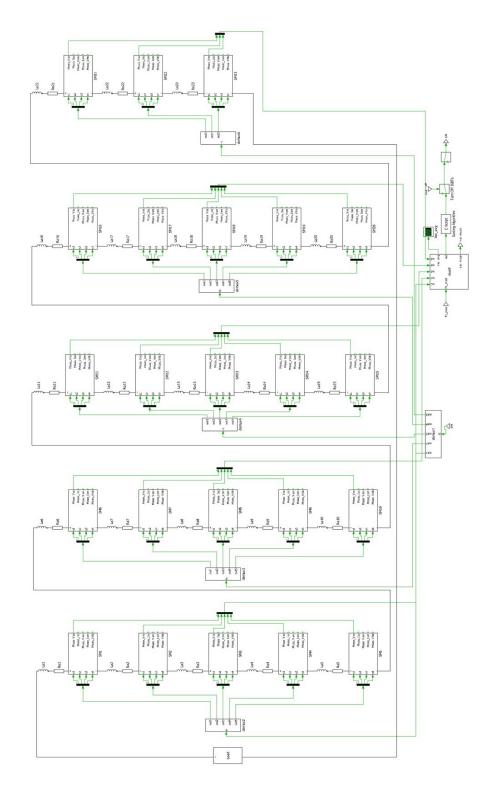

| 4.10 | Full-scale converter PLECS model: each block (SM1-SM23) represents the equivalent circuit of a row, composed by 96 submodules in parallel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49 |

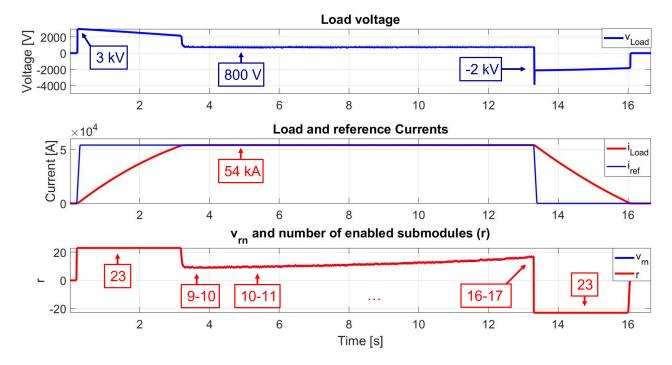

| 4.11 | PLECS simulation for a standard 10 s long experiment: the converter provides its maximum voltage during the ramp-up phase, while it starts its switched operation during the flat-top and finally recovers the inductive energy of the load during the ramp-down.                                                                                                                                                                                                              | 50 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

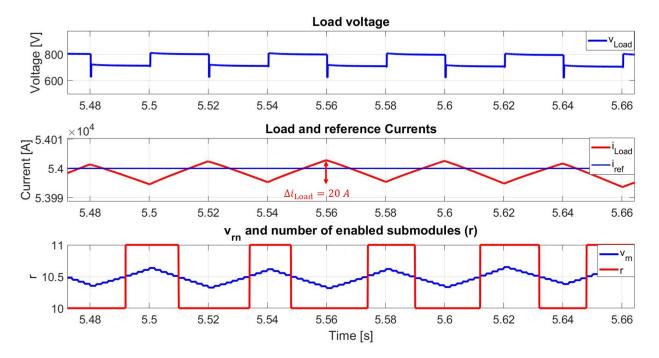

| 4.12 | Zoom of the previous figure: the subswitching during standard switching events are due to the voltage balancing algorithm, which in order to keep the supercapacitors voltages balanced swaps the submodules multiple times ( $f_c$ ) during a single cycle.                                                                                                                                                                                                                   |    |

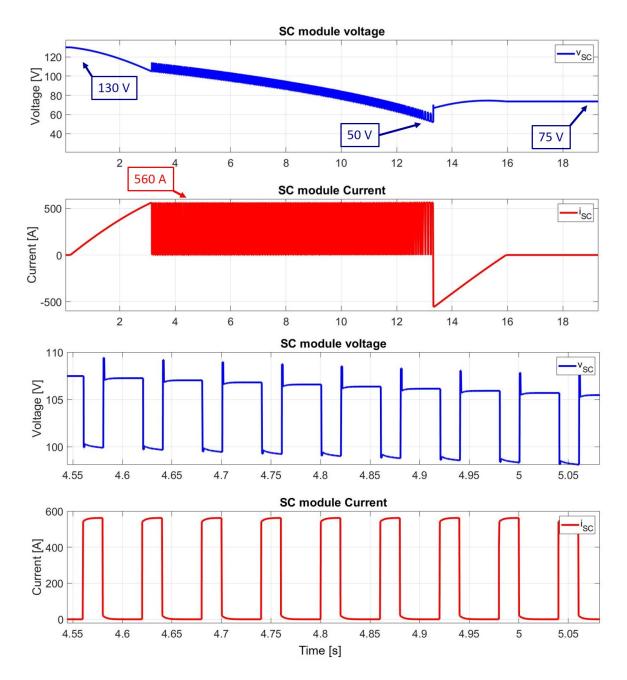

| 4.13 | Single supercapacitors module electrical scenario during a pulse: the voltage starts from its nominal value (130 V) and loses about 50 V during the whole pulse, while the current is first continous during the ramp-up phase and then pulsed (DC) during the flat-top phase. During the ramp-down phase $i_{SC}$ is negative due to the inductive energy of the load that is recovered and shared among all the submodules. The two lower plots are a zoom of the upper ones | 52 |

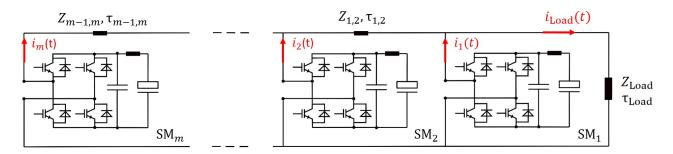

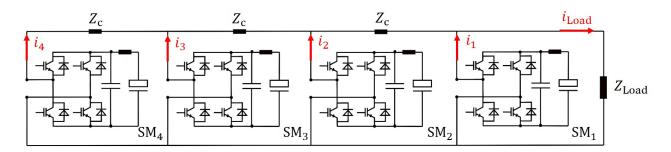

| 4.14 | Simplified circuit of <i>m</i> submodules in parallel: $Z_{1,2}Z_{m-1,m}$ are the impedances of the busbars (or cables) connecting the submodules belonging to the same row. Each submodule has a different distance from the load and this can cause currents unbalancing if $Z_{1,2}Z_{m-1,m}$ are not well designed                                                                                                                                                         | 53 |

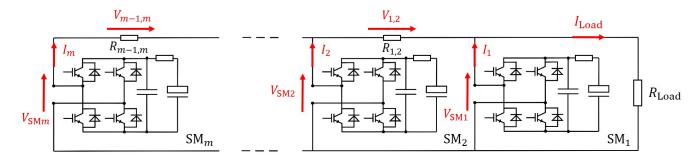

| 4.15 | Simplified circuit of <i>m</i> submodules in parallel: $R_{1,2}R_{m-1,m}$ are the resistances<br>of the busbars connecting the submodules belonging to the same row. Each<br>submodule has a different distance from the load and this leads to steady state<br>currents unbalancing which can be limited by minimizing the resistance of the<br>bars. Inductances of the circuit are neglected since they do not play any relevant<br>role in steady state condition          | 55 |

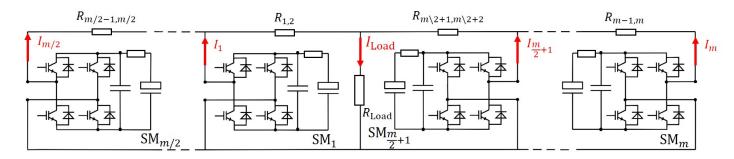

| 4.16 | Simplified circuit of $m$ submodules in parallel with load connected in the center of the row: this type of connection halves the distance between the load and the last submodule in comparison with the configuration shown in Fig. 4.15                                                                                                                                                                                                                                     | 56 |

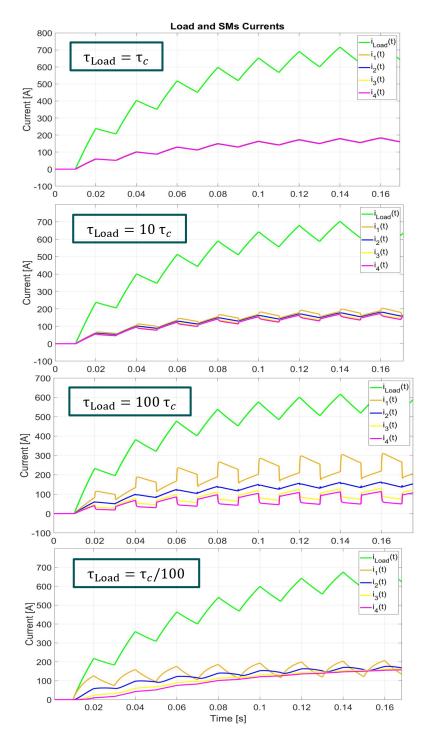

| 4.17 | Simulation results of 4 parallel submodules with different $Z_c$ : only in the first case $\tau_{\text{Load}} = \tau_c$ while in the other 3 cases the effect of unmatching is shown. Top-right and bottom-left plots show unmatching due to a too high resistance in the parallel connections, while the last plot shows the effect caused by a too large $L_c$ .                                                                                                             | 57 |

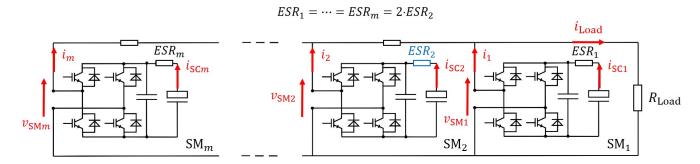

| 4.18 | Simplified circuit of <i>m</i> submodules in parallel with different $ESR$ : all the submodules except one are at the end of their lifetime, while the different one (SM <sub>2</sub> ) has been recently replaced and therefore has a lower $ESR$ .                                                                                                                                                                                                                           | 59 |

| 4.19 | Submodule internal fault: in case $S_2$ does not open before $S_1$ closes, a short circuit occurs due to the filter capacitance energy that start to discharge through the red path of the figure. The gate driver of $S_1$ has to be fast enough to detect the short circuit current and interrupt it before it triggers unwanted short circuits                                                                                                                              |    |

|      | in the adiacent submodules.                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 61 |

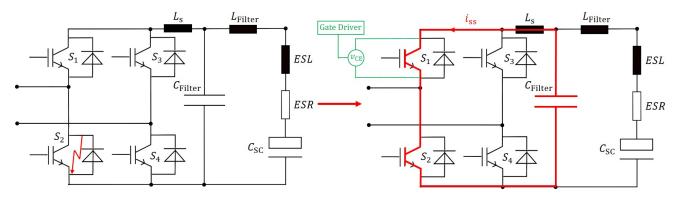

| 4.20 | Failed and operating submodules in parallel compared: if $L_s \ll L_c$ , $i_{ss}$ (in red) raises much faster than $i_{rs}$ (in orange). In this way the failed submodule can interrupt $i_{ss}$ before the parallel submodules detect any short circuit and the whole row can continue the operation with <i>m</i> -1 submodules.                                                                                                   | 62 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

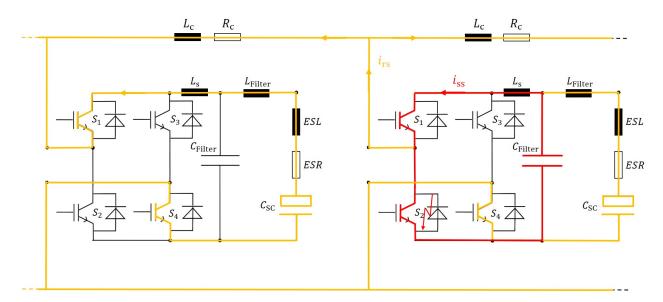

| 4.21 | Row internal short circuit: once the short circuit current exceeds a specific threshold the submodules controllers force the power stage to a zero-voltage state (by-pass) and send an error signal to the master controller. This means that the master controller is informed about the row status and knows that it is not available anymore for operation.                                                                       | 63 |

| 4.22 | DC-side short circuit in charge configuration: all the submodules detect the fault<br>by a change of current direction and are forced by their local microcontrollers to<br>a zero-voltage state. The switches connecting the charging circuit with AC-grid<br>are open and if that is not sufficient, a fuse can interrupt the short circuit current.                                                                               | 64 |

| 4.23 | Load side short circuit: this fault is detected by the submodules current sensors.<br>The local microcontrollers force to a zero-voltage state their respective submodules.                                                                                                                                                                                                                                                          | 65 |

| 5.1  | Supercapacitor module used for the prototype: the module is composed by 48 x 2.7 V cells in series for a total voltage of 130 V. Being a custom module built for this project, it has been decided to keep it as simple (and passive) as possible avoiding any active electronics in it (e.g. voltage balancing)                                                                                                                     | 68 |

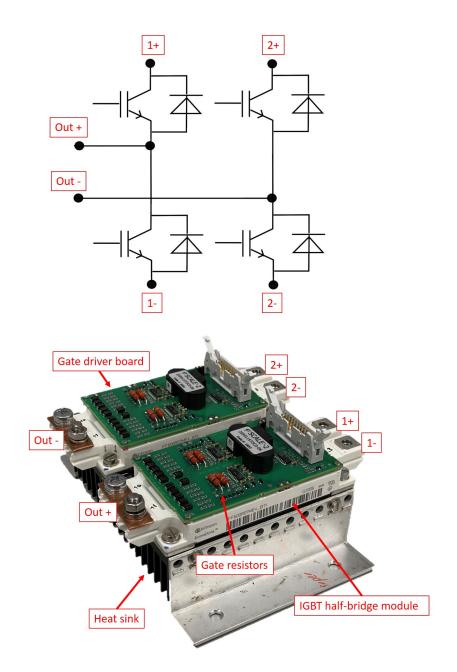

| 5.2  | Power stage schema (top) and photo (bottom): each half-bridge has a positive, a negative and an output terminal marked in red in both the pictures. By connecting the positive and negative terminals of the first half-bridge with their respective ones of the second half-bridge, a full-bridge can be obtained. The photo shows also the gate driver board with gate resistors mounted and the heat sink used for the prototype. | 70 |

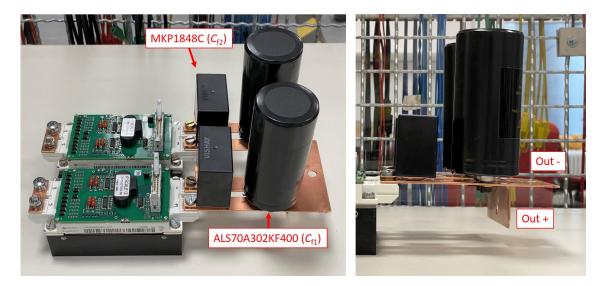

| 5.3  | Filter capacitors mounted on the power stage: top view on the left, side view<br>on the right. One copper bar output terminal has been bent to 90 degrees with<br>respect to the other one to facilitate the connection with the supercapacitor module.                                                                                                                                                                              | 71 |

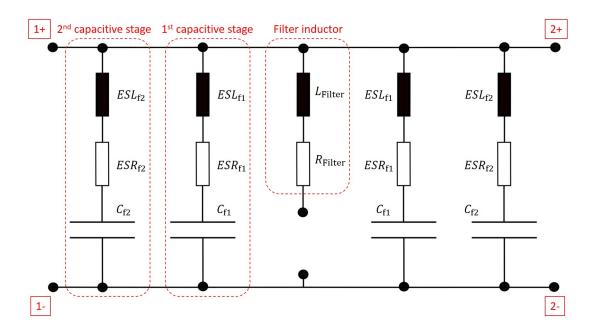

| 5.4  | Power stage filter simplified schema: the filter is splitted into two symmetrical parts sharing the same filter inductor. Stray inductances and parasitic elements of the copper bars connecting the filter capacitors can be neglected. The terminals $1+/-$ and $2+/-$ are highlighted to show the connection points with the two IGBT half-bridges of the power stage (see Fig. 5.2).                                             | 72 |

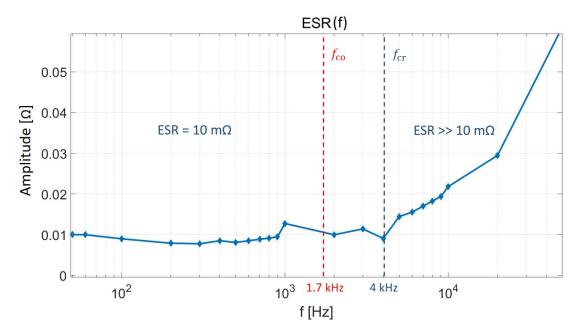

| 5.5  | Experimentally measured <i>ESR</i> frequency dependency: the designed filter is a low pass filter with a cut-off frequency $f_{co}=1.7$ kHz. It is important durign the designing phase to keep this value within the safe operating range ( $f < f_{cr}$ ) since a higher <i>ESR</i> leads to higher losses and shorter lifetime of the supercapacitors.                                                                            | 73 |

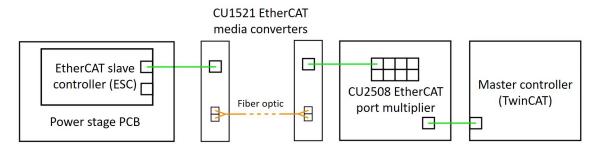

| 5.6  | Example of EtherCAT network required to control a submodule: the master controller is a virtual PLC realised by the help of TwinCAT. The master communicates via a port multiplier (to keep scalability possible) and two media converters (to avoid electromagnetic interferences) to the slave controller. The slave controller board is directly mounted on the power stage PCB                                                                                                                                                          | 74 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

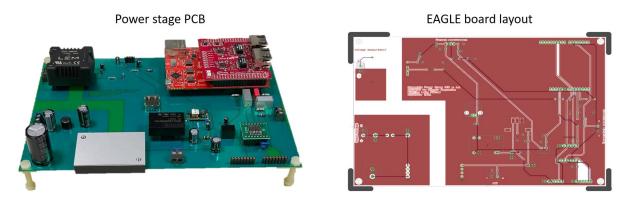

| 5.7  | Power stage PCB (left) and its EAGLE layout (right): this board acts as an adapter<br>between the microcontroller and measurements components/gate drivers. The<br>board is also used to power all the electronic components of the submodule by<br>taking the power directly from the supercapacitor module. The PCB has been<br>designed on the EAGLE software                                                                                                                                                                            | 74 |

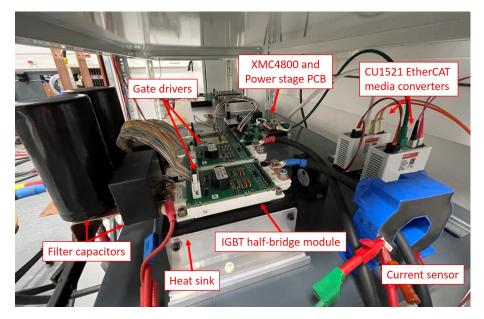

| 5.8  | Submodule experimental setup: the main submodule components are shown. An additional CU1521 has been added to the first one in order to be able to configure the EtherCAT network in ring topology, which means that redundancy can be ensured.                                                                                                                                                                                                                                                                                             | 76 |

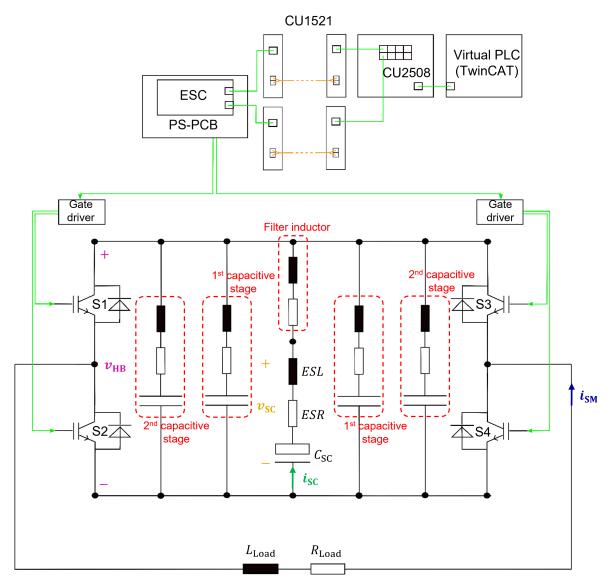

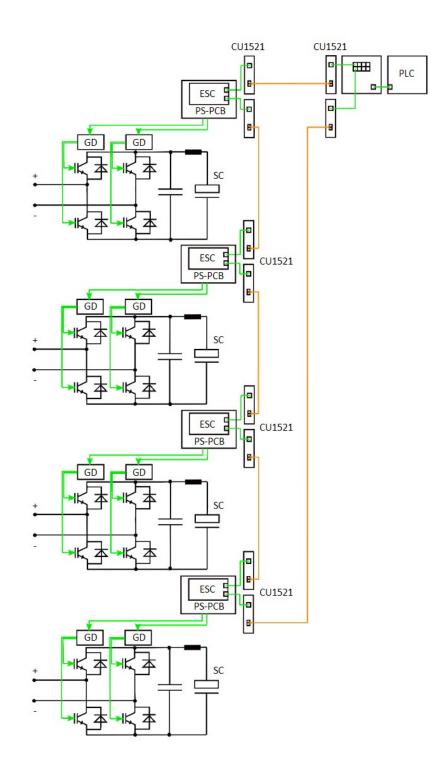

| 5.9  | Equivalent schema of the submodule experimental setup: four CU1521 allow<br>the ring configuration of the communication network. The power stage filter<br>components have been highlighted in red, while the supercapacitors module is<br>represented by its equivalent circuit.                                                                                                                                                                                                                                                           | 77 |

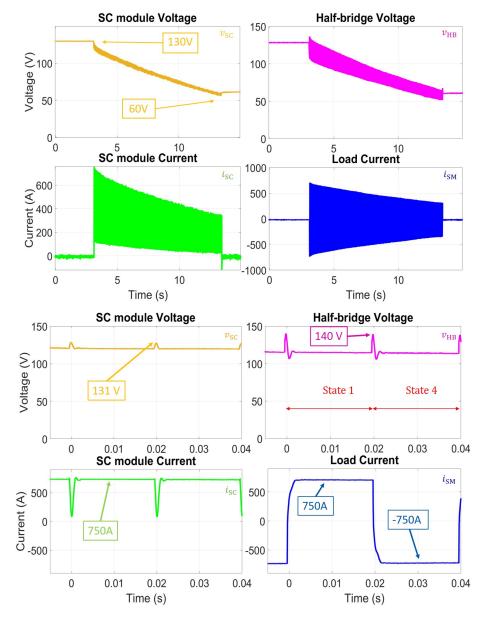

| 5.10 | Single submodule tests experimental results: the upper 4 plots represent the main submodules electrical parameters measured during a typical 130 V / 750 A pulse. The lower 4 curves represent the same parameters but in a different time-scale to observe their behavior during transients                                                                                                                                                                                                                                                | 78 |

| 5.11 | Schematic of the demonstrator: the submodules have been represented with their simplified circuit. The schema does not include any load, since depending on the configuration (serial, parallel or mixed) the load connection can change. The submodules are controlled via the EtherCAT protocol with a ring topology: this is fundamental in the case of the the parallel operation. In case of serial (or mixed) operation, instead of a single ring network, four independent rings (or two) can be used thanks to the port multiplier. | 80 |

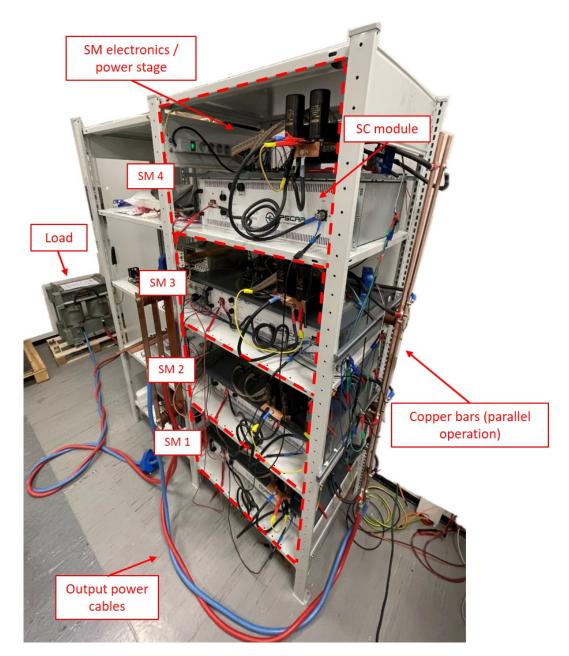

| 5.12 | The 4-SM demonstrator: the rack is composed of four independent sections containing each a submodule. The output terminals of each submodule are on the right side of the rack and they can be connected either via cables or copper bars (as in the photo). The lowest submodule (SM1) is connected to the output power cables connecting the prototype with the load [60]                                                                                                                                                                 | 81 |

| 5.13 | Equivalent circuit of the serial operation experiments: the four submodules -<br>by being in series without any parallel submodules - carry all the load current<br>continuously. This current depending on the state of each submodule flows<br>through two of the four switches of each of them.                                                                                                                                                                                                                                          | 82 |

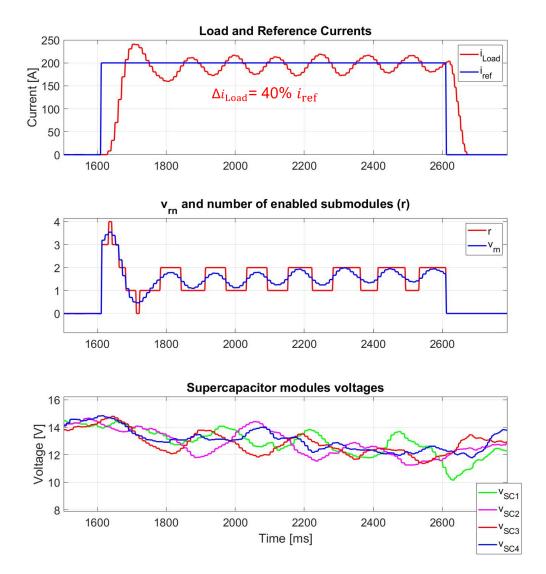

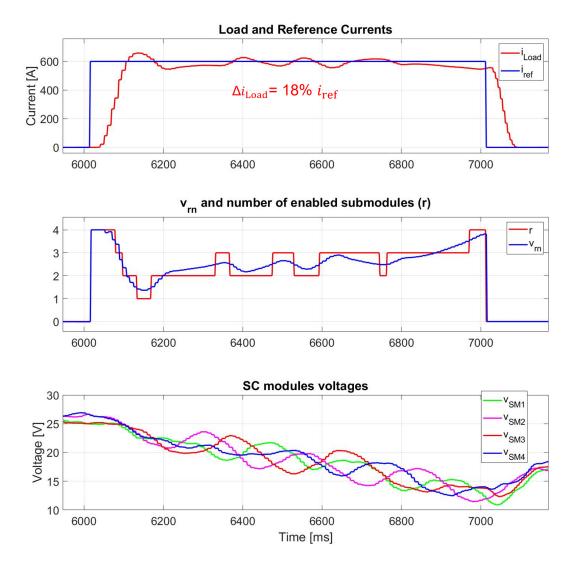

- 5.14 Experimental results of a serial operation pulse: two different tests have been done and compared, to show the controller behaviour with different paramters. The first pulse (shown in this figure) has been done with a reference current of 200 A and supercapacitor modules have been charged at 15 V. The maximum measured load current ripple is 40% of the reference current and during the discharge the controller keeps the number of enabled submodules switching from 1 to 2 constantly due to the slow discharging of the supercapacitors.

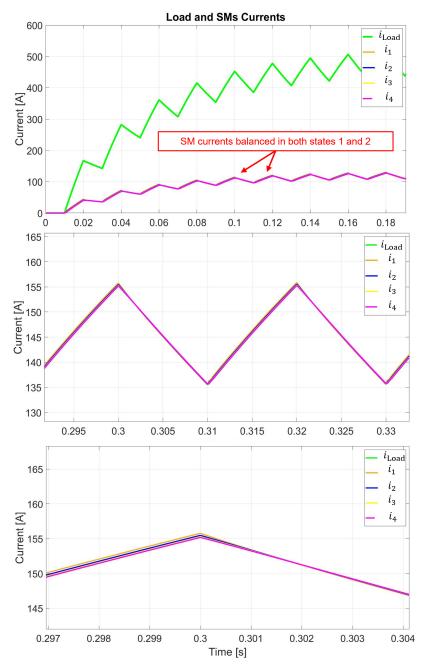

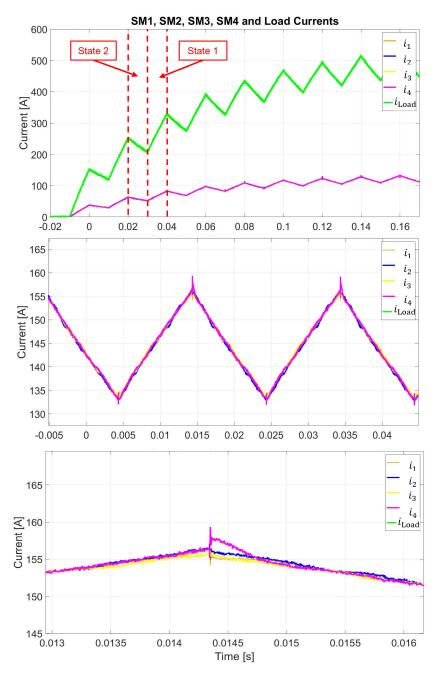

- 5.17 Simulations results of the parallel operated prototype: the four submodules receive the same switching commands to switch synchronously from states 1 to 2 with a switching frequency of 50 Hz. The results are shown in three different time-scales. The upper and central plots show that the load current is evenly shared among the submodules in steady state conditions. In the bottom plot they are shown during a transient.

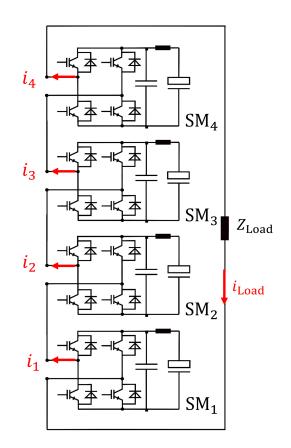

- 5.19 Equivalent circuit of the demonstrator in combined serial/parallel configuration: the submodules in parallel switch together as for the case of the full-scale converter, while the two formed rows are enabled/disabled according to the control strategy. Since the submodules belonging to the same row have the same voltage level, only one supercapacitor module voltage per row has been monitored for the control. 90

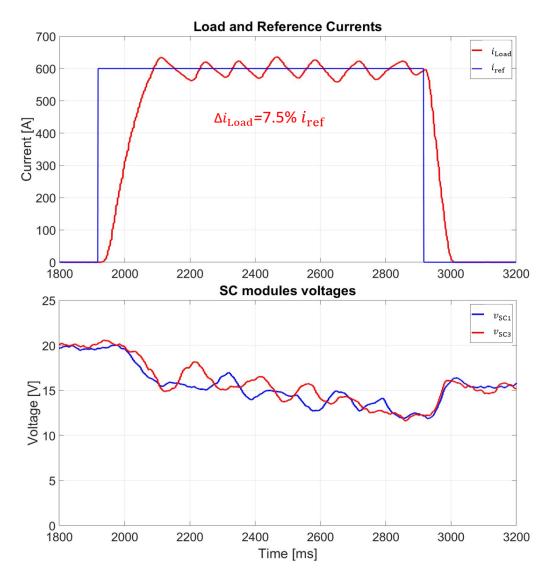

- 5.20 Experimental results of the demonstrator tested in combined serial/parallel operation: the load current follows its reference with a ripple of 7.5% as expected (top plot) and the row voltages (bottom plot) are kept balanced during the 1 s pulse thanks to the voltage balancing algorithm, limiting the maximum voltage displacement to 2.5 V. This value decreases (improving the balancing) by increasing the amount of paralleled submodules due to the higher available energy. 91

84

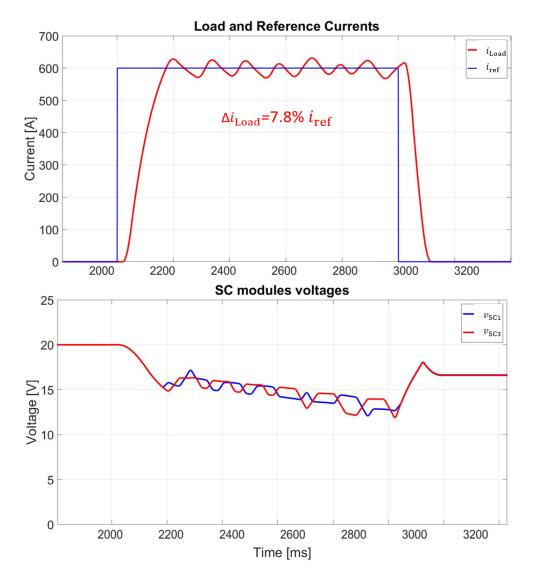

| 5.21 | The same experiment shown in the previous figure has been simulated in PLECS         |    |  |  |  |

|------|--------------------------------------------------------------------------------------|----|--|--|--|

|      | and the results are very similar to the ones obtained experimentally. This validates |    |  |  |  |

|      | the developed full-scale model since the model used for these simulations is an      |    |  |  |  |

|      | adapted version of it                                                                | 92 |  |  |  |

|      |                                                                                      |    |  |  |  |

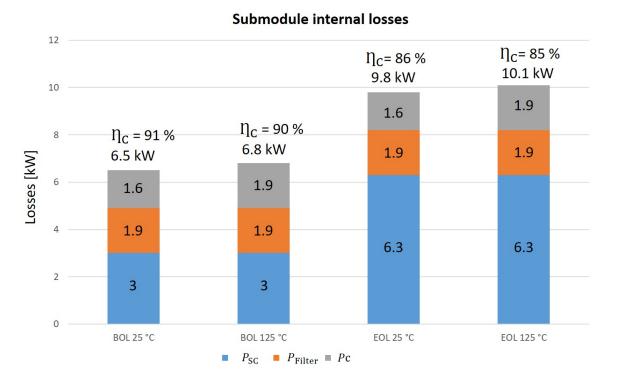

6.1 Estimated submodule internal losses and efficiency for different scenarios: the different values are due to the different state of life of the supercapacitor modules (BOL and EOL) and temperature (25 and 125 °C) considered for the calculations. 94

# **List of Tables**

| 2.1                      | Main ASDEX Upgrade's machine parameters.                                                                                                                                                                                                                                                                                                                                                                                                    |                      |  |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|

| 3.1<br>3.2               | Main data of ASDEX Upgrade's FG: EZ2 is the largest and oldest one<br>Half-bridge submodule states: this configuration can generate only positive                                                                                                                                                                                                                                                                                           | 19                   |  |

| 3.3                      | (State 1) or zero (State 2) output voltage (2-quadrant operation)<br>Full-bridge submodule states: this configuration can generate positive<br>(State 1), negative (State 4) or zero (State 2 and State 3) output voltage<br>(4-quadrant operation); the capability to by-pass the submodule capacitor<br>with two different states allows a well distributed power dissipation leading<br>to a longer lifetime of the semicondutor devices | 29<br>30             |  |

| 4.1<br>4.2               | Main electrical parameters used for the PLECS full-scale converter<br>Main control parameters used for the PLECS full-scale converter                                                                                                                                                                                                                                                                                                       | 48<br>48             |  |

| 5.1<br>5.2<br>5.3<br>5.4 | Main technical data of the used supercapacitors module [55] Main technical data of the used IGBT half-bridge modules [54] Main equivalent parameters of the chosen filter components Main parameters for the performed 130 V / 750 A experiments                                                                                                                                                                                            | 68<br>69<br>71<br>75 |  |

| 6.1                      | Main parameters of the proposed converter                                                                                                                                                                                                                                                                                                                                                                                                   | 96                   |  |

| 8.1                      | List of the publications where the candidate has been the first or one of the main authors.                                                                                                                                                                                                                                                                                                                                                 | 101                  |  |

| 8.2                      | List of supervised students.                                                                                                                                                                                                                                                                                                                                                                                                                | 102                  |  |

# List of Symbols

#### Symbol Unit Description $m^2$ A Area В Т Magnetic field Т $B_{\rm Tor}$ Toroidal magnetic field F Capacitance С Speed of light С m/s Submodule's capacitor capacitance $C_{\rm c}$ F F Filter capacitance $C_{\rm Filter}$ F Supercapacitor capacitance $C_{\rm SC}$ Duty cycle D Electrodes distance d m EJ Energy Error e $E_{S}$ J Stored energy $E_{SC}$ J Supercapacitor energy ESLEquivalent series inductance Η ESR Ω Equivalent series resistance J Short circuit energy $E_{\rm ss}$ TF coil's stored energy J $E_{\rm TF}$ $E_{\rm m}$ J Unused energy $E_{\rm w}$ J Dissipated energy Hz Frequency f **Control frequency** Hz $f_{\rm c}$ Cut-off frequency Hz $f_{\rm co}$ Maximum operating frequency Hz fcr Nominal frequency Hz fN Switching frequency Hz fsw Open-loop transfer function $G_0$ $G_{\rm c}$ Converter transfer function Load transfer function $G_{\text{Load}}$ PI transfer function $G_{\rm PI}$

| Symbol                  | Unit    | Description                            |

|-------------------------|---------|----------------------------------------|

| $G_{ m W}$              |         | Closed-loop transfer function          |

| $H_{\rm s}$             |         | Current sensors transfer function      |

| $I_{\rm ch}$            | А       | Charger current (rms)                  |

| <i>i</i> <sub>epr</sub> | А       | Leakage current                        |

| $I_{\rm TF}$            | А       | TF coil current (rms)                  |

| $i_{\rm Load}$          | А       | Load current                           |

| $i'_{\rm Load}$         | А       | Measured load current                  |

| $I_{\rm P}$             | А       | Plasma current (rms)                   |

| <i>i</i> <sub>pc</sub>  | А       | Pre-charging current                   |

| $\dot{i}_{ref}$         | А       | Reference current                      |

| $\dot{i}_{\rm rs}$      | А       | Short circuit current                  |

| <i>i</i> <sub>SC</sub>  | А       | Supercapacitor current                 |

| $i_{\rm SM}$            | А       | Submodule current                      |

| $i_{\rm ss}$            | А       | Submodule short circuit current        |

| I <sub>ssth</sub>       | А       | Thereshold short circuit current (rms) |

| J                       | $A/m^2$ | Current density                        |

| $k_{\rm p}, k_{\rm ps}$ |         | PI proportional contants               |

| $k_{\rm i}, k_{\rm is}$ |         | PI integral contants                   |

| L                       | Η       | Inductance                             |

| l                       | m       | Length                                 |

| $L_{\rm arm}$           | Η       | Arm inductance                         |

| $L_{\rm c}$             | Η       | Busbars inductance                     |

| $L_{ch}$                | Η       |                                        |

| L <sub>Filter</sub>     | Η       | Filter inductance                      |

| $L_{\rm i}$             | Η       | Internal inductance                    |

| $L_{\rm s}$             | Η       | Stray inductance                       |

| М                       | kg      | Mass                                   |

| т                       |         | Number of parallel submodules          |

| $M_{\rm SC}$            | kg      | Supercapacitor mass                    |

| M <sub>SCtot</sub>      | kg      | Total supercapacitor mass              |

| $M_{\rm tot}$           | kg      | Total mass                             |

| п                       |         | Number of submodules in series         |

| n <sub>c</sub>          |         | Number of cells                        |

| $N_{\rm SM}$            |         | Number of submodules                   |

| $p_{ m c}$              | W       | Conduction losses                      |

| $p_{\text{filter}}$     | W       | Filter losses                          |

| $P_{\rm N}$             | W       | Nominal power (rms)                    |

| $p_{\rm SC}$            | W       | Supercapacitor losses                  |

|                         |         |                                        |

| Symbol                     | Unit | Description                                      |

|----------------------------|------|--------------------------------------------------|

| $p_{\rm SM}$               | W    | Submodule losses                                 |

| $p_{sw}$                   | W    | Switching losses                                 |

| $p_{\Omega}$               | W    | Ohmic losses                                     |

| q                          | С    | Charge                                           |

| r                          | m    | Radius                                           |

| <i>R</i> <sub>arm</sub>    | Ω    | Arm resistance                                   |

| $R_{\rm c}$                | Ω    | Busbars resistance                               |

| $\tilde{R}_{CE}$           | Ω    | Collector-emitter resistance                     |

| R <sub>Chopper</sub>       | Ω    | Chopper resistance                               |

| $R_{eq}$                   | Ω    | Equivalent resistance                            |

| $R_{\rm Load}$             | Ω    | Load resistance                                  |

| $R_{\rm thCH}$             | Ω    | Case to heat sink resistance                     |

| $R_{\rm thJC}$             | Ω    | Junction to case resistance                      |

| S                          |      | Switch                                           |

| S <sub>N</sub>             | W    | Nominal complex power                            |

| <i>s</i> <sub>n</sub>      |      | Switching commands                               |

| $T_{\rm IGBT}$             | °C   | IGBT temperature                                 |

| $T_{\rm FT}$               | S    | Flat-top time                                    |

| $T_{\rm op}$               | °C   | IGBT operating temperature                       |

| t <sub>pulse</sub>         | S    | Pulse time                                       |

| $\hat{T}_{p}$              | °C   | Plasma temperature                               |

| $T_{\rm s}$                | S    | Sampling period                                  |

| $T_{\rm sw}$               | S    | Switching period                                 |

| $T_{\rm thr}, T_{\rm thr}$ | S    | Short circuit detection time via gate drivers    |

| $T_{\rm thSM}$             | S    | Short circuit detection time via current sensors |

| $U_{ m N}$                 | V    | Nominal voltage                                  |

| vc                         | V    | Capacitor voltage                                |

| VCE,ON                     | V    | Collector-emitter ON voltage                     |

| $v_{\rm cf}$               | V    | Filter capacitor voltage                         |

| $v_{\rm ESL}$              | V    | <i>ESL</i> voltage                               |

| $v_{\rm ESR}$              | V    | ESR voltage                                      |

| VGES                       | V    | Gate voltage                                     |

| $v_{\rm Lch}$              | V    | Charger inductor voltage                         |

| $v_{\rm Lf}$               | V    | Filter inductor voltage                          |

| $v_{\text{Load}}$          | V    | Load voltage                                     |

| vout                       | V    | Output voltage                                   |

| Vr                         | V    | PI output signal                                 |

| v <sub>rl</sub>            | V    | Load resistive voltage                           |

| Syr                | nbol | Unit  | Description                                  |

|--------------------|------|-------|----------------------------------------------|

| v <sub>rn</sub>    |      | V     | Normalized PI output signal                  |

| vsc                |      | V     | Superapacitor voltage                        |

| $v_{\rm SC}$       | eop  | V     | Supercapacitor voltage at the end of a pulse |

| $v_{\rm SN}$       | -    | V     | Submodule voltage                            |

| vsc                | min  | V     | Minimum sapacitor voltage                    |

| $v_{ m th}$        |      | V     | Thereshold voltage                           |

| w <sub>i</sub> ,   | Wp   |       | Integral and proportional contants           |

| Ζ                  |      | Ω     | Impedance                                    |

| $Z_{\rm c}$        |      | Ω     | Busbars impedance                            |

| α                  |      |       | Helium nucleus                               |

| $\epsilon$         |      | F/m   | Permittivity                                 |

| $\epsilon_{0}$     |      | F/m   | Permittivity in the free space               |

| $\epsilon_{\rm r}$ |      | F/m   | Relative permittivity                        |

| $\eta$             |      |       | Particle density                             |

| $\eta_{ m c}$      |      |       | Converter efficiency                         |

| Θ                  |      | kg∙m² | Moment of inertia                            |

| ν                  |      | m/s   | Speed of a particle                          |

| π                  |      |       | Pi                                           |

| ho                 |      | Ω·m   | •                                            |

| $	au_{ m c}$       |      | S     | Busbars time constant                        |

| $	au_{ m m}$       |      | S     | Time constant of parallel submodules         |

| $	au_{ m Lo}$      | ad   | S     | Load time constant                           |

| $	au_{ m s}$       |      | S     | Busbars time constant                        |

| $	au_{ m SN}$      | 1    | S     | Sensors time constant                        |

| $\phi_{ m m}$      |      | Deg   | Phase margin                                 |

| $\phi_{ m SC}$     | 2    | -     | Supercapacitor impedance phase angle         |

| ω                  |      |       | Angular speed                                |

| $\omega_{\rm c}$   |      | rad/s | Control angular frequency                    |

|                    |      |       |                                              |

# **List of Abbreviations**

| AC       | Alternating current                              |

|----------|--------------------------------------------------|

| ASDEX    | Axially symmetric divertor experiment            |

| BCP      | Boost-charging phase                             |

| BOL      | Beginning of operational life                    |

| CAES     | Compressed air energy storage                    |

| CS       | Central solenoid                                 |

| D        | Deuterium                                        |

| DC       | Direct current                                   |

| DEMO     | Demonstration power plant                        |

| DTT      | Divertor tokamak test                            |

| ECRH     | Electron cyclotron resonance heating             |

| EES      | Energy storage system                            |

| EOL      | End of operational life                          |

| EPR      | Equivalent parallel resistance                   |

| ESC      | EtherCAT slave controller                        |

| EtherCAT | Ethernet for control automation technology       |

| EZ2      | Energiezentrale 2                                |

| FDU      | Fast discharge unit                              |

| FPGA     | Field programmable gate array                    |

| HEV      | Hybrid electric vehicles                         |

| HVDC     | High-voltage direct current                      |

| ICRH     | Ion cyclotron resonance heating                  |

| IGBT     | Insulated-gate bipolar transistor                |

| IPP      | Max-Planck-Institute for Plasma Physics          |

| ITER     | International thermonuclear experimental reactor |

| MB       | Modulation and balancing block                   |

| MMC      | Modular multilevel converter                     |

| NBI      | Neutral beam injector                            |

| NTC      | Negative temperature coefficient                 |

| PCB      | Printed circuit board                            |

| PCP     | Pre-charging pahse                      |

|---------|-----------------------------------------|

| PF      | Poloidal field                          |

| PI      | Proportional-integral                   |

| PLC     | Programmable logic controller           |

| PPS     | Pulsed power supply                     |

| RFH     | Radio-frequency heating                 |

| SC      | Supercapacitor                          |

| SNU     | Switching network unit                  |

| SM      | Submodule                               |

| SMES    | Superconductive magnetic energy storage |

| STATCOM | Static synchronous compensator          |

| Т       | Tritium                                 |

| TF      | Toroidal field                          |

| UPS     | Uninterruptible power supply            |

# **1** Introduction

# 1.1 Motivation of the dissertation

ASDEX Upgrade is a mid-size tokamak operated at the Max-Planck-Institute for Plasma Physics (IPP) since 1991 [1]. This experimental reactor allows to study the plasma physics in a reactor-like environment, which means that most of the systems studied there are similar (but scaled-down) to the ones that will be used in a future fusion reactor that could generate net energy out of it. Among those systems, the power supply is one of the most challenging ones. ASDEX Upgrade electrical power is provided by three independent flywheel generators which have been built only for this experiment more than 30 years ago. Since the flywheel generators market has changed in the last decades, there exist no present company able to produce nowadays a flywheel generator with a size as large as the largest one ('EZ2') used at IPP. For this reason IPP scientists started to search for alternative power supply systems that could replace one or more of the flywheel generators in case of permanent faults. The first idea consisted in conducting a feasibility study on the adoption of several smaller flywheel generators in parallel to reach the same power required by EZ2, but the outcome of this research was not successful due to synchronization problems [2]. Since modern flywheel generators seem to be not an option, IPP decided to search for a different technology with similar energy and power density: common batteries have higher energy density but too low power density, leading to a huge excess of (unused) energy in order to reach the required power; capacitors on the other hand have a very high power density, but a low energy density. For these reasons it has been decided to investigate on the upcoming technology of supercapacitors, which fits with flywheel generators in terms of both energy and power density. In order to deliver the required power to ASDEX Upgrade coils however supercapacitors are not enough, and a proper power converter is necessary. As it will be shown along the dissertation there exist already some supercapacitors-based power supplies for fusion applications, but all those systems use supercapacitors as a single passive bank and a single powerful converter controls them. This would be the equivalent supercapacitor-based solution of a flywheel generator which would solve the current problem of replacing EZ2, but on the other hand it would present its main concern: any major failure in the supercapacitors bank or in the output converter would affect the whole system and therefore the operation of ASDEX Upgrade would be affected. This concern led to the search of a modular system and

from here the idea of combining together supercapacitors with the modular multilevel converter was born: this converter has several identical small-scale power converter modules (submodules) that can control individually the supercapacitor modules; in this way in case of failure of a single supercapacitor module or submodule, the whole converter would not be affected or it could even continue the operation with a proper fault management. Right now there exists no similar solution as the one described in this dissertation, and for this reason it has been decided to keep the design as much flexible as possible, so that in case of need it can be adapted for different applications.

# 1.2 Organization of the dissertation