# Tailoring Properties of Printed Field-Effect Transistors by Design and Material Changes

Zur Erlangung des Grades eines Doktors der Naturwissenschaften (Dr. rer. nat.) genehmigte Dissertation im Fachbereich Material- und Geowissenschaften von Felix Joachim Neuper aus Hersbruck

Tag der Einreichung: 10. August 2022, Tag der Prüfung: 28. April 2023

Gutachten: Prof. Dr. Horst Hahn

Gutachten: Prof. Dr. Christian Kübel

Darmstadt - D 17

Materials and Earth Sciences Department Gemeinschaftslabor Nanomaterialien Tailoring Properties of Printed Field-Effect Transistors by Design and Material Changes

Doctoral thesis in Materials and Earth Sciences by Felix Joachim Neuper

Review: Prof. Dr. Horst Hahn

Review: Prof. Dr. Christian Kübel

Date of submission: 10. August 2022 Date of thesis defense: 28. April 2023

Darmstadt – D 17

Bitte zitieren Sie dieses Dokument als: URN: urn:nbn:de:tuda-tuprints-240542 URL: http://tuprints.ulb.tu-darmstadt.de/24054

Dieses Dokument wird bereitgestellt von tuprints, E-Publishing-Service der TU Darmstadt http://tuprints.ulb.tu-darmstadt.de tuprints@ulb.tu-darmstadt.de

Die Veröffentlichung steht unter folgender Creative Commons Lizenz: Namensnennung – Weitergabe unter gleichen Bedingungen 4.0 International https://creativecommons.org/licenses/by-sa/4.0/deed.de

# Erklärungen laut Promotionsordnung

## §8 Abs. 1 lit. c PromO

Ich versichere hiermit, dass die elektronische Version meiner Dissertation mit der schriftlichen Version übereinstimmt.

## §8 Abs. 1 lit. d PromO

Ich versichere hiermit, dass zu einem vorherigen Zeitpunkt noch keine Promotion versucht wurde. In diesem Fall sind nähere Angaben über Zeitpunkt, Hochschule, Dissertationsthema und Ergebnis dieses Versuchs mitzuteilen.

## §9 Abs. 1 PromO

Ich versichere hiermit, dass die vorliegende Dissertation selbstständig und nur unter Verwendung der angegebenen Quellen verfasst wurde.

## §9 Abs. 2 PromO

| Die Arbeit hat bisher noch nicht zu Prüfungszwecken gedi | ent.         |

|----------------------------------------------------------|--------------|

| Darmstadt, den 10. August 2022                           |              |

|                                                          | F. J. Neuper |

# Zusammenfassung

Mit der zunehmenden Digitalisierung in allen Lebens- und Arbeitsbereichen inklusive digitaler Kennzeichnung oder gar elektronischer Rückmeldungen von einzelnen Bauteilen oder Konsumartikeln stellt sich die Frage nach neuen Möglichkeiten, Schaltungen schnell und einfach zu produzieren. In diesem Zusammenhang muss auch die Massenproduktion von Transistoren, den Grundbausteinen elektronischer Logiken, neu überdacht werden, um die vergleichsweise aufwändige Produktion von Siliziumchips zu überwinden. Hierbei hat sich das Drucken elektronischer Elemente in den letzten Jahren als vielversprechende Methode hervorgetan. Leiterbahnen, Solarzellen oder Displays sind als gedruckte Elektronik bereits vielfach in industriellen Produktionsprozessen integriert worden.

Im Gegensatz dazu konnten bisher keine verlässlichen Prozesse für gedruckte Transistoren in industriellem Maßstab etabliert werden. Organische und anorganische Halbleitermaterialien haben oft diametral unterschiedliche Eigenschaften: organische Materialien sind in der Regel p-Halbleiter und warten mit einfacher Verarbeitbarkeit und mechanischer Flexibilität auf. Anorganische Systeme sind in der Regel n-Halbleiter, spröde und bedürfen hoher Prozesstemperaturen. Diese Nachteile anorganischer, insbesondere oxidischer Halbleiter, werden jedoch durch die oftmals wesentlich besseren elektronischen Eigenschaften und besserer Umweltstabilität ausgeglichen.

Um besonders niedrige Betriebsspannungen bei trotzdem ausreichend hohen Strömen zu erreichen, empfiehlt sich, die Polarisierung des Kanals über einen Elektrolyt statt eines Dielektrikums umzusetzen, da die Ausbildung von Helmholtz-Doppelschichten lokal sehr starke Felder erlaubt. So können Bauteile mit typischen Spannungen kommerziell verfügbarer Batterien betrieben werden.

Im Rahmen dieser Arbeit konnten erfolgreich neue und verbesserte Methoden für die Darstellung gedruckter Feldeffekttransistoren umgesetzt werden, die die Entwicklung hin zu einer Produktion von Einheiten mit vorhersehbaren Eigenschaften in hohen Stückzahlen unterstützen. Ausgehend von planaren Feldeffekttransistoren mit versetzten Gattern,

wurden drei Verbesserungsmöglichkeiten untersucht: eine vertikale Geometrie, dotierte Kanäle und ein alternativer Elektrolyt.

Der Wechsel von einer planaren zu einer vertikalen Bauweise erlaubt die Kanallängen von der Auflösung der Materialdrucker unabhängig zu machen und auf die Dicken der abgeschiedenen Filme zu reduzieren. Somit können Längen von zweistelligen Mikrometern auf Submikrongröße verkleinert werden. Da die Kanallänge direkt proportional zum Strom an der Senke ist, kann hier eine deutliche Verbesserung erreicht werden. Jedoch muss hierfür der Kanal porös dargestellt werden, um eine große Oberfläche mit Elektrolyt in Kontakt bringen zu können. Hierbei wurde ein bekanntes System mit SnO<sub>2</sub>-Kanal durch eine vereinfachte Darstellungsmethode mit schnell verfügbaren Materialien verbessert und erfolgreich ein funktionales Bauteil dargestellt.

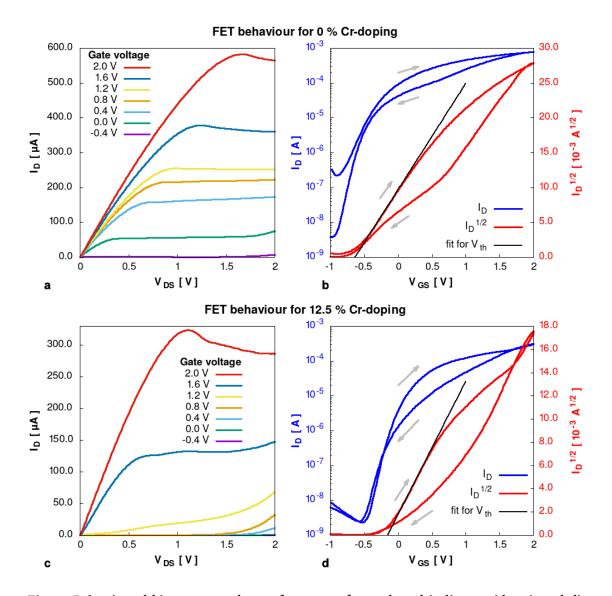

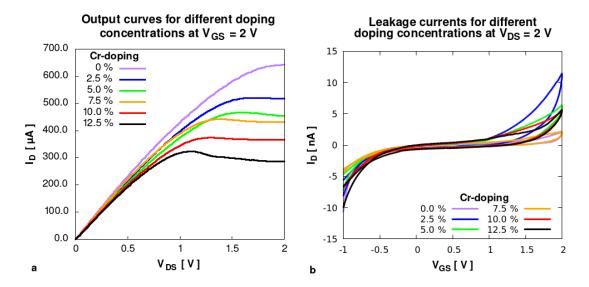

Um die wichtige Kenngröße der Schwellspannung, diejenige Gatterspannung, ab der ein Kanal vom isolierenden in den leitenden Zustand wechselt, verlässlich darzustellen und individuell einstellen zu können, wurde eine In<sub>2</sub>O<sub>3</sub>-Präkursorentinte mit variabler Chromdotierung entwickelt. Durch diese Dotierungen konnte die Schwellspannung linear zur Dotantkonzentration verändert werden, jedoch unter deutlichen Verlusten in den Ausgangsströmen.

In einer dritten Versuchsreihe wurde der üblicherweise genutzte Kompositpolymerfeststoffelektrolyt durch  ${\rm Al_2O_3}$  ersetzt. Statt eines dielektrischen Polarisationsverhaltens resultierte jedoch aufgrund niedriger Synthesetemperaturen im Atomlagenabscheideverfahren ein Material mit geringer Dichte und vielen Hydroxyfunktionalitäten, das als Elektrolyt agiert. In Abhängigkeit der Luftfeuchtigkeit kann die Funktionalität der so erhaltenen Transistoren beeinflusst werden, da die Elektrolyteigenschaft auf an der  ${\rm Al_2O_3}$ -Oberfläche generierten Protonen basiert.

Im Rahmen dieser Arbeit konnten somit erfolgreich drei Alternativen für die Produktion gedruckter, anorganischer Feldeffekttransistoren aufgezeigt werden und ein Beitrag zu Weiterentwicklung dieser Technologie geleistet werden.

# **Abstract**

Due to the increasing digitalization in all areas of life and work, including digital signatures or even electronic feedbacks from single component parts or consumer articles, the question for new possibilities for quick and simple manufacturing of circuits arises. In this respect, also mass production of transistors, the core building units of electronic logics, has to be reconsidered in order to overcome the often complex production of silicon chips. In this scope, printing of electronic components has presented itself as a highly promising method within the recent years. Conductive paths, solar cells, or displays have already been integrated as printed electronics in manyfold industrial production processes.

In contrast to this, so far, no reliable processes for printed transistors in an industrial scale have been established. Organic and inorganic semiconducting materials often have properties with diametral differences: while organic materials use to be p-type semiconductors and come up with simple processability and mechanical flexibility, inorganic systems tend to be n-type semiconductors, brittle and in need of high processing temperatures. These disadvantages of inorganic, especially oxidic semiconductors however are compensated by often severely better electronic properties and increased environmental stability.

In order to achieve very low operation voltages while maintaining sufficiently high currents, it is recommended to realize channel polarization via electrolytes instead of dielectrics, as the formation of Helmholtz double layers allows for locally very high fields. By this, units can be operated at voltages typical for commercially available batteries.

Within the scope of this work new and improved methods for the processing of printed field-effect transistors were successfully implemented, contributing to the development towards large-scale production of devices with predictable properties. Starting form planar field-effect transistors with displaced gates, three possibilities for improvements have been examined: a vertical geometry, doped channels and an alternative electrolyte.

By changing from a planar to a vertical device geometry, channel lengths may become independent from the material printers' resolutions and can be reduced to the thickness of the deposited films. By this lengths may be shrunk from a two-digit micron range to submicron values. As channel lengths are directly correlated with output currents, a severe improvement can be realized. However, in this case the channel must be porous in order to allow a large surface being covered by electrolyte. Within this work, a known system with an SnO<sub>2</sub> channel could be improved by developing a simplified production method with quickly available materials, successfully resulting in a fully functional device.

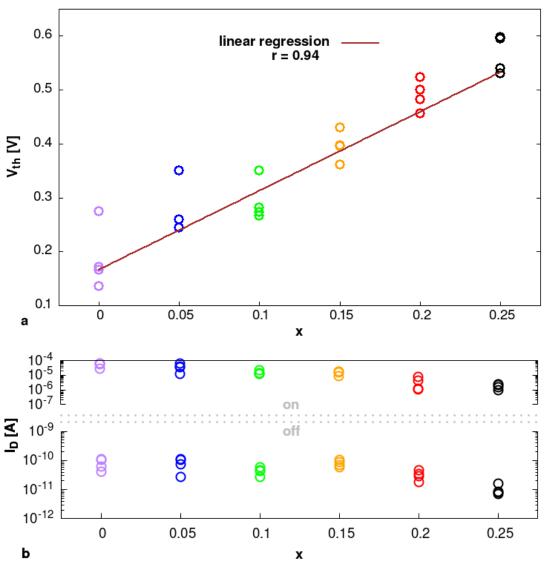

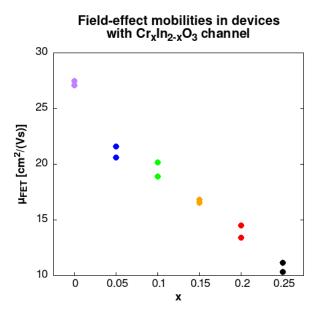

For reliably tailoring the central property of the threshold voltage, i.e., the gate voltage at which the channel changes from an insulating to a conducting state, on a per-device level, an  $In_2O_3$  precursor ink with varying chromium doping has been developed. Through this doping, the threshold voltage could be changed linearly with the dopant concentration, however under severe loss in the output current.

In a third experimental series, the usually applied composite solid polymer electrolyte has been replaced with  $Al_2O_3$ . However, instead of a dielectric gating, a material with low density and many hydroxy functionalities acting as an electrolyte was created due to low temperatures during the atom layer deposition process. Depending on the humidity, the functionality of such transistors can be changed as the electrolytic properties are based on protons generated on the  $Al_2O_3$  surface.

Within this work, three alternatives for the production of inorganic field-effect transistors could be successfully shown and a contribution towards the further development of this technology was made.

# **Contents**

| Lis | st of A | Abbrev  | riations                                                 | xvii |

|-----|---------|---------|----------------------------------------------------------|------|

| 1.  | Intro   | ductio  | on .                                                     | 1    |

|     | 1.1.    | On the  | E Increasing Demand for Printed Field-Effect Transistors | 1    |

|     |         |         | ntion and Outline                                        |      |

| 2.  | The     | oretica | I Background                                             | 7    |

|     | 2.1.    | Field-E | Effect Transistors                                       | 7    |

|     |         |         | Semiconductor Materials                                  |      |

|     |         | 2.1.2.  | The Metal-Semiconductor Contacts                         | 11   |

|     |         | 2.1.3.  | The Field-Effect                                         | 12   |

|     |         | 2.1.4.  | Electrolyte Gating                                       | 15   |

|     |         | 2.1.5.  | Functionality of Field-Effect Transistors                | 17   |

|     |         |         | Operation of Field-Effect Transistors                    |      |

|     |         | 2.1.7.  | Obtaining Key Properties of Field-Effect Transistors     | 22   |

|     | 2.2.    | Printin | ng Technology                                            | 25   |

|     |         |         | Ink-Jet Printing                                         |      |

|     |         |         | Microplotting                                            |      |

|     |         |         | Limitations                                              |      |

|     | 2.3.    | Thin-F  | ilm Deposition Methods                                   | 30   |

|     |         |         | Atomic Layer Deposition                                  |      |

|     |         |         | Sputtering                                               |      |

|     | 2.4.    |         | al Analysis                                              |      |

|     |         |         | X-Ray Diffractometry                                     |      |

|     |         |         | X-Ray Reflectometry                                      |      |

|     |         |         | Thermogravimetric Analysis                               |      |

|     |         |         | Scanning Electron Microscopy                             |      |

|     | 2.5.    |         | d EGFETs in Current Research                             |      |

| 3. | Exp  | erimental Part                                               | 35 |

|----|------|--------------------------------------------------------------|----|

|    | 3.1. | Ink Preparation                                              | 35 |

|    |      |                                                              | 35 |

|    |      | 3.1.2. Composite Solid Polymer Electrolyte                   | 36 |

|    |      | 3.1.3. Precursor for Porous Tin Dioxide                      | 36 |

|    |      | 3.1.4. Commercially Available Inks                           | 36 |

|    | 3.2. |                                                              | 36 |

|    |      |                                                              | 37 |

|    |      | 3.2.2. In-Plane Field-Effect Transistors with Doped Channels | 38 |

|    |      |                                                              | 39 |

|    | 3.3. |                                                              | 40 |

|    |      |                                                              | 40 |

|    |      | • • • • • • • • • • • • • • • • • • • •                      | 40 |

|    |      |                                                              | 40 |

|    |      |                                                              | 41 |

|    |      |                                                              | 41 |

|    |      |                                                              | 41 |

|    | 3.4. |                                                              | 41 |

|    |      | Statistical Analysis                                         | 42 |

|    |      | ·                                                            |    |

| 4. |      |                                                              | 43 |

|    |      |                                                              | 43 |

|    |      | Material Characterization                                    |    |

|    |      | Optimizing the vFET Manufacturing Process                    |    |

|    | 4.4. | Electrical Characterization                                  | 50 |

|    |      | ALD-Coating of the Porous Channel                            |    |

|    | 4.6. | Conclusion                                                   | 58 |

|    |      |                                                              |    |

| 5. |      | 5 1 - 5 7 7 1 5                                              | 59 |

|    |      | Current Research in the Field                                |    |

|    |      | Material Characterization                                    |    |

|    | 5.3. | Electrical Characterization                                  |    |

|    |      | 5.3.1. Devices with two channel layers                       |    |

|    |      | 5.3.2. Devices with four channel layers                      |    |

|    | 5.4. | Conclusion                                                   | 75 |

| 6  | AI D | -Derived Al <sub>2</sub> O <sub>3</sub> as Solid Electrolyte | 77 |

| υ. |      | - ·                                                          | 77 |

|    | 0.1. | Guitent rescarcii iii die l'iciu                             | // |

|    | 6.2.         | Material Characterization of the ALD-Derived Alumina | 78                         |

|----|--------------|------------------------------------------------------|----------------------------|

|    | 6.3.         | Devices with Ag Top Gates                            | 30                         |

|    | 6.4.         | Devices with Graphene Top Gates                      | 81                         |

|    | 6.5.         | Humidity Dependence of Device Characteristics        |                            |

|    |              | 6.5.1. FET Characteristics                           | 83                         |

|    | 6.6.         | Time Dependence of $I_D$                             | 87                         |

|    | 6.7.         | Conclusion                                           | 90                         |

| 7. | Sum          | mary and Outlook                                     | 91                         |

| ٨  | A n.n        | on div                                               | 93                         |

| Α. | App          | endix !                                              | 95                         |

| Α. |              | Cr-Doped Channels with Two Printed Layers            |                            |

| А. |              |                                                      | 93                         |

| Α. |              | Cr-Doped Channels with Two Printed Layers            | 93<br>93                   |

| Α. | A.1.         | Cr-Doped Channels with Two Printed Layers            | 93<br>93<br>94<br>96       |

| Α. | A.1.         | Cr-Doped Channels with Two Printed Layers            | 93<br>93<br>94<br>96       |

| Α. | A.1.         | Cr-Doped Channels with Two Printed Layers            | 93<br>93<br>94<br>96       |

| A. | A.1.<br>A.2. | Cr-Doped Channels with Two Printed Layers            | 93<br>93<br>94<br>96<br>96 |

# **List of Figures**

| 1.1. | Optimization of Printed FETs                                             | 5  |

|------|--------------------------------------------------------------------------|----|

| 2.1. | Band Model                                                               | 8  |

| 2.2. | The Fermi-Dirac Distribution                                             | 9  |

| 2.3. | Doping and Carrier Concentration                                         | 10 |

| 2.4. | Band Bending at Metal-Semiconductor Contacts                             | 12 |

| 2.5. | Layout and Applied Voltages in FETs                                      | 13 |

| 2.6. | Carrier Distribution at Gate-Insulator-Semiconductor Contact             | 14 |

| 2.7. | Ion Distribution in a Biased Electrolyte                                 | 16 |

| 2.8. | Channel Formation in an FET                                              | 18 |

| 2.9. | Typical Output and Transfer Characteristics                              | 21 |

| 2.10 | Typical Leakage Currents                                                 | 21 |

| 2.11 | .Layout of a printed EGFET and Electrolyte Capacitance Schematic         | 23 |

| 2.12 | .Concept of Ink-Jet Printing                                             | 26 |

| 2.13 | .Concept of Microplotting                                                | 28 |

|      | The Coffee Ring Effect                                                   |    |

| 2.15 | Printing Errors                                                          | 30 |

| 2.16 | Schematic of Atomic Layer Deposition                                     | 31 |

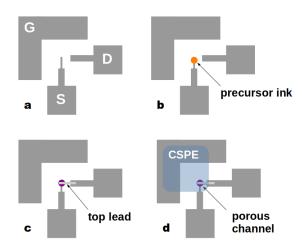

| 3.1. | Production Steps for vFETs                                               | 37 |

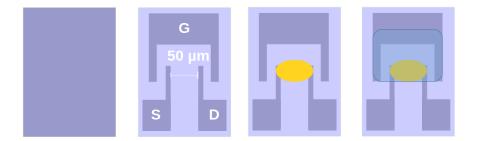

| 3.2. | Production Steps for Cr-Doped FETs                                       | 38 |

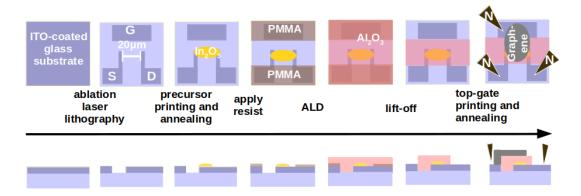

|      | Production Steps for ALD-Gated FETs                                      |    |

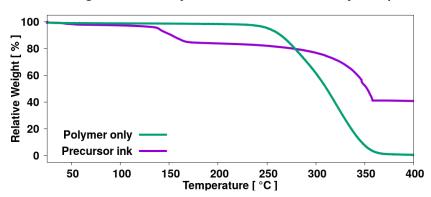

| 4.1. | TGA of vFET Precursor and Template Polymer                               | 45 |

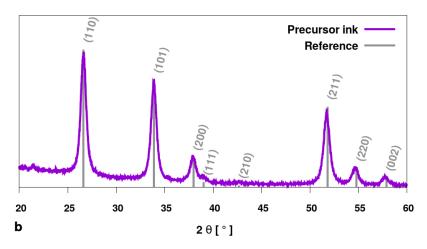

| 4.2. | XRD Powder Pattern of vFET Precursor Ink Residues from TGA               | 47 |

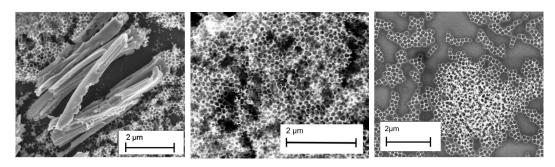

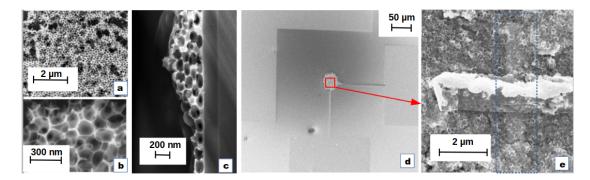

| 4.3. | SEM Micrographs of Precursor Inks with Varying SnO <sub>2</sub> -Loading | 48 |

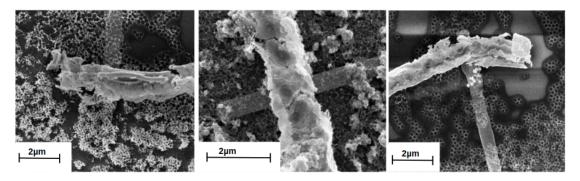

| 4.4. | SEM Micrographs of vFETs with Pd Top Leads                               | 49 |

|      | SEM Micrographs of a vFET Device and Reference Samples                   |    |

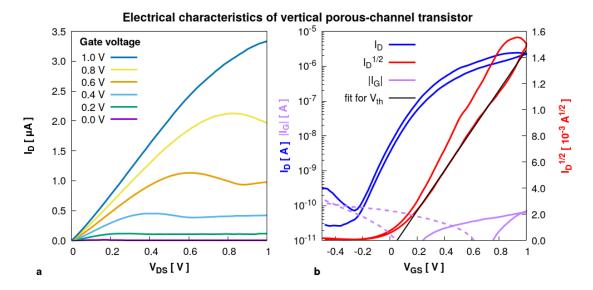

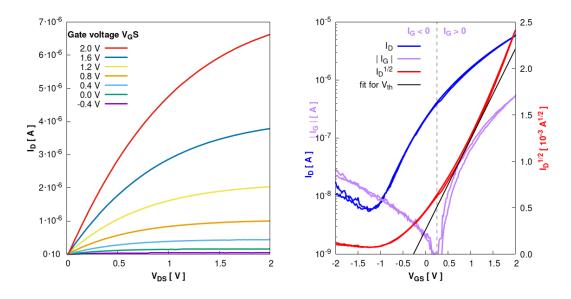

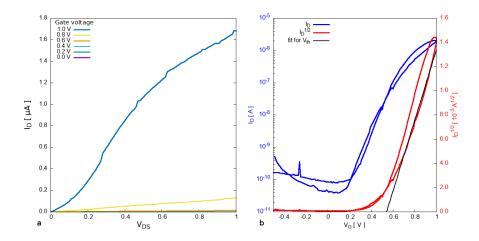

| 4.6. | Electrical Characteristics of a vFET in the 1V-range                     | 51 |

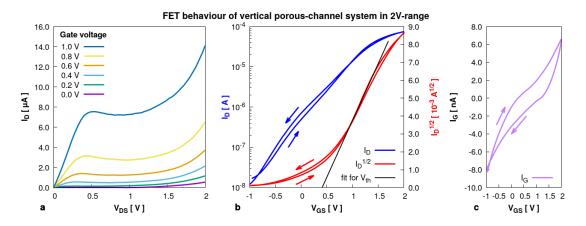

| 4.7. | Electrical Characteristics of a vFET in the 2 V-range                      | 52 |

|------|----------------------------------------------------------------------------|----|

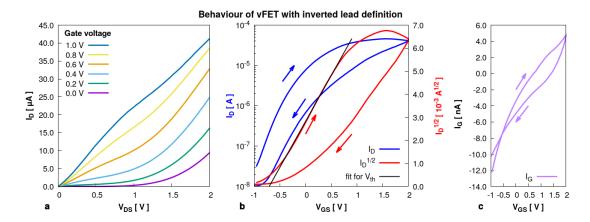

| 4.8. | Electrical Characteristics a vFET with Inverted Lead Definition            | 53 |

| 4.9. | Combined Output Curves of a vFET for Normal and Inverted Operation         | 53 |

| 4.10 | Schematic of Structural Defects in a vFET                                  | 55 |

|      | .Device Characteristics of a vFET in Normal and Inverted Setup             | 56 |

| 4.12 | .SEM Micrographs of ALD-Coated Porous SnO <sub>2</sub>                     | 58 |

|      | Powder XRD Patterns of Cr:In <sub>2</sub> O <sub>3</sub> Samples           | 62 |

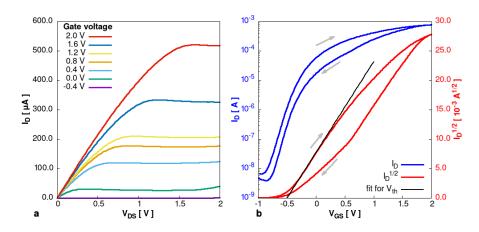

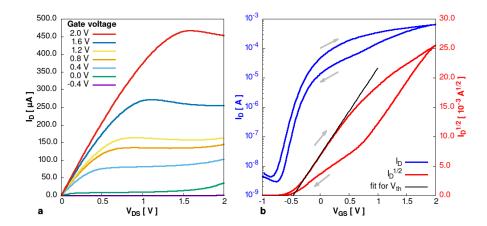

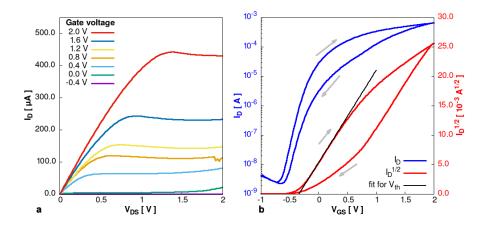

|      | FET Characteristics for Devices with 0% and 12.5% Cr-Doping (2 Layers)     | 65 |

|      | Comparison of Output Curves for Different Cr-Concentrations (2 Layers) .   | 66 |

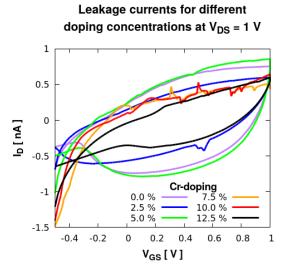

|      | Leakage Currents at Different Cr-Dopant Concentrations (2 Layers)          | 67 |

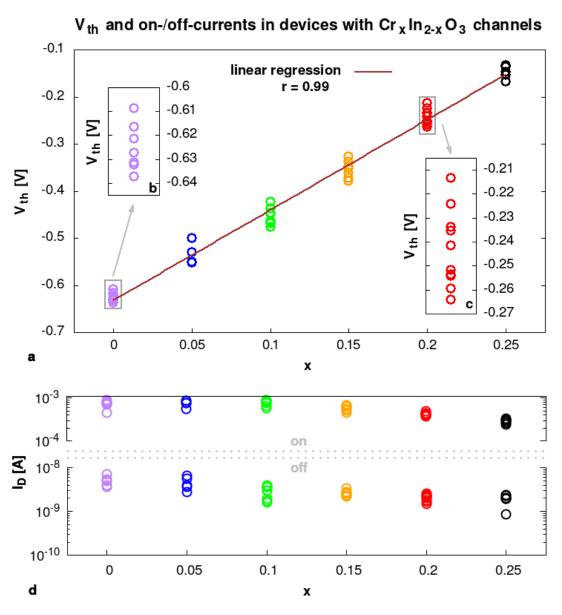

|      | $V_{ m th}$ and on- and off-Currents for Cr-Doped Devices (2 Layers)       | 68 |

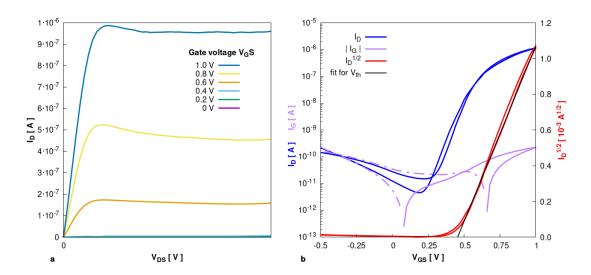

|      | FET Characteristics for Devices with 0% and 12.5% Cr-Doping (4 Layers)     | 70 |

|      | Comparison of Output Curves for Different Cr-Concentrations (4 Layers) .   | 71 |

|      | $V_{\mathrm{th}}$ and on- and off-Currents for Cr-Doped Devices (4 Layers) | 72 |

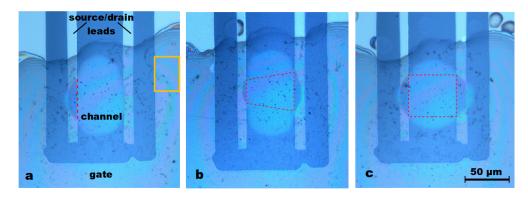

|      | Selection of Devices for $\mu_{\text{FET}}$ Determination                  | 74 |

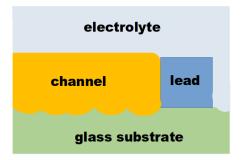

|      | Schematic of Sidewise Contact Between Channel and Lead                     | 74 |

| 5.11 | .Field effect mobilities for different doping concentrations               | 75 |

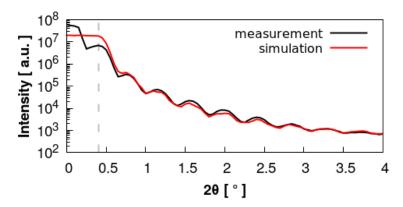

|      | XRR of ALD-Derived $Al_2O_3$                                               | 79 |

|      | FET Characteristics of an ALD-Device with Ag Gate                          | 80 |

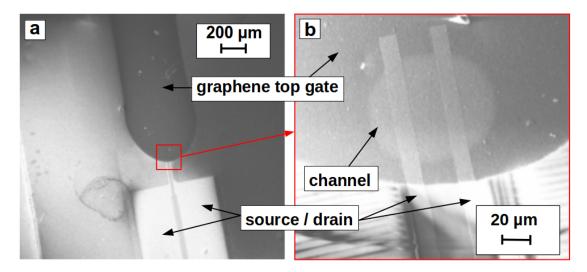

|      | SEM Micrograph of an ALD-Device with Graphene Gate                         | 81 |

|      | FET Characteristics of an ALD-Device with Graphene Gate                    | 82 |

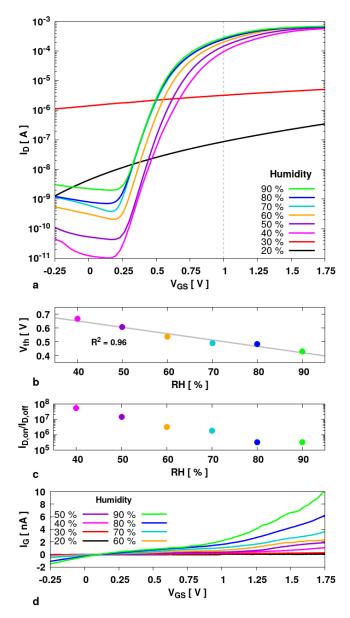

|      | FET Characteristics of an ALD Device at Different RHs                      | 85 |

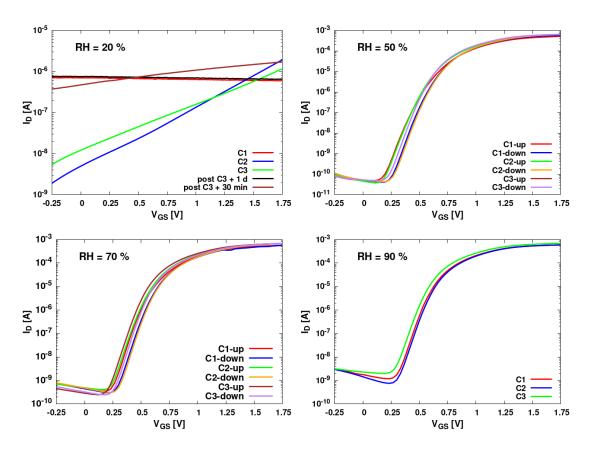

|      | Transfer Curve Stability Upon RH Cycling                                   | 86 |

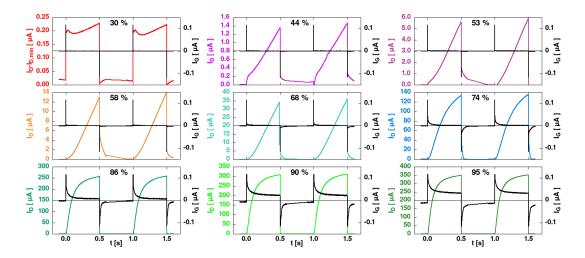

|      | Drain and Gate Currents in Pulsed Measurements at Different RHs            | 88 |

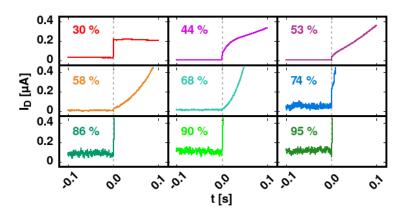

|      | Enhanced View of Drain Current Built-Up in Pulsed Measurements             | 89 |

| 6.9. | Saturation Times after $I_G$ Pulses                                        | 89 |

|      | FET Characteristics for 2.5 % Cr (2 Layers)                                |    |

|      | FET Characteristics for 5.0 % Cr (2 Layers)                                | 94 |

|      | FET Characteristics for 7.5 % Cr (2 Layers)                                | 95 |

|      | FET Characteristics for 10.0 % Cr (2 Layers)                               | 95 |

|      | FET Characteristics for 2.5 % Cr (4 Layers)                                | 97 |

|      | FET Characteristics for 5.0 % Cr (4 Layers)                                |    |

|      | FET Characteristics for 7.5 % Cr (4 Layers)                                |    |

| A.8. | FET Characteristics for 10.0 % Cr (4 Layers)                               | 98 |

# **List of Tables**

| T3.1.Ink Compositions for Cr-Doping            | 35       |

|------------------------------------------------|----------|

| T4.1.Work Function Values for vFET Materials   | 54       |

| T5.1.Cr-Contents in Doped $In_2O_3$ Channels   | 61<br>67 |

| T6.1.Material Properties of $Al_2O_3$ from XRR | 79       |

| TA.1.Data List for Doping Sets (2 Layers)      |          |

# **List of Abbreviations**

ALD atomic layer deposition

complementary metal oxide semiconductor (device) **CMOS**

**CSPE** composite solid polymer electrolyte

D drain

**EBL** e-beam lithography electrolyte gating/gated EG

**EGFET** electrolyte-gated field-effect transistor

FET field-effect transistor

G gate (in devices), gap (for semiconductors)

internet of things IoT

negative differential resistance **NDR OLED** organic light-emitting diode R2R roll-to-roll (processing) relative humidity

RH

S source

scanning electron microscopy SEM

SS subthreshold swing

thermogravimetric analysis **TGA**

threshold th

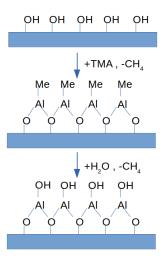

**TMA** triethyl aluminium (Al(CH<sub>3</sub>)<sub>3</sub>)

X-ray diffractometry **XRD** X-ray reflectometry **XRR**

# 1. Introduction

# 1.1. On the Increasing Demand for Printed Field-Effect Transistors

One of the currently heavily forced transitions in industry is the digitalization of work processes at any step from production to management. While this evolution towards computer-based workflows, commonly referred to as digital revolution, is openly visible in office works, as nearly all desk jobs include personal computers nowadays, new aspects have risen in interest lately: data mining and big data, as well as the internet of things.

Data mining hereby means statistical analysis of large information sets ("big data") in order to extract valuable information and patterns. E.g., this is needed for optimizing a production process, predicting customer behavior or even training artificial intelligence systems as well as in the scientific areas dealing with combinatorial synthesis and screening for specific properties in the products. [1]

Internet of things on the other hand refers to enabling direct, digital communication between devices independent of human interaction. [2, 3] While it might sound like an absurdly unnecessary and sci-fi gadget to have one's mixer suggest making banana milk as both the bananas in the fruit basket and the milk in the fridge report being on the verge to spoil, a direct feedback loop from sensor devices (and analyzing the big data amounts they create) can further automatize industrial production processes and allows for real-time adjustments. This is interesting, e.g., in continuous chemical reactors or as one way to flexibly manage urban traffic. On an end-user level, medical applications have come into focus where patients' health data are continuously monitored and the need for medication or iatric intervention is reported in real-time or even applied by an automatic dispenser. [4] Apart from optimizing known processes, a whole new management of supply chains by IoT-technology is anticipated, where each part has a unique identification number – effectively being an internet protocol (IP) address – and can report its spatial position,

position in the production chain, state of passed quality tests and many more properties to the smart, self-organizing factory. [5] With version 6 of the internet protocol (IPv6) formally  $3.4 \cdot 10^{38}$  globally unique IP addresses are possible and even the address space commonly given to a single household already allows for up to  $1.8 \cdot 10^{19}$  unique addresses. [6,7]

This sparks the question on how to apply this unique labeling and the digital logics they require. Processes will have to be able to produce electronic devices in large quantity with high reliability at low unit costs while preferably being attached to flexible substrates to allow applying these intelligent labels to components as adhesive tags or to incorporate them into the packaging. In this respect new materials in combination with printing technology have been established as promising alternative to replace previously industry standard processes that rely on batch-wise production due to the need for high vacuum methods or monocrystalline materials. Currently, technologies such as printed (organic) light-emitting diodes, printed solar cells, printed resistors, printed conductive lines, and printed radio-frequency identification (RFID) antennas already have reached significant industrial application in replacing traditional analogues or are on the verge to do so and even are applied to flexible substrates in many cases. [8–18] With this respect the traditional understanding of printing as recreating text or images from a master needs to be redefined to applying material inks onto a substrate, with focus on material properties rather than the optical appearance of the print result.

For high throughput production, roll-to-roll processing is considered the most relevant option. In R2R a rolled-up, flexible substrate is fed through a printer line and the patterned substrate collected on another roll at the end. Several printing methods are well established and applicable for this. Coarsely they can be classified by whether the substrate is in contact with the printing machine and in how many dimensions the structuring is possible. [19] They include gravure printing, transfer-printing, screen printing, slot-die coating, and flexographic printing and have been vastly applied to produce electronic devices and components. [8, 20–23] Structured layouts are not a necessity in all cases. E.g., for OLEDs or solar cells, spraying or doctor blading can be a valid method for film applications as the aim lies in creating large areas of active material. [24–27]

The aforementioned printing methods suffer from major disadvantages: either they rely on a pattern master that needs elaborate manufacturing or allow no patterning at all. Inkjet printing on the other hand stands out as being a drop-on-demand technology, i.e., ink ejection from a nozzle can be selectively managed and thus patterns need digital masters only. That means it can be freely designed in a software suite. [21] Additionally to full flexibility in patterning, it is a direct writing method, meaning the ink is directly applied,

and thus material losses on patterning masks or master cylinders or because of etching steps are excluded. This makes ink-jet printing especially interesting for applications with many design changes, expensive or sparsely available materials, and use-cases where ink is applied in very low-density patterns. The latter case applies, e.g., in printed ring oscillators, where channel materials only make up a comparably small area of the final devices. [28–30]

In current scientific literature, ink-jet printing is one of the standard techniques for manufacturing printed electronics and due to its versatility can be considered the first laboratory scale method for developing devices before a transfer and scale-up to R2R production is applied. While this scale-up and technology adaption by industry is successful for many electronic components, especially field-effect transistors – the core and key components of any digital logic – have not yet found their way into industrial production by printing methods, despite huge interest from industry and vast research activities in the field.

This can be attributed to a few FET-specific problems and requirements. In general, it can be noted that organic semiconductors can often be dissolved and thus be readily printed, however, their intrinsic mobilities are comparably low. Inorganic SCs on the other hand show good mobilities but either need to be printed as particles, and thus particle-particle contacts limit the overall performance, or they have to be derived from precursors, and as such often need annealing steps that can hardly be combined with using temperaturesensitive flexible polymer or paper substrates and also suffer from brittleness. [31-36] Another factor is that organic SCs usually are p-type while inorganic tend to be n-type. p-type inorganic and n-type organic SCs tend to have mobilities far below the typical values of n-type inorganic and p-type organic SCs, respectively. [37, 38] Thus basic logics, like inverters, that usually rely on complementary metal oxide semiconductor technology face several challenges. But also the printing technology itself sets limits to transistor performances: on the one hand current high-throughput methods are limited in their resolutions. Commonly, drop diameters of an ink-jet printed material are in the range of 20-50 μm. Thus, channel lengths and therefore maximum currents are limited in standard in-plane layout FETs. Performance changes arising from random printing variations challenge the demand for high reproducibility in reliable logic arrays and inflexibility in varying central performance parameters limit the freedom in circuit design. Last but not least printed electronics are targeted to end-user and mobile applications thus battery-driven, low voltage operation is desirable. This makes electrolytic gating a valuable candidate over dielectric gating, as in general lower operation voltages are possible. [39, 40] However electrolytes face new problems in, e.g., environmental stability and long-term reliability.

### 1.2. Motivation and Outline

The focus of this thesis is to provide pathways for tackling the aforementioned challenges printed field-effect transistors are facing and hindering them from being adapted into an industrial-scale application.

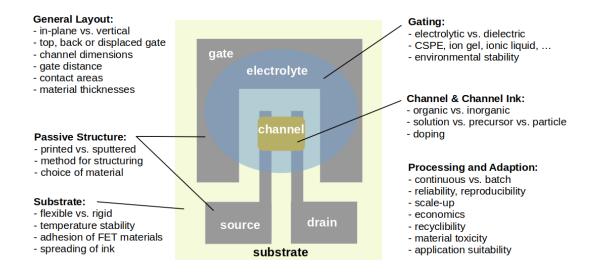

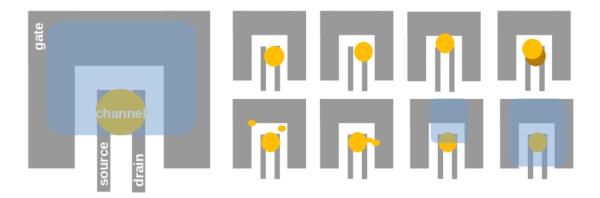

Taking the well-established concept of printed, in-plane, CSPE-gated FETs with displaced gates as starting point, each component as well as the general layout offer manyfold potentials for optimization as shown in fig. 1.1. [41] In general, an FET consists of four different materials, one for each component: the substrate, the passive structure (source, gate, and drain), the channel, and the electrolyte or dielectric. A fifth material may be possible if a top gate, i.e., a conductive element atop the electrolyte and above the channel is introduced. Of course each material selection can be considered separately and shall be discussed briefly here.

In case of the substrate, it must be decided between a rigid or flexible material, if it can withstand the annealing conditions, and if surface treatment is necessary for ensuring proper material adhesion and ink spread. The passive structure can either be printed allowing a continuous process but with drawbacks on conductivity and resolution – or, e.g., sputtered in combination with EBL – a high resolution method but a three-step batch process (structuring, deposition, lift-off). The considerations regarding channel material and ink make-up have been discussed in the previous section, however, the possibility of using doping for shifting semicoductor properties shall be mentioned here explicitly. Gating can be regarded from the method, the material, and the layout side. In case of the method, only two options are available: dielectric gating – typically associated with fast response times – or electrolyte gating – allowing lowering the operation voltage and more feasible for printing. For dielectrics already a vast variety of high- $\kappa$  materials is available, many of which, however, need more elaborate deposition methods. [42] Regarding electrolytes, one has to choose between, e.g., CSPEs, ion gels, or ceramic electrolytes, each coming with different advantages and disadvantages in ionic conductivity, environmental stability and processability. [41] Additionally, different positions of the gate can be regarded: a displaced gate, only possible with electrolyte gating due to the ability of ions moving through the electrolyte. A back-gated system, where a conductive substrate acts as the gate electrode and is covered by a dielectric atop which the printed materials are deposited. And a top gate, as mention earlier, in this case, the gate electrode is placed atop the electrolyte or dielectric. This already leads to more general considerations for the layout itself, which may be in-plane or vertical, and the dimensions of each component both in the plane as well as the perpendicular thickness. Here, for example, short distances

Figure 1.1.: Typical layout of a printed, in-plane CSPE-gated FET with displaced gate and selection of possible optimization considerations

between gate and channel are desirable but bear the danger of creating short circuits during manufacturing, small dimensions are limited by printing resolution, or too sparse material use may limit performance, e.g., too thin metal leads introducing considerable resistances – internally or due to too small contact areas with the channel. Furthermore, printing as deposition method introduces new requirements regarding suitability of a material in ink-form, ink stability or ink composition necessities for the selected printing method. Materials and processes may also not just be optimized separately: contact resistances and possible chemical reactions between the components are to be considered. Beyond the scope of a single device, industrial adaptation will also depend on further factors, e.g., if the process is suitable for scale-up or for high-throughput methods, if the device performance has a reliable window for the properties and low failure rates, and if the materials and devices suit to the desired application, e.g., biocompatibility in medical systems. And of course even factors beyond the actual performance need to be considered, such as pricing and availability of the materials, economics and safety of the processing, and recyclibility of the devices. Often the desired properties and methods may be diametrical to each other, e.g., the good electrical performances of inorganic SCs contrast the desire for flexible substrates, well-performing materials being expensive (e.g. gold as conductor), or design limitations in all-printed devices, just to name a few.

As can be seen, it has to be clearly selected and defined, which properties shall be optimized. Of course, on the level of single-device processing in laboratory scale, the focus on one property may come at the cost of disregarding another. While accepting to stick with rigid substrates, high-temperature processes, and batch processes, three different fields out of the aforementioned optimization parameters have been selected and examined separately.

First of all, the limitations of device performances due to the upper limits of printing resolution have been tackled in a vertically aligned FET, where the channel length is defined by the far smaller film thickness instead of the drop diameter. Chapter 4 describes a new and vastly simplified method for preparation of a vertical channel with highly regular porosity. Advancing from an earlier described system by Baby et. al., the necessary materials could be substituted by chemicals with better availability and manageability, the channel structure be changed to more regular porosity, and the process temperature be reduced. [43]

Secondly, in chapter 5, the problem of reproducibility and predefining of electrical performances in printed FETs have been overcome by the – to the best knowledge of the author – first systematic examination of chemical doping in printed FETs with oxide SCs. Within this chapter, a linear correlation between threshold voltage and Cr dopant content in  $In_2O_3$  is shown, including statistically sound separation between the different device properties.

The third field, examined in chapter 6, introduces an alternative gating based on the highly environmentally stable, yet low-cost,  $Al_2O_3$ . Despite being a ceramic, the material acts as electrolyte with humidity-dependent performance. Performance changes with humidity, including the device reaction times, and the mechanism behind are discussed.

The fundaments for understanding FETs and the methods used within this work are laid in chapter **2**, and the experimental realization described in chapter **3**. Finally, a summary of this thesis and an outlook on future projects based on it can be found in chapter **7**.

# 2. Theoretical Background

Major parts of the theory and functionality of FETs in this chapter are based on the standard textbooks by Neamen, Sze, and Fiore without further mentioning. [44–46]

### 2.1. Field-Effect Transistors

Field-effect transistors are the core unit in current logic devices and silicon technology is based on it. In order to understand how a printed transistor operates, the basic concept of FET functionality must be examined. In a first, simplified view, transistors can be considered as switches that allow or deny, or, more generally, increase or reduce, a current flow between a source and drain electrode. To achieve this, a so-called channel that has a variable resistance which can be influenced depending on a third input signal is necessary.

#### 2.1.1. Semiconductor Materials

The foundation of any transistor is a channel made from a semiconductor, a material class, where availability of free charge carriers, and thus resistance, may be influenced by external stimuli without decomposition.

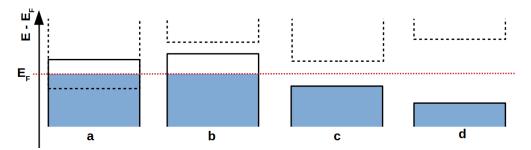

In contrast to conductors, defined by an energetic overlap of the valence and conduction band or partially filled valence bands (fig. **2.1a,b**), and insulators, defined by a large energy gap between valence and conduction bands (fig. **2.1d**), semiconductors have energy gaps ( $E_G$ ) of up to 4 eV (fig. **2.1c**).

Given the Fermi-Dirac distribution (eq. (2.1)) describing the occupation probability p of a particle state with energy E in thermal equilibrium at temperature T, and with the

Figure 2.1.: Band model depiction of a) a conductor with overlapping valence and conduction bands, b) a conductor with a partially filled valence band, c) a semiconductor and d) an insulator;  $E_F$  defines the Fermi level, energies normalized to  $E_F$ , blue colored areas represent filled states for the ground state of the respective material

Boltzmann constant  $k_B$ , the Fermi level is the potential energy level with the occupation probability  $p(E_F) = \frac{1}{2}$ . In a semiconductor this Fermi level is between valence and conduction band and as such usually does not match an allowed particle state.

$$p(E) = \frac{1}{exp(\frac{E - E_F}{k_B T}) + 1}$$

(2.1)

When analyzing eq. (2.1) at absolute zero, one will see that all states with  $E < E_F$  are occupied, while states with higher energies are unoccupied. With increasing temperatures, the probability of occupying states above  $E_F$  is non-zero (fig. 2.2a). Transferring this occupation setup to a semiconductor following the band model from fig. 2.1c results in the generation of electron-hole pairs where each electron that is being promoted to the conduction band and the hole it leaves in the valence band can be used for charge transport as electrons may occupy empty, spatially neighboring states and holes may be occupied by neighboring electrons, respectively (fig. 2.2b-d). That means the concentration of charge carriers can be controlled by temperature or other ways of exciting an electron from the valence to the conduction band, e.g., by photons.

A much more reliable, vastly applied and considerably a key capability of semiconductors is, however, using doping as means to control both the charge carrier concentration as well as the kind of the majority carriers, i.e., whether electrons in the conduction band (n-type semiconductor) or holes in the valence band (p-type semiconductor) are both higher in concentration as their counterpart and mainly contribute to the total current. During

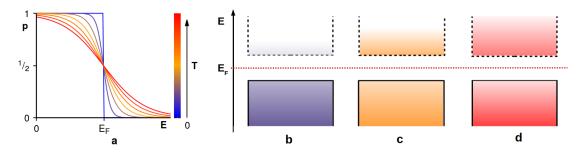

Figure 2.2.: a) Schematic depiction of Fermi-Dirac distributions with the same Fermi level  $E_F$  at different temperatures T, b to d) change in the population of valence and conduction band in a semiconductor with increasing temperatures; temperatures increase as indicated by color

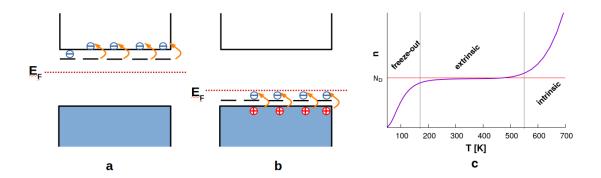

doping new energetic states in the band gap are created, either unfilled (acceptor) states near the valence band or filled (donor) states near the conduction band (fig. 2.3a,b). In general, the concentration of major charge carriers is depending on the concentration of intrinsic carriers, i.e., thermally created ones, and extrinsic carrier numbers that arise from the doping states. It is notably possible to dope with acceptor and donor states in the same material (so-called compensated semiconductor), the effective dopant concentration then arises from the difference in concentration of n- and p-type doping. Based on temperature the influence of intrinsic and extrinsic carriers on the total concentration varies. At very high temperatures, the total concentration is governed by the thermal creation of charge carriers, i.e. intrinsic carriers make up the major part. At intermediate temperatures, the carrier concentration is determined by the effective dopant concentration only, as it can be assumed that all dopant states are ionized and intrinsic carriers have a concentration far below the doping concentrations. That means the concentration is based on extrinsic carriers only. At very low temperatures, the thermal energy is so small that less and less electrons can be promoted from the valence band into acceptor states or donor states into the conduction band, respectively, i.e., full ionization of the doping states is no more given. This temperature range is called the freeze-out region, where thermal effects govern both intrinsic and extrinsic carriers. (fig. 2.3c)

Focusing on n-type devices operated at room temperatures as is done within this work, the total, effective carrier concentration  $n_0$  at thermal equilibrium and under assumption

Figure 2.3.: a) n-doping: electrons from donor states are promoted into the conduction band as charge carriers, b) p-doping: electrons from the valence band are promoted into acceptor states, leaving holes as charge carriers c) temperature dependence in charge carrier density in an n-doped semiconductor with a dopant concentration of  $N_D - N_A$  where  $N_D > N_A$  (after [47])

of total ionization of all dopant states is given as

$$n_0 = \frac{N_d - N_a}{2} + \sqrt{\frac{(N_d - N_a)^2}{2} + n_i^2}$$

(2.2)

where  $N_d$  and  $N_a$  are the concentrations of donor and acceptor states, respectively, and  $n_i$  the intrinsic carrier concentration. Assuming that extrinsic carriers by far exceed intrinsic carriers ( $N_d \gg n_i$ ), this even simplifies to  $n_0 = N_d - N_a$ .

The generation of doping states can be achieved in two ways. Extrinsic doping means incorporating foreign dopant atoms into a crystal lattice with a different number of valence electrons than the atoms they replace. I.e., if a a dopant occupies a cation position and contributes more valence electrons than the atom it replaces (e.g. Sn<sup>4+</sup> on an In<sup>3+</sup> position in indium oxide), it increases the number of electrons in the electronic band, effectively n-doping the system. Analogously, replacing an atom at an anionic position that needs to absorb less electrons to reach its favored ionic state, will likewise increase the number of electrons in the band system, e.g., Cl<sup>-</sup> at the position of O<sup>2-</sup>. For the change in carriers to come into effect, a delocalization of the electron or hole, respectively, into the spread-out molecular orbitals of energy states near the band gap is necessary. This is only possible if the dopant state – which itself is localized to the dopant atom – is energetically close to the conduction or valence band, respectively, so that an electron transfer – which

creates the delocalized n- or p-carrier – is possible at room temperature. If a semiconductor is tolerant towards heavy extrinsic doping without phase separation, it will eventually always have an extremely high number of available carriers for charge transport. In such cases the semiconductor is called degenerate and behaves like a metallic conductor.

Intrinsic doping on the other hand follows from crystallographic defects in non-stoichiometric compounds. In many cases of oxide semiconductors this equals oxygen vacancies, effectively leading to n-type semiconductors as not all electrons from the metal atoms may be bound by a matching non-metal atom. In contrast to extrinsic doping, the number of vacancies is not determined by the stoichiometry of precursor compounds, but rather depends on conditions during synthesis or the synthesis method itself, e.g., the partial pressure of oxygen during sputtering, the temperature during oven annealing, ALD-parameters and overall resulting grain boundary morphologies to name a few. [48]

#### 2.1.2. The Metal-Semiconductor Contacts

In a transistor the current flow between source and drain is mainly based on the conductivity of the channel material which itself is set via an external stimulus. Thus, the properties of the semiconductor play a major role, however, it must not be forgotten, that also the metal leads, and especially the contact between the leads and the channel also influence the transistor characteristics.

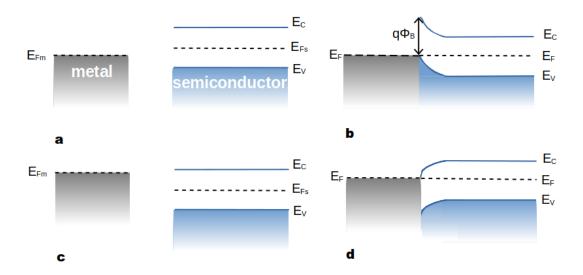

Both, the isolated metal and semiconductor, have specific Fermi levels that are given as material properties but usually differ from each other. This is depicted for an n-type semiconductor in fig. **2.4**. The interconnected system however has a unified system of electronic states and thus a Fermi level of the combined system is formed. This leads to the bands of the semiconductor bending in the contact area depending on whether the Fermi level  $E_{\rm Fm}$  of the metal is lower or higher than the Fermi level  $E_{\rm Fs}$  of the semiconductor.

In the first case, a potential barrier  $\Phi_B$  formed that hinders electron injection from the metal to the semiconductor and a so-called rectifying contact is generated. With the increased energy levels of  $E_C$  at the contact, also the reverse electron flow is hindered by the difference between  $E_C$  in the bulk material and at the contact area. (fig. **2.4a,b**)

In the other case, no potential barrier between the occupied states in the metal and the semiconductor's conduction band is present and thus electron injection is not hindered. (fig. **2.4c,d**)

While the rectifying contacts are used as diodes, transistor applications demand for a seamless transfer of the charger carriers between metal and semiconductor. Therefore, ohmic contacts are preferred there.

Figure 2.4.: a) metal and n-type semiconductor with the Fermi level  $E_{\rm Fm}$  of the metal being lower than the Fermi level  $E_{\rm Fs}$  of the semiconductor, b) once connected, a rectifying contact is formed; c) metal and semiconductor with  $E_{\rm Fm} > E_{\rm Fs}$ , d) once connected an ohmic contact is formed

#### 2.1.3. The Field-Effect

As stated earlier, the charge carrier concentration in a semiconductor may be influenced by external stimuli which is the central property that allows switching between a conductive and insulating state. This external signal may be temperature – as shown in the Fermi-Dirac distribution – or photons with sufficient energy to enhance electrons from the valence to the conduction band. As a result, semiconductors are applied in, e.g., thermometers and photodetectors. In a transistor, however, the external signal is electric. In the case of junction transistors, the resistance of the channel is controlled by a current applied, whereas in field-effect transistors the resistance is voltage-controlled.

As all devices within this work function similar to metal-oxide-semiconductor field-effect transistors (MOSFETs), the focus in the following lies on this type.

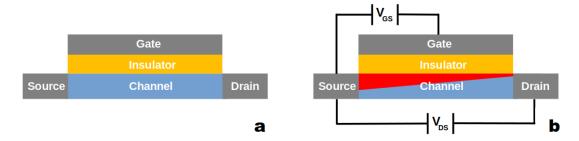

In a MOSFET, the channel is positioned between source and drain and covered by the metal gate electrode over the full length of the channel. Gate and channel are separated by a dielectric which should both be a good insulator and have a very low shielding effect versus electric fields. In fig. **2.5a**, a schematic side view of a typical MOSFET is shown. If a voltage is applied between source and gate, the dielectric insulator becomes polarized and thus influences the energy bands on the channel surfaces. As the gate bias typically is applied relative to the source, the depth of the induced change in carrier concentration is dependent on distance to the source, leading to a profile as shown in fig. **2.5b**. Once  $V_{\rm GS}$  exceeds the threshold voltage  $V_{\rm th}$ , conductivity is given throughout the channel length, and applying a voltage between source and drain can be used for inducing a current. Before a deeper understanding of transistor characteristics is explained in sec. **2.1.5**, it should be understood, how a gate bias leads to changes in carrier concentration in the channel surface.

Figure 2.5.: a) generic layout of an FET device, b) with applied voltages during FET operation, red indicates availability of charge carriers as induced by  $V_{\rm GS}$

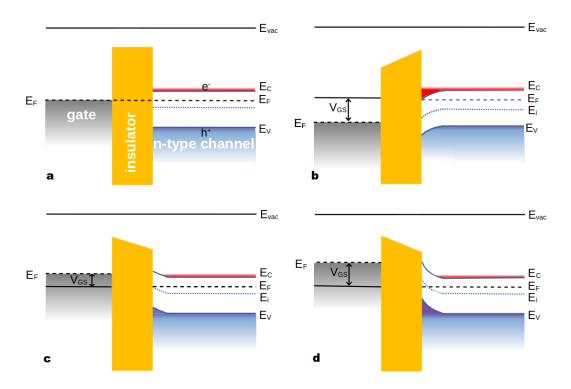

Fig. **2.6a** shows the energetic diagram at a certain position along the channel in the flat band case for an n-type semiconductor. In this ideal situation, the Fermi level of the gate electrode matches the Fermi level of the (n-type) semiconductor and so the number of majority charge carriers in the channel surface equals the value of the (doped) bulk material. A few electron hole pairs exist at room temperature due to the Fermi-Dirac distribution, however the conductivity is governed by the intrinsically available majority carriers. The insulator acts as energetic barrier denying charge carrier transfer between gate and channel. While this situation is unlikely to appear naturally, the flat band case may be reached easily by applying a corresponding voltage to the gate.

Once a positive  $V_{\rm GS}$  is applied the Fermi level of the gate electrode is shifted downwards (fig. **2.6b**), and electrons from the valence band will accumulate at the channel surface and be able to act as additional charge carriers and the channel is highly conductive. This situation is called accumulation mode.

If a negative  $V_{\rm GS}$  is applied, the excess electrons stemming from the doping are removed due to a higher hole concentration. The channel is depleted even of the intrinsically available charge carriers and becomes insulating. The depletion mode is shown in fig. **2.6c**.

As soon as a very low  $V_{\rm GS}$  is applied, the intrinsic energy level at the surface rises above the Fermi level, and thus, the minority carriers have a higher concentration than the majority carriers at the surface. The channel again is conductive. This inversion mode is shown in fig. **2.6d**.

Figure 2.6.: Carrier distributions in the channel at the gate-insulator-channel contact area. a) flat band case, b) accumulation mode, c) depletion mode, d) inversion mode

All devices within this work will be n-type transistors operated in accumulation mode.

### 2.1.4. Electrolyte Gating

In most current applications, the insulator is a dielectric and the system gate-insulator-semiconductor can thus be regarded as a parallel plate capacitor. Any bias  $V_G$  on the gate will induce a charge Q in the channel. The two items are connected by the capacitance C via

$$Q = CV_{\rm G}$$

with:  $C = \frac{\kappa \epsilon_0 A}{d}$  (2.3)

where  $\kappa$  is the dielectric constant/relative permittivity,  $\epsilon_0$  the vacuum permittivity, A the area of the system and d the thickness of the dielectric. While the area is determined by the FET geometry, an ideal insulator has a very small thickness and a high permittivity. The thickness has a lower limit due the breakdown voltage. The permittivity is a material property, and the polarizability depends on the material itself as well as crystallinity, crystallographic orientation, and the chemical composition of the material.

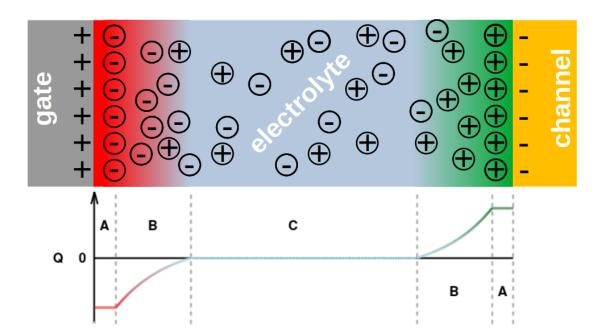

The alterative to this is to replace the dielectric by an electrolyte. In an electrolyte, mobile cations and anions are available. If a bias is applied to the gate, ions will be attracted or repelled at this surface depending on their charge, while the same happens at the electrolyte semiconductor surface with the respective counterions. A schematic of the ion distribution and the charge density in an electrolyte is depicted in fig **2.7**.

The ion distribution on one electrode can be described using the Stern model which combines a rigid Helmholtz double layer at the contact area with a diffuse layer of an exponentially decreasing electric potential and accordingly charge and ion concentrations until the potential drops to 0. This distribution is mirrored on the other side with the complementary charges.

Especially the Helmholtz layer can be considered as a very high-capacitance system according to eq. (2.3), as the effective distance between the charges are in the single-particle size range.

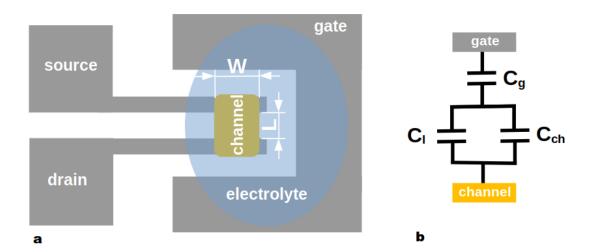

As the ions can move through the electrolyte along electric fields, it is possible to go away from the sandwiched structure of channel-dielectric-gate and use a displaced-gate, in-plane geometry, where the gate is located next to the channel and both are covered with the electrolyte. A schematic of such a device is shown in fig. **2.11**.

Figure 2.7.: top: schematic of ion distribution in the electrolyte with a positive bias applied at the gate: anions are attracted to the gate and cations are pushed to the channel, inducing a negative charge; bottom: corresponding charge density with (A) Helmholtz double-layer, (B) diffuse layer with exponential charge decline, (C) neutral electrolyte with matching numbers of ions and counterions

Due to the liquid nature of the electrolyte, it may not only be printed but is also highly conformative towards the channel surface. In general, electrolyte gating allows for lower gating voltages due to the strong field in the Helmholtz double layer easily inducing a conductive channel. The concepts for the polarization of charge carriers in the semiconductor as described in the previous section still apply.

Often the electrolytes are composite solid polymer electrolytes, that offer a solid polymer backbone instead of a liquid system. These CSPEs have seen various applications in both batteries as well as printed FET technology. [41, 49]

Using protons instead of salts as ions for electrolyte gating has been shown in water-gated devices. [50, 51] Notably ion movement here is governed by the Grotthus mechanism, that describes hopping of protons between water molecules and is considerably faster

than the actual movement speed of a specific proton. [52] This mechanism may also be expanded from solutions to surfaces with protic or proton-accepting functionalities or absorbed protic solvents. [53]

### 2.1.5. Functionality of Field-Effect Transistors

When operating an FET, one major question is when does the semiconductor change from an insulating to a conductive state – or to be more precise – when does the channel form as conductive path between source and drain electrode. The necessary gate voltage to form this is called threshold voltage  $V_{\rm th}$  and is a unique property of each individual device and prone to manyfold influences. Just to name a few, it is e.g. dependent on the channel material, its orientation and crystallinity, the gate insulator material and thickness, or the contact quality between insulator and semiconductor. While often semiconductor and channel are used interchangeably, *semiconductor* describes the material and building element, while *channel* strictly speaking only stands for the regions in a semiconductor that have excess charge carriers available that may be used to create a current.

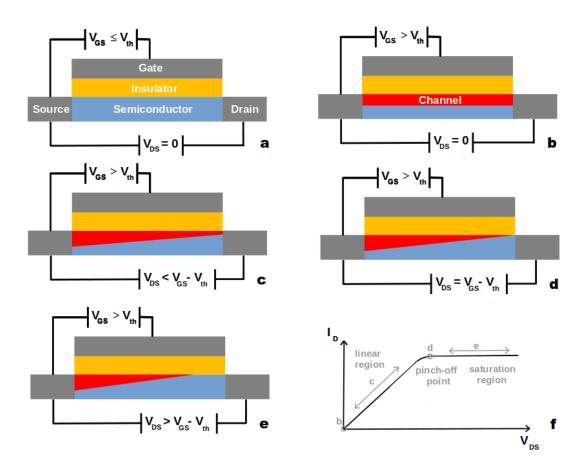

In fig. **2.8**, the different modes of the channel depending on  $V_{\rm GS}$  and  $V_{\rm DS}$  are depicted for an n-type device. In the first case (a), the gate voltage is below the threshold voltage and no channel is created. As explained in the previous section, formally for lower gate voltages, the inversion mode conductivity is possible then, but not further regarded here. In the second case (b), the channel is equally formed at the semiconductor surface. Once a drain voltage is applied (c) a profile with a smaller channel towards the drain contact is formed since electrons are extracted. This may also be understood as the drain voltage polarizing the channel contrary to the gate bias. The carrier density Q at a given point x along the channel – which spans from 0 to length L – is given as:

$$Q(x) = C'(V_{GS} - V_{th} - V(x))$$

(2.4)

where C' is the areal double layer capacitance at the semiconductor insulator contact and V(x) the voltage between x and the drain. At the pinch-off point (d), Q(L) drops to 0, and a further increase of  $V_{DS}$  (e) will not increase the current as all available charge carriers are already contributing to  $I_{D}$ .

Fig. **2.8f** shows a typical I-V-characteristic, also-called output curve, of an n-type semi-conductor at a given  $V_{\rm GS} > V_{\rm th}$ .  $I_{\rm D}$  may be derived from eq. **(2.4)** by knowing that the local current density J(x) is a function of the carrier densities and their drift velocity

Figure 2.8.: Distribution of the channel at varying  $V_{\rm GS}$  and  $V_{\rm DS}$  settings: a) no channel is formed, b) channel is equally distributed, c) linear-region: channel becomes smaller towards drain contact, but still is established though the whole length d) pinch-off point: channel vanishes at drain contact e) saturation region: channel vanished before drain contact, a pinch-off region without channel is formed; f) typical I-V-characteristic with indicators which channel schematic applies

$v_{\rm n}$ . Note that in the following, channel polarization will be assumed as being a pure surface phenomenon and thus the depth of the polarization is regarded as constant and small and will be factored in the spatial and areal values for charge and current density,

respectively, and be denoted as Q'(x) and J'(x).

$$J'(x) = Q'(x)v_n \tag{2.5}$$

The drift velocity itself is a function of the electric field E (in this case between source and drain) and the electron mobility  $\mu$ . The latter is a material property that describes the relation between electric field and drift velocity and may be regarded as a term describing internal movement restrictions of charge carriers.

$$v_n = \mu E = \mu \frac{\mathrm{d}V(x)}{\mathrm{d}x} \tag{2.6}$$

Substituting eqs. (2.5) and (2.6) into eq. (2.4), forms

$$J'(x) = C' \mu \frac{dV(x)}{dx} (V_{GS} - V_{th} - V(x))$$

(2.7)

The current densities may now be transformed to the current via the channel width W, as I = I'W. Using this relation and separation of variables, eq. (2.7) may be integrated:

$$I \int_{0}^{L} dx = C' \mu W \int_{0}^{V_{DS}} (V_{GS} - V_{th} - V(x)) dV(x)$$

(2.8)

Leading to the description of the I-V-curve:

$$I_D = C' \frac{W}{I_c} \mu ((V_{GS} - V_{th}) V_{DS} - \frac{1}{2} V_{DS}^2)$$

(2.9)

The linear region can now be described by assuming that  $V_{\rm DS} \ll V_{\rm GS} - V_{\rm th}$  and thus neglecting the quadratic term in eq. (2.9) leading to the linear function in  $V_{\rm DS}$ :

$$I_D = C' \frac{W}{I} \mu (V_{\rm GS} - V_{\rm th}) V_{\rm DS}$$

(2.10)

At the pinch-off point,  $V_{\rm DS}$  equals  $V_{\rm GS}-V_{\rm th}$  and thus the saturation current is given as:

$$I_{\text{D,sat}} = \frac{C'W}{2L} \mu (V_{\text{GS}} - V_{\text{th}})^2$$

(2.11)

To be more precise, the mobility  $\mu$  should be replaced by the field-effect mobility  $\mu_{FET}$  of the same dimension. This value represents the effective mobility of an individual device that is dependent not only on the ideal mobility of the material, but as well as manyfold factors, e.g., semiconductor crystallinity and grain sizes, electrical grain contacts, channel dimensions, or metal semiconductor contact. In general, the field-effect mobility is highly process-dependent.

## 2.1.6. Operation of Field-Effect Transistors

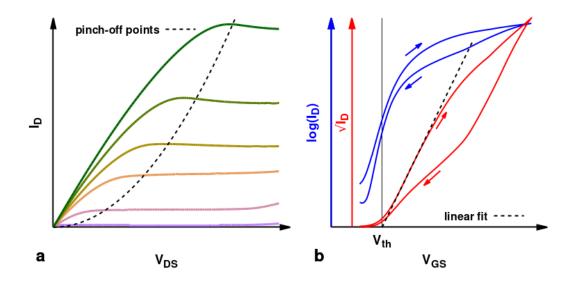

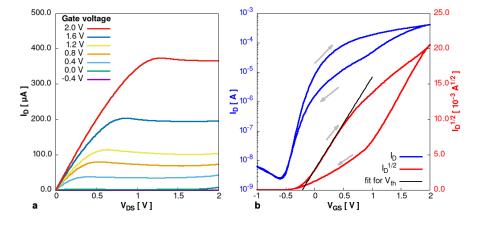

Fig. **2.9** shows typical device characteristics of a printed EGFET. In (a) a series of output curves with increasing  $V_{\rm GS}$  is shown, whereas for the purple graph  $V_{\rm GS}$  is still below  $V_{\rm th}$  and thus there is no current. The dotted line is the quadratic function of the positions for the pinch-off points where the saturation current is reached as described in eq. (2.11).

When a transistor is operated with a constant  $V_{\rm GS}$ , the transfer characteristic is obtained by varying  $V_{\rm GS}$  as shown in (b). It is typical for electrolyte-gated devices to show a certain hysteresis when  $V_{\rm GS}$  is swept up and down. This can be attributed to a delayed response of the ionic movements to the gate bias, or ions and charge carriers being tapped in locally favorable states (trap states). [54] Saturation in  $I_{\rm D}$  versus  $V_{\rm GS}$  occurs due to the limitations of channel polarization.

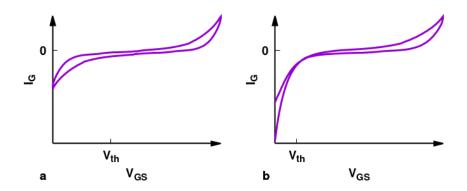

Outside a certain range for  $V_{\rm GS}$ , the electrolyte will be electrochemically decomposed, generally this is visible in an increased (absolute) value for the gate current  $I_{\rm G}$ , a value describing leakage into the gate electrode. In dielectric-gated devises leakage current may occur due to pinhole connections or beyond the breakdown voltage of the insulator. A schematic of typical leakage currents are shown in fig. **2.10**. In case **(a)**, the electrolyte is stable, case **(b)** corresponds to fig. **2.9b**. In a reasonable device leakage currents must be several orders of magnitude smaller than  $I_{\rm D}$  in order to ensure a clear differentiation between on- and off-states.

Figure 2.9.: Typical device characteristics; a) output curves at increasing  $V_{\rm GS}$ , in the case of the purple graph,  $V_{\rm GS}$  is below  $V_{\rm th}$  and no current present, the dotted graph marks pinch-off points, where  $V_{\rm DS}=V_{\rm GS}-V_{\rm th}$  (see eq. (2.11); b) transfer characteristics (blue) and square root of  $I_{\rm D}$  (red) with linear fit for determining  $V_{\rm th}$  at  $I_{\rm D}=0$

Figure 2.10.: Typical leakage current curves, a) electrolyte is stable within operational range, b) electrolyte is decomposed at lower voltages (curve matching to fig. **2.9b**)

## 2.1.7. Obtaining Key Properties of Field-Effect Transistors

### **Threshold Voltage**

As should be obvious by now,  $V_{th}$  is a key property of FETs. It may be obtained by rewriting eq. (2.11) as

$$\sqrt{I_D, sat} = \sqrt{\frac{C'W}{2L}} \mu_{\text{FET}} \left( V_{\text{GS}} - V_{\text{th}} \right)$$

(2.12)

creating a linear correlation between  $I_{D,sat}$  and  $V_{GS}$ , with  $V_{th}$  easily determined at  $I_D = 0$ . In fig. **2.9b**, this fit is already shown. This so-called square root method approach allows for fitting a simple function to a reasonable large amount of data points and thus can be considered as stable versus statistical measurement variations.

## Field-Effect Mobility

With the linear fit,  $\mu_{\text{FET}}$  may be extracted from the obtained slope a via

$$a = \sqrt{\frac{C'W}{2L}\mu_{\text{FET}}} \Rightarrow \mu_{\text{FET}} = \frac{2a^2L}{C'W}$$

(2.13)

For this the areal capacitance C' and the geometry values W and L have to be known. Fig. **2.11a** depicts a typical layout of a printed, in-plane, displaced gate, electrolyte-gated field-effect transistor. Source, drain and gate are made from a conductor, the printed channel interconnects source and drain leads, and a printed electrolyte covers both, the channel and gate, and ideally as little of the source and drain leads as possible. As the sizes for W and L in this work usually lie in the two-digit micron range, these two values may be obtained from an optical microscope.

The determination of C' on the other hand is more complex. As explained in sec. **2.1.4**, each electrode-electrolyte-contact site acts as a capacitor, thus the system gate-electrolyte-channel can be considered as two capacitors in series. However, often it is not possible to fully exclude contact between the electrolyte and the source or drain leads, as shown in fig. **2.11a**. Therefore on the capacitance on the channel side consists of two capacitors

Figure 2.11.: a) typical layout of a printed electrolyte-gated field-effect transistor with channel width W and length L indicated; b) circuit depiction of the capacitors in the gate-electrolyte-channel/leads system with capacitances between electrolyte and gate ( $C_g$ ), source/drain leads ( $C_l$ ), and channel ( $C_{ch}$ ), respectively

in parallel stemming from the channel and lead contact areas, respectively. The total capacitance  $C_{\rm tot}$  can be measured by short-circuiting source and drain and applying a bias versus the gate.  $C_{\rm tot}$  now can be expressed as

$$\frac{1}{C_{\text{tot}}} = \frac{1}{C_{\text{g}}} + \frac{1}{C_{\text{l}} + C_{\text{ch}}}$$

(2.14)

As the contact area on the gate side is very large, so is the capacitance there, and thus  $C_g \gg C_l + C_{ch}$  making  $1/C_g$  negligible in the above equation:

$$C_{\text{tot}} = C_{\text{l}} + C_{\text{ch}} = C_{\text{l.ar}} A_{\text{l}} + C' A_{\text{ch}}$$

(2.15)

$$\Rightarrow C' = \frac{C_{\text{tot}} - C_{\text{l,ar}} A_{\text{l}}}{A_{\text{ch}}}$$

(2.16)

Where  $C_{l,ar}$  and C' are the areal capacitances of the leads and channel, respectively.  $A_l$  and  $A_{ch}$  are the corresponding contact areas which, again, can be gained from optical measurements.  $C_{l,ar}$  must be obtained from reference devices no channel. Applying the same logic as eqs. **(2.14)** and **(2.15)** when neglecting  $C_{ch}$  in fig. **2.11b**, it follows that

$$\frac{1}{C_{\text{tot,ref}}} = \frac{1}{C_{\text{g}}} + \frac{1}{A_{\text{l,ref}}C_{\text{l,ar}}} \wedge C_{\text{g}} \gg C_{\text{l}}$$

(2.17)

$$\therefore C_{l,ar} = \frac{C_{tot,ref}}{A_{1,ref}}$$

(2.18)

$C_{\text{tot,ref}}$  and  $A_{\text{l,ref}}$  again can be obtained from electrical or optical measurements, respectively.

It should be noted that despite C' seemingly being a material property, it should still be obtained individually for each device to ensure that possible process variations are taken into account.

#### **Drain Current On-Off-Ratio**

For a good differentiation between an open and a closed channel, the ratio between the currents in the on- and off-state,  $I_{\rm D,on}/I_{\rm D,off}$ , is of relevance, where  $I_{\rm D,on}$  and  $I_{\rm D,off}$  are the maximum and minimum currents in a transfer graph, respectively. Usually this should span several orders of magnitude.

## Subthreshold Swing

As can be seen in fig. **2.9b**,  $I_D$  is already rising before the threshold voltage is reached. While this rise is small in absolute numbers ( $I_D$  is depicted on a logarithmic scale), this so-called subthreshold swing describing the rise between the minimum drain current  $I_{D,\min}$  and the current  $I_{D,th}$  at  $V=V_{th}$  is an indicator for surface trap states. [55] It is determined in terms of voltage change per decadic change of the current as

$$S = \frac{d V_{GS}}{d \log_{10}(I_D)}$$

(2.19)

but may also be described using the double layer capacitance of the gating material  $C_{\rm dl}$  and the capacitance contribution from trap states  $C_t$  at a given temperature T:

$$S = ln(10)\frac{k_{\rm B}T}{q} \cdot \frac{C_{\rm dl} + C_t}{C_{\rm dl}}$$

(2.20)

In an ideal device, no surface traps exist, and thus  $C_t = 0$ . This allows calculating the theoretical lower limit of S, which at room temperature is  $60 \frac{mV}{dec}$ .

# 2.2. Printing Technology

For fully understanding printed FET technology, not only the basics of FETs, but also the borders set by the printing technology must be understood. Laboratory scale printing often means having variable layouts and many varying inks, possibly expensive or in need of an effortful synthesis, and thus only available in sparse amounts. For this reason, printing methods that allow using little amount of ink, applying it directly onto the substrate, and easily changing the printing design have established themselves in the first step of research on printed materials. Within this work ink-jet printing and microplotting is applied and hence a deeper understanding of these technologies is necessary. Both are drop-on-demand technologies, i.e., the ejection of a droplet can be individually controlled and thus the deposition may occur both contactless and by applying any digitally designed pattern. This makes drop-on-demand technologies highly versatile towards design changes and besides a digital design no actual physical template needs to be produced.

## 2.2.1. Ink-Jet Printing

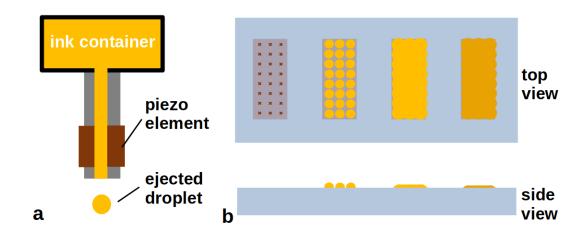

In ink-jet printing, a print head is equipped with nozzles that have piezoelectric crystals attached. Once the print head has reached the correct position over the substrate, the piezo element is used for squeezing out ink as desired. In fig. **2.12** schematics of the nozzle and the steps during printing are depicted. When printing with an ink-jet system, first, the design is created digitally and ink deposition points are defined in the structures. After deposition, the droplets will spread on the substrate, depending on the interactions between ink and substrate, as well as drying speed, and merge to form the desired structure. Eventually, the ink will dry fully. Optionally the substrate may be heated during

Figure 2.12.: a) jetting nozzle of an ink-jet printer b) steps during ink-jet printing on a substrate (blue) with top (top) and side (bottom) view; from left to right: digitally designed pattern with calculated ink deposition positions, drop pattern directly after deposition, ink spreads and droplets combine to continuous pattern, final structure after ink has fully dried

deposition in order to speed up the drying process, which may also be used to influence the spreading. Deposition point distances can be varied according to the expected spread radius after deposition. If desired multiple layers may be deposited.

For creating a good and sharp pattern, it must be ensured that the interaction between ink and substrate neither leads to the ink spreading out too far nor a lotus effect. If the interaction is too repellent, the droplets may merge into a single large drop, if the spreading goes too far, the structures become too large. In either case the thickness of the films will also be outside the desired values. E.g., a better interaction with polar inks may be reached by treating the substrate in an oxygen plasma before deposition.

Drop sizes of the system used within the scope of this work are in the 10 pL range. The diameter of a single dried-in droplet will therefore be in the lower two-digit micron range and the resolution of the patterns is limited by this value.

To ensure good printability, the inks must lie within the approximate window of  $1 \le Z \le 10$  where Z is a function of the density  $\rho$ , surface tension  $\sigma$ , and viscosity  $\mu$  of the ink as

well as the diameter *d* of the drops. [56]

$$Z = \frac{\sqrt{\rho\sigma d}}{\mu} \tag{2.21}$$

Inks outside this window may either be too viscose to be ejected, too thin to be retained even if no jetting signal is sent or – in less extreme cases – lead to satellite drops during jetting, that may spoil the printed structure.

## 2.2.2. Microplotting

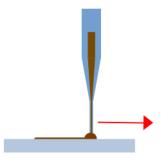

In the microplotting technique, a glass capillary is dipped into an ink reservoir and takes up the ink via capillary forces. Once placed over the substrate, the ink may be released by an ultrasonic signal that is created via a piezo crystal to which the capillary is attached. The frequency of the signal is varying with the setup and chosen as the resonance frequency of the system. In general, droplet diameters with this technique are slightly larger than with ink-jet printing, but of course vary depending on capillary size, ink viscosity and interaction between ink and substrate. Within this work, ink has been applied using the system as a pen writing device. For this the ink-filled capillary is brought into contact with the substrate and the ink is released due to adhesive forces between ink and substrate, possibly supported by an ultrasonic pulse for the initial release. After that, the capillary is slightly raised and moved across the substrate in the desired pattern, and the ink released from the capillary solely based on adhesion to the substrate and surface tension with already deposited ink.

In general, microplotting allows for usage of inks with larger particle sizes, as the capillary opening is wider than the nozzles in ink-jet printing and has less tendency to clog.

Figure 2.13.: Ink application by moving an ink-soaked glass capillary above the substrate; the ink is dragged out of the capillary due to its surface tension

#### 2.2.3. Limitations

While being an effective method for applying material in defined patterns at desired positions, there are also a few limitations in printing that need to be considered.

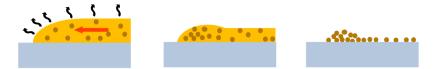

## **Coffee Ring Effect**

Once a droplet is deposited on the substrate, the outer contact line is pinned due to interaction with the surface. As the solvent evaporates more rapidly on the edges due to the curvature of the drop's surface, a material flow towards the edges is created. [57] Effectively, this will lead to more material being deposited on the edges, but the effect is dependent on the contact angle with the substrate and the loading with colloidal particles. [58]

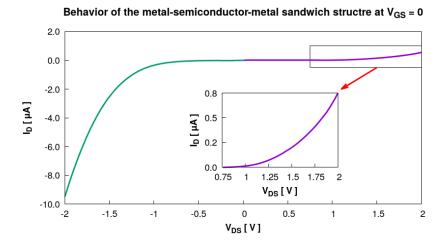

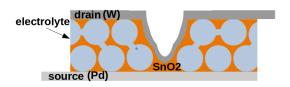

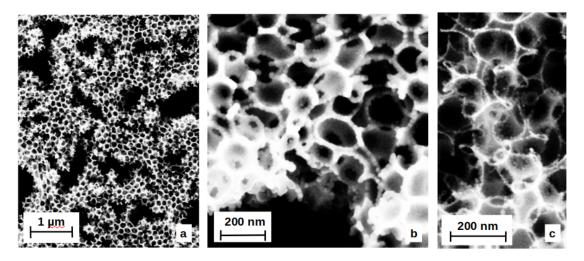

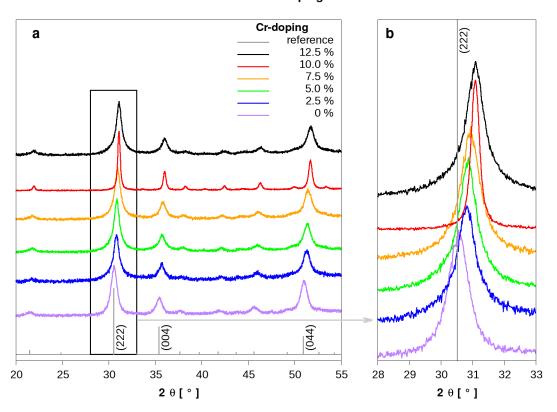

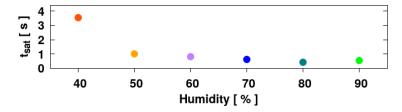

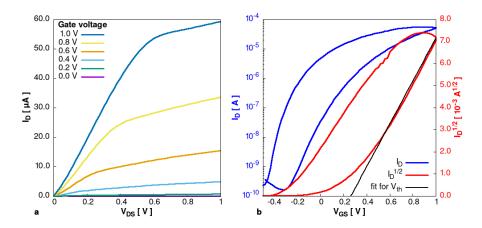

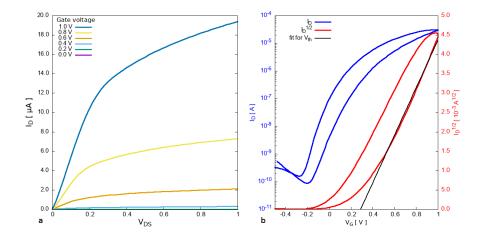

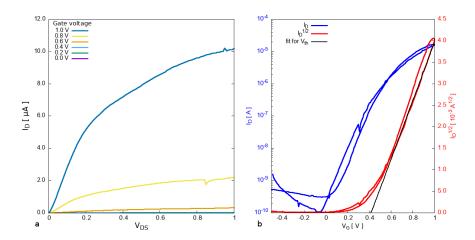

The coffee ring effect may be reduced by changing the ink composition. Adding a high viscosity component will suppress particle movement, a solvent mixture from liquids with differing vapor pressures will influence the evaporation on the edges due to accumulation of the component with the higher boiling point, or changing the pH will lead to variations in the interactions with the surface and between particles. [59, 60] Other approaches include adding nanofibers or changing the shape of the particles themselves. [61,62]