# Efficient and Scalable Universal Circuits\*

Masaud Y. Alhassan · Daniel Günther · Ágnes Kiss · Thomas Schneider

Technical University of Darmstadt, Darmstadt, Germany

sophismay@gmail.com

guenther@encrypto.cs.tu-darmstadt.de

kiss@encrypto.cs.tu-darmstadt.de

schneider@encrypto.cs.tu-darmstadt.de

Communicated by Nigel Smart.

Received 28 March 2019 / Revised 18 February 2020 Online publication 8 April 2020

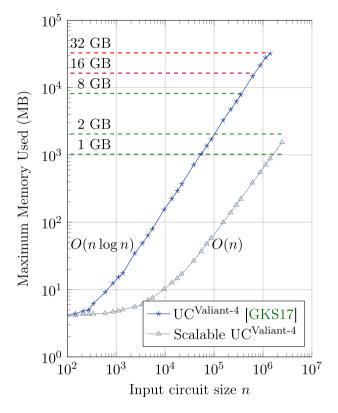

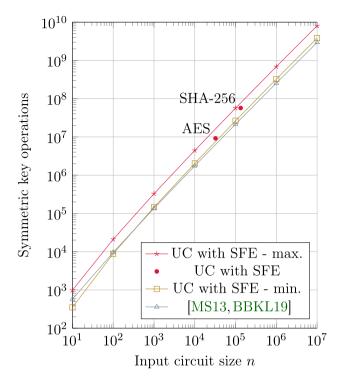

**Abstract.** A universal circuit (UC) can be programmed to simulate any circuit up to a given size n by specifying its program inputs. It provides elegant solutions in various application scenarios, e.g., for private function evaluation (PFE) and for improving the flexibility of attribute-based encryption schemes. The asymptotic lower bound for the size of a UC is  $\Omega(n \log n)$ , and Valiant (STOC'76) provided two theoretical constructions, the so-called 2-way and 4-way UCs (i.e., recursive constructions with 2 and 4 substructures), with asymptotic sizes  $\sim 5n \log_2 n$  and  $\sim 4.75n \log_2 n$ , respectively. In this article, we present and extend our results published in (Kiss and Schneider EUROCRYPT'16) and (Günther et al. ASIACRYPT'17). We validate the practicality of Valiant's UCs by realizing the 2-way and 4-way UCs in our modular open-source implementation. We also provide an example implementation for PFE using these sizeoptimized UCs. We propose a 2/4-hybrid approach that combines the 2-way and the 4-way UCs in order to minimize the size of the resulting UC. We realize that the bottleneck in universal circuit generation and programming becomes the memory consumption of the program since the whole structure of size  $\mathcal{O}(n \log n)$  is handled by the algorithms in memory. In this work, we overcome this by designing novel scalable algorithms for the UC generation and programming. Both algorithms use only  $\mathcal{O}(n)$ memory at any point in time. We prove the practicality of our scalable design with a scalable proof-of-concept implementation for generating Valiant's 4-way UC. We note that this can be extended to work with optimized building blocks analogously. Moreover, we substantially improve the size of our UCs by including and implementing the recent optimization of Zhao et al. (ASIACRYPT'19) that reduces the asymptotic size of the 4-way UC to  $\sim 4.5n \log_2 n$ . Furthermore, we include their optimization in the implementation of our 2/4-hybrid UC which yields the smallest UC construction known so far.

**Keywords.** Universal circuit, Private function evaluation, Function hiding, Scalability.

<sup>\*</sup>This article is a combined and substantially extended version of [45] (EUROCRYPT'16) and [31] (ASIACRYPT'17). We summarize the additional contributions in Sect. 1.3.

#### 1. Introduction

Any computable Boolean function f(x) can be represented as a Boolean circuit  $C_{u,v}^g(x)$  with u input wires  $x = (\text{in}_1, \dots, \text{in}_u)$ , v output wires  $\text{out}_1, \dots, \text{out}_v$ , and g gates for some u, v, g. The size of such a Boolean circuit is n = u + v + g. Universal circuits (UCs) are programmable circuits that can simulate any Boolean function f(x) up to a given size n. To program a UC to compute f, programming or control bits are specified as further inputs  $c^f = \{c_1, \dots, c_m\}$ . The UC then receives these control bits as inputs along with the input x and computes the result as  $UC(x, c^f) = f(x)$ . This means that the same UC can evaluate different Boolean circuits by specifying the respective control bits. In analogy to a universal Turing machine, a universal circuit allows to turn any function into data in the form of a program description.

Several efficient constructions considering both the size and the depth of UCs were proposed. Valiant proposed in [66] an asymptotically size-optimal UC construction with size  $\Theta(n \log n)$  and depth  $\mathcal{O}(n)$  [68]. He presents two constructions, called 2-way and 4-way UCs, based on so-called edge-universal graphs (EUGs) that utilize either 2 or 4 subcircuits, respectively. The asymptotic complexity of the 4-way UC is  $\sim 4.75n \log_2 n$  which is smaller than that of the 2-way UC of  $\sim 5n \log_2 n$  [66]. The 4-way UC has been further improved in [72], where its size is reduced to  $\sim 4.5n \log_2 n$ . An asymptotically depth-optimal construction with depth  $\Theta(d)$  that simulates circuits with depth d was proposed in [17], but it has a significantly larger size of  $\mathcal{O}(n^3d/\log n)$ . In our paper, due to the applications in cryptography that we revisit in Sect. 1.1, we concentrate on the existing size-optimized UCs, especially that proposed by Valiant [66] with asymptotic size  $\Theta(n \log n)$  with the optimization presented by Zhao et al. in [72].

## 1.1. Applications of Universal Circuits

Size-optimized universal circuits have many applications, which we review here and refer to the original publications for a more detailed description.

#### Private Function Evaluation (PFE)

The most prominent application of universal circuits is the secure evaluation of private functions based on secure function evaluation (SFE) or secure computation. SFE enables two parties  $P_1$  and  $P_2$  to evaluate a publicly known function f(x, y) on their respective private inputs x and y, ensuring that none of the participants learns anything about the other participant's input apart from the output of the computation. Many secure computation protocols, such as Yao's garbled circuit protocol [47,69,70] and the GMW protocol [32], use Boolean circuits for representing the desired functionality. In some applications, the function itself should be kept private. This setting is called private function evaluation (PFE), where we assume that only one of the parties  $P_1$  knows the function f(x), whereas the other party  $P_2$  provides the input to the private function x.  $P_2$  should learn no information about f except for an upper bound on the size of the circuit describing the function, and  $P_1$  should learn nothing about x beyond what can be inferred from the result f(x).

PFE can be reduced to SFE [1,44,58,63] by securely evaluating a UC that is programmed by  $P_1$  to evaluate the function f on  $P_2$ 's input x. For this,  $P_1$  provides the control bits  $c^f$  for the UC and  $P_2$  provides his private input x into an SFE protocol that computes  $UC(x, c^f)$ . Here, the UC is a public function and the control bits  $c^f$ —and therefore the function f—and input x are kept private due to the properties of SFE. The first implementation of PFE was provided in [44,61], which extends the Fairplay secure computation framework [51] with universal circuits. The underlying UC construction achieves a non-optimal asymptotic size of  $\mathcal{O}(n\log^2 n)$  and depth  $\mathcal{O}(n\log n)$ . We have shown in [45] that it results in larger UCs than Valiant's constructions for all reasonable circuit sizes in practice. The complexity of PFE in this case is determined mainly by the size and depth of the UC, while the security follows from that of the SFE protocol that is used to evaluate the UC. If the SFE protocol is secure against semi-honest, covert, or malicious adversaries, then the PFE protocol is secure in the same adversarial setting. UC-based PFE can be easily integrated into any SFE framework and can directly benefit from recent optimizations. For instance, outsourcing UC-based PFE to two or multiple servers using XOR secret sharing is directly possible with outsourced SFE [42]. The non-interactive secure computation protocol of [3] can be generalized to obtain a noninteractive PFE protocol [46]. Moreover, with UC-based PFE, evaluating public and private parts of a functionality can easily be performed together without modifying the underlying secure computation framework.

In [40], Katz and Malka presented an alternative approach for PFE that does not rely on UCs. They use additively homomorphic public-key encryption as well as a symmetrickey encryption scheme and achieve constant-round PFE with linear  $\mathcal{O}(n)$  communication complexity. However, the number of public-key operations is linear in the circuit size, and due to the gap between the efficiency of public-key and symmetric-key operations, this results in a less efficient protocol. Their protocol is secure against semi-honest adversaries, uses Yao's garbled circuits [70], and has recently been improved in [5], where the authors modify the algorithm to perform one full execution from which information can be reused in subsequent more efficient executions of the protocol. Mohassel and Sadeghian consider PFE with semi-honest adversaries in [53] and propose a generic PFE framework that can be instantiated with different secure computation protocols. Their first protocol uses homomorphic encryption with which they achieve linear complexity  $\mathcal{O}(n)$  in the circuit size n and their second protocol relies solely on oblivious transfers (OT), which results in a method with  $\mathcal{O}(n \log n)$  symmetric-key operations. The OT-based construction from [53] or PFE using UCs is more desirable than the linear homomorphic encryption-based methods in practice, since using OT extension, the number of expensive public-key operations can significantly be reduced, such that it is independent of the number of OTs [2,36]. Biçer et al. [6] improve the communication of the OT-based PFE protocol of [53] by around 40%. The asymptotic complexity of the OT-based construction of [53] and Valiant's UCs for PFE is the same, and therefore, we compare these solutions for PFE in more detail in Sect. 8. Mohassel et al. extend the framework from [53] to malicious adversaries in [54] with linear complexity  $\mathcal{O}(n)$ , using additively homomorphic encryption. Active security of UC-based PFE is achieved by using a secure computation protocol with active security. Even though their claimed better efficiency, to the best of our knowledge, these protocols have not yet been implemented and are not as generally applicable as PFE with UCs, e.g., they cannot be easily combined with secure evaluation of public functions.

Semi-private function evaluation (semi-PFE) has been proposed in [60] and allows for PFE where the function f is in a set of functions  $\mathcal{F}$  known by both parties. This relaxes the necessary topology hiding requirement of generic PFE. Yao's garbled circuit can be used for evaluating circuits of the same topology as shown in [59]. Recently, an automated approach for semi-PFE has been proposed in [39], where the circuits representing  $f \in \mathcal{F}$  have varying topologies, for which a container topology is found that can be programmed to compute any of the available topologies. This has therefore been defined as a set-universal circuit, i.e., a circuit that can be programmed to compute any circuit from a pre-defined set of circuits. This approach has been further improved in [41], where a modified garbled circuit protocol allows for efficient semi-PFE with linear communication in the size of the largest circuit in  $\mathcal{F}$ . However, semi-PFE does not suffice for generic PFE where we have an exponential number of possible circuit topologies.

#### Applications of PFE

PFE can be applied in scenarios where one of the parties wants to keep the evaluated function private. One of the first applications for PFE was privacy-preserving checking for credit worthiness [21], where not only the loanee's data, but also the loaner's function that computes if the loanee is eligible for a credit needs to be kept private. The original scheme, using garbled circuits, can represent simple policies, but by evaluating a UC their scheme can be extended to more complicated credit checking policies. [15] shows an application for secure computation, where evaluating UCs or other PFE protocols would ensure privacy: When autonomous mobile agents migrate between several distrusting hosts, the privacy of the inputs of the hosts is achieved using SFE, while privacy of the mobile agent's code can be guaranteed with PFE. [57] shows a method to filter remote streaming data obliviously, using secret keywords and their combinations. Their scheme can additionally preserve data privacy by using PFE to search the matching data with a private search function. PFE allows for running proprietary software on private data, such as privacy-preserving evaluation of diagnostic programs that was considered in [13], where the owner of the program does not want to reveal the diagnostic method and the user does not want to reveal his data. Example applications for such programs include medical diagnostics [9] and remote software fault diagnosis, where the function and the user's input are desired to be handled privately. In the protocol presented in [13], the diagnostic programs are represented as binary decision trees or branching programs which can easily be converted into a Boolean circuit representation and evaluated using PFE based on universal circuits. Moreover, PFE can be applied to create blinded policy evaluation protocols [20,24]. [20] utilizes UCs for so-called oblivious circuit policies and [18] for hiding the circuit topology in order to create one-time programs. In [25,59], universal circuits are used for hiding queries in private database management systems (DBMSs). The Blind Seer DBMS [25] was improved in [59] by making use of a simpler UC for evaluating queries, which does not hide the circuit topology. The authors mention that in case the topology of the SQL formula and the circuit have to be kept private, a generic UC should be utilized. Further applications

of PFE given in [53] are evaluation of branching programs on encrypted data [37] and privacy-preserving intrusion detection [56].

## UC Applications Beyond PFE

Apart from being used for PFE, UCs can be applied in various other scenarios. Efficient verifiable computation on encrypted data was studied in [22]. A verifiable computation scheme was proposed for arbitrary computations, and a UC is required to hide the function. [29] make use of UCs for reducing the verifier's preprocessing step. In [30], a DDH-based multi-hop homomorphic encryption scheme is proposed that uses rerandomizable garbled circuits, for which UCs are used to achieve function privacy. When the common reference string is dependent on a function that the verifier is interested in outsourcing, then the function description can be provided as input to a UC of appropriate size. As described in [4], the Attribute-based encryption (ABE) schemes [27,34] for any polynomial-size circuits can be turned into ciphertext-policy ABE by using UCs. The ABE scheme of [28] also uses UCs. Universal circuits can be applied for program obfuscation. Candidates for indistinguishability obfuscation are constructed using a UC as a building block in [14,26]. The algorithm of [26] has been implemented in [12], which can be improved using Valiant's UC implementation [45]. Direct program obfuscation was proposed in [71], where the circuit is a secret key to a UC. [46] mentions that UCs can be applied for secure two-party computation in the batch execution setting, where the cost of evaluating Yao's garbled circuits is amortized if the same circuit—a UC—is evaluated [35,49]. This protocol has been made round-optimal in [52].

## Implied Theoretical Results

We mention two theoretical results relying on UCs. Both the depth-optimized UC from [17] and Valiant's size-optimized UCs were adapted in [8] to construct *universal quantum circuits*. The design of *universal parallel computers* was inspired by Valiant's UCs as well [33,50].

#### 1.2. Our Contributions and Outline

In Sect. 2, we recapitulate the necessary preliminaries for our work. We revisit the asymptotically size-optimal UCs of [66] in Sect. 3. This complex construction makes use of an internal graph representation and programs a so-called edge-universal graph (Sect. 3.1). Thereafter, we describe how an edge-universal graph can be translated into a universal circuit (Sect. 3.2). Finally, we revisit Valiant's 2-way (Sect. 3.3) and 4-way UCs (Sect. 3.4) and the improved building block proposed by Zhao et al. [72] for the latter.

Our modular programming algorithm (Sect. 4). We detail our modular algorithm for programming a universal circuit that provides the description of the input function f as program bits  $c^f$  to the UC, for both Valiant's 2-way and 4-way UCs. Our method consists of two steps, the block edge-embedding (Sect. 4.1) and the recursion point edge-embedding (Sect. 4.2).

New universal circuit constructions and extensions (Sect. 5). We describe Lipmaa et al.'s generalization [46] of Valiant's universal circuit to any k-way UC (Sect. 5.1) and detail how our modular programming algorithm from Sect. 4 can be directly gener-

alized for this extension. We continue with presenting a new 3-way UC (Sect. 5.2) that is predicted to be more efficient than the existing UCs. However, after providing modular building blocks for this UC, we show that it is asymptotically larger than Valiant's UCs, due to an optimization that cannot be applied for one of its building blocks. Then, we propose a hybrid UC construction (Sect. 5.3) that can efficiently combine k-way UCs for multiple values of k. With this, we combine Valiant's 2-way and 4-way UCs to achieve the smallest universal circuit known so far. Lastly, we provide our scalable algorithms (Sect. 5.4) that allow for generating and programming UCs with only linear  $\mathcal{O}(n)$  memory instead of handling the whole structure of size  $\mathcal{O}(n \log n)$  in memory at once.

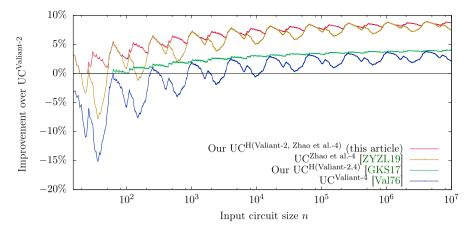

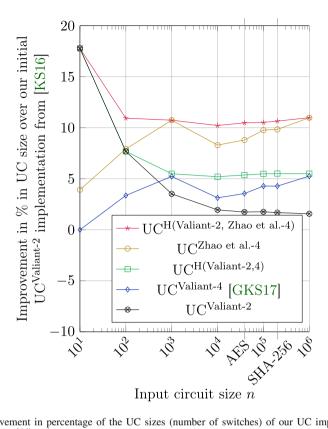

Optimized size and depth of UCs (Sect. 6). We compare the asymptotic (Sect. 6.1) and concrete (Sect. 6.2) sizes of Valiant's (2-way and 4-way) UCs and that of different k-way UCs. We show that of all k-way UCs of Lipmaa et al. [46], Valiant's 4-way UC provides the smallest size for large circuits, whereas Valiant's 2-way UC provides the smallest depth. We include size optimizations, achieving a linear concrete improvement for all UCs. Moreover, we show that our 2/4 hybrid method for generating UCs improves over the 4-way UCs, i.e., both over Valiant's 4-way UC and over the optimized 4-way UC of [72].

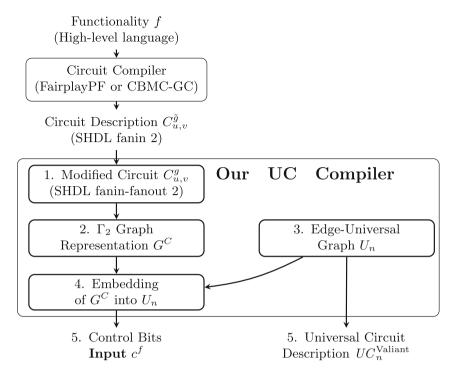

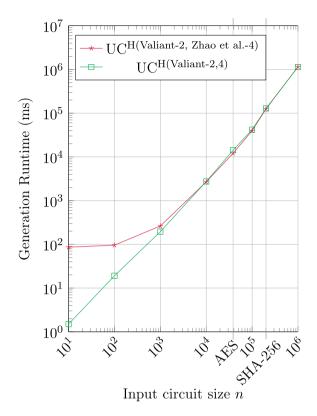

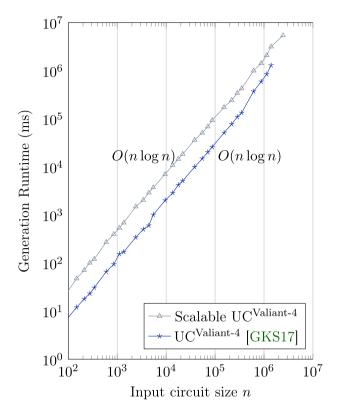

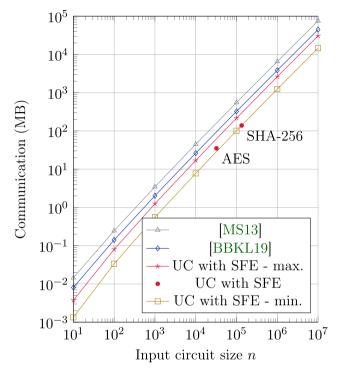

Implementation of Valiant's UCs and experiments (Sect. 7). We detail the steps of our algorithm for a practical realization of Valiant's UC construction and implement the 2-way and recently optimized 4-way UCs as well as our 2/4 hybrid UC construction. We note that our implementation is the first implementation that includes the optimization of Zhao et al. [72], which achieves the best size  $\sim 4.5n \log_2 n$  to date. We describe the architecture of our UC compiler (Sect. 7.1). We experimentally evaluate the performance of our UC generation and programming algorithms with a set of example circuits (Sect. 7.2). We provide the evaluation of our scalable 4-way UC as well and compare it with our memory-based implementation of Valiant's 4-way UC.

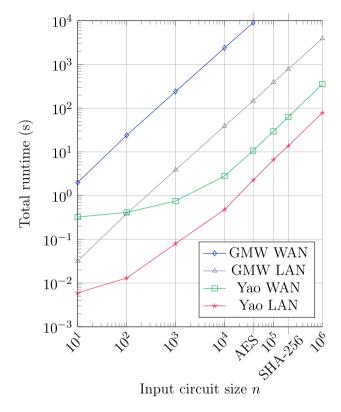

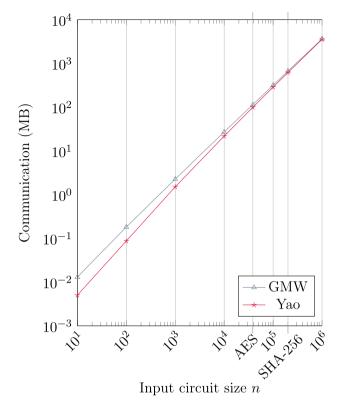

Toolchain for private function evaluation using universal circuits (Sect. 8). We provide the implementation of an example application for universal circuits, namely of private function evaluation (PFE) by extending the ABY secure function evaluation framework [19] to evaluate our universal circuits (Sect. 8.1). We provide the first implementation for PFE with  $\mathcal{O}(n \log n)$  complexity and show experimental results for performing PFE (Sect. 8.2). We theoretically compare PFE with UCs with other state-of-the-art approaches for PFE (Sect. 8.3).

#### 1.3. Additions to Conference Versions

This journal article is a significantly extended and improved version of the conference publications [45] and [31]. Our added contributions are as follows.

Optimizations. We included the optimized building block of [72] in our 4-way and hybrid implementations as well as in the size and depth comparisons. This allows us to compare all state-of-the-art methods for UCs. This is the first implementation of their construction, which has the lowest asymptotic and concrete sizes known so far.

2. Scalability. We extend our design and implementation with a scalable 4-way UC construction based on Valiant's 4-way UC, which reduces the memory complexity from  $\mathcal{O}(n \log n)$  to  $\mathcal{O}(n)$  when generating and programming the universal circuit. This construction involves a novel layer-by-layer approach for generating and topologically ordering the universal circuit and programs the structure according to the recursion steps, i.e., subcircuit by subcircuit.

- 3. Universal circuit depths. We examine the depth of the universal circuits in addition to their sizes, since though being optimized for the latter, some applications also require to minimize the former. For instance, the number of communication rounds in PFE via secure function evaluation with the GMW protocol [32]—which in contrast to Yao's garbled circuits allows to precompute all symmetric cryptographic operations [64]—depends on the depth of the universal circuit.

- 4. Comparison and implementation. In our previous works, we have compared the 2-way and 4-way UCs with each other and with the only other existing UC of [44]. In this work, we implement the hybrid method that uses both 2-way and 4-way UCs and achieves the best concrete size for all simulated circuit sizes. We also implement our new scalable 4-way UC construction, which utilizes very different algorithms than those applied before for UC generation. We compare these methods with respect to runtime, communication, and memory consumption.

#### 2. Preliminaries

As preliminaries for our paper, we introduce the graph and circuit theoretic background in Sect. 2.1 and Sect. 2.2, respectively. We provide a summary of all our notations and abbreviations in "Appendix A."

#### 2.1. Graph Theory

In this section, we describe the graph theoretic preliminaries necessary for our work.

**Definition 1.** The number of incoming [outgoing] edges of a node is called its *indegree* [outdegree]. A graph has fanin [fanout]  $\rho$  if the indegree [outdegree] of all its nodes is at most  $\rho$ .

We denote by  $\Gamma_{\rho}(n)$  the set of all directed acyclic graphs with n nodes and fanin and fanout  $\rho$ .

**Definition 2.** Let G = (V, E) be a directed graph with set of nodes  $V = \{1, ..., n\}$  and edges  $E \subseteq V \times V$ . A mapping  $\eta^G : V \to \{1, ..., n\}$  is called topological order if  $(i, j) \in E$  implies that  $\eta^G(i) < \eta^G(j)$  and  $\forall i, j \in V : \eta^G(i) = \eta^G(j)$  means that i = j. In short, i > j implies that there is no edge or directed path from i to j.

A topological order of  $G \in \Gamma_{\rho}(n)$  can be found with computational complexity  $\mathcal{O}(\rho n)$ . Further on, we require a labeling of the nodes in a topological order. **Definition 3.** Edge-embedding is a mapping from graph G = (V, E) into G' = (V', E') that maps V into V' one-to-one, with possible additional nodes in V', i.e.,  $V \subseteq V'$  and E into directed paths in E', such that all paths are pairwise edge-disjoint, i.e., an edge can be used only in one path.

**Theorem 1.** (Kőnig–Hall theorem) Given a directed acyclic graph (DAG)  $G \in \Gamma_2(n)$ , the set of edges E can be separated into two disjoint sets  $E_1$  and  $E_2$ , such that graphs  $G_1 = (V, E_1)$  and  $G_2 = (V, E_2)$  are instances of  $\Gamma_1(n)$ , having fanin and fanout I for each node [38,48,66].

*Proof of Theorem 1.* Given the set of nodes in topological order  $V = \{1, \ldots, n\}$ , we can construct a bipartite graph  $\overline{G} = (\overline{V}, \overline{E})$  with nodes  $\overline{V} = \{m_1, \ldots, m_n, m'_1, \ldots, m'_n\}$  and edges  $\overline{E}$  such that  $(m_i, m'_j) \in \overline{E}$  if and only if  $(i, j) \in E$ . It is easy to see that the fanin and fanout of the resulting bipartite graph is also 2. The edges of  $\overline{G}$  and thus the corresponding edges of G can be colored in a way that the result is a valid two-coloring. Having fanin and fanout of at most 2, such coloring can be found directly with the following method:

- 1: while there are uncolored edges in  $\overline{G}$  do

- 2: Choose an uncolored edge  $e = (m_i, m'_j)$  randomly and color the path or cycle that contains it in an alternating manner: The neighboring edge(s) of an edge of the first color will be colored with the second color and vice versa.

- 3: end while

This edge-coloring can be performed in  $\mathcal{O}(n)$  steps and it defines the edges in  $E_1$  and  $E_2$ , such that  $E_1$  contains the edges colored with color one and  $E_2$  the ones with color two and  $G_1 = (V, E_1)$  and  $G_2 = (V, E_2)$ .

The Kőnig–Hall theorem was used in [45,46] to provide a 2-coloring algorithm for the edges of a graph with fanin and fanout 2. In its originally proposed form, however, Kőnig's theorem [38,48] applies also for k-coloring the edges of any graph with at most k incoming and outgoing edges for each of its nodes. This transformation can be easily generalized to graphs in  $\Gamma_k(n)$ , in which case the resulting bipartite graph will have fanin and fanout k. We review this theorem and the corresponding algorithm here.

**Theorem 2.** (Kőnig's theorem) If  $\overline{G}$  is bipartite and its nodes have at most k incoming and outgoing edges, then the number of colors sufficient to color all edges of  $\overline{G}$  is k.

**Proof of Theorem 2.** ([38,48]) Take colors  $\{1, \ldots, k\}$ , and greedily color edges. Let us assume that at some point the coloring stops because we cannot color more edges. In this step,  $(w_i, z_j)$  is an uncolored edge. If we look at the colors of the edges adjacent to  $w_i$  and  $z_j$ , we can define the set of available colors for both nodes. There is at least one color for both  $w_i$  and  $z_j$  due to the fanin and fanout restriction, but there is no color which is available for both nodes, otherwise we could color  $(w_i, z_j)$ .

There is a color that is used in an edge adjacent to  $w_i$ , e.g., color a, but not on an edge adjacent to  $z_j$ . In the same way, we can find another color b that is used in an edge

adjacent to  $z_j$ , but not to  $w_i$ . Take the longest unique path P from  $w_i$  that uses colors a and b alternatingly.

Indirectly, assume that this path also contains  $z_j$ . It then terminates in  $z_j$  due to the fact that  $z_j$  is not adjacent with an edge colored with a. Then,  $P \cup (w_i, z_j)$  is an odd cycle, which is impossible since  $\overline{G}$  is bipartite. Therefore, p does not contain  $z_j$ , and we can exchange colors a and b on path P and color  $(w_i, z_j)$  with color a.

This process is continued until there are no uncolored edges in  $\overline{G}$ .

### 2.2. Circuit Theory

**Definition 4.** The *fanin [fanout]* of a circuit can be defined analogously to the fanin [fanout] of a graph (cf. Definition 1), i.e., the maximum number of incoming [outgoing] wires of all its gates, inputs and outputs.

**Theorem 3.** A circuit  $C_{u,v}^{\hat{g}}$  with u inputs,  $\hat{g}$  gates, and v outputs and fanin and fanout  $\rho > 2$  can be transformed to a circuit  $C_{u,v}^{g}$  with fanin and fanout 2.

*Proof of Theorem 3.* Shannon's expansion theorem [61,62] describes how gates with larger fanin can be reduced to gates with two inputs by adding additional gates, which results in a circuit  $C_{u,v}^{\tilde{g}}$  with  $\tilde{g}$  fanin 2 gates. It was proven in [66] that the general case, where the fanout of the circuit can be any integer  $\rho \geq 2$ , can be transformed to the special case when  $\rho \leq 2$  by introducing copy gates, each of which eliminates one from the extra fanout of the original gate. We place a binary tree in place of each gate with fanout larger than 2, following Valiant's proposition: "Any gate with fanout x + 2 can be replaced by a binary fanout tree with x + 1 gates" [66, Corollary 3.1]. Thus, the class of Boolean functions with u inputs and v outputs that can be realized by acyclic circuits with  $\tilde{g}$  gates and arbitrary fanout can also be realized with an acyclic fanout-2 circuit with  $\tilde{g} \leq g \leq 2\tilde{g} + v$  gates.

**Definition 5.** We can regard  $C_{u,v}^g$  with u inputs, v outputs, and g gates as a  $\Gamma_2(n)$  graph G—which we commonly refer to as the *graph of circuit*  $C_{u,v}^g$ —with n = u + v + g by creating a node for each input, gate, and output, and an edge for each wire in  $C_{u,v}^g$ .

### 3. Valiant's Universal Circuit Constructions

In any circuit  $C_{u,v}^{\hat{g}}$ , the inputs of each of the  $\hat{g}$  gates are either connected to one of the u inputs, to the output of a previous gate, or are assigned a fixed constant. Due to the nature of Valiant's edge-universal graph (EUG) construction, the input circuit must have fanin and fanout 2, which can be achieved with the transformations described in Sect. 2.2 and implemented in [44,45]. From here on, and without loss of generality, we assume that our input circuit  $C_{u,v}^{g}$  has u inputs, g gates and v outputs and fanin and fanout 2.

The size of a function f represented by a circuit  $C_{u,v}^g$  with fanin and fanout 2 is n = u + v + g, which can be represented as a graph  $G \in \Gamma_2(n)$ . In this section, we describe Valiant's UC constructions [66,68] that can be programmed to evaluate

any function of size n. We explain the general idea behind Valiant's UC construction [66] in Sects. 3.1 and 3.2, and the 2-way and 4-way UCs along with improvements of [31,45,46,72] in Sects. 3.3 and 3.4, respectively.

## 3.1. Valiant's Edge-Universal Graph Construction

Valiant's UC construction relies on the notion of so-called edge-universal graphs that are then translated to universal circuits [66].

**Definition 6.** A graph  $U_n(\Gamma_\rho) = (V_U, E_U)$  is an *edge-universal graph* (EUG) for  $\Gamma_\rho(n)$  if every graph G = (V, E) in  $\Gamma_\rho(n)$  can be edge-embedded (cf. Definition 3) into  $U_n(\Gamma_\rho)$ .

An EUG  $U_n(\Gamma_\rho)$  has distinguished nodes called *poles*  $P=\{p_1,\ldots,p_n\}\subseteq V_U$  where each node  $a\in V=\{1,\ldots,n\}$  is mapped to exactly one pole with an injective mapping  $\varphi^V:V\to V_U$ . This mapping is defined by a concrete topological order  $\eta^G$  of the original graph G with  $\varphi^V(a)=p_{\eta^G(a)}$ , i.e., every node in G has a corresponding pole in  $U_n(\Gamma_\rho)$ . Apart from the poles,  $U_n(\Gamma_\rho)$  might have additional nodes that enable the edge-embedding (cf. Sect. 2.1). For each edge  $(a_i,a_j)\in E$ , we then define a path of variable length z between the corresponding poles  $\varphi^V(a_i)=p_{\eta^G(a_i)}=b_1$  and  $\varphi^V(a_j)=p_{\eta^G(a_j)}=b_z$  as  $(b_1,\ldots,b_z)$ , where  $b_1,\ldots,b_z\in V_U$ . All these paths are edge-disjoint, i.e., they do not use any edge in  $U_n(\Gamma_\rho)$  in more than one path (cf. Sect. 2.1).

Let  $U_n(\Gamma_1)$  be an EUG for graphs in  $\Gamma_1(n)$  with n poles  $P = \{p_1, \ldots, p_n\}$  (we will show concrete constructions for such EUGs in Sect. 3.3 and in Sect. 3.4). The nodes of any topologically ordered  $\Gamma_1(n)$  graph can be mapped to these poles. The poles have fanin and fanout 1, while all other nodes have fanin and fanout 2.

An EUG  $U_n(\Gamma_\rho)$  for  $\rho \geq 2$  is created by taking  $\rho$  instances of  $U_n(\Gamma_1)$  EUGs with poles  $P_1 = \{p_{1,1}, \ldots, p_{1,n}\}, \ldots, P_\rho = \{p_{\rho,1}, \ldots, p_{\rho,n}\}$ , and merging each pole with its multiple instances, i.e., the set of merged poles  $P = \{p_1, \ldots, p_n\}$  is formed by merging  $p_{1,1}, \ldots, p_{\rho,i}$  to obtain  $p_i$  for  $i = 1, \ldots, n$ . All edges are preserved, and thus, the poles have fanin and fanout  $\rho$ , i.e.,  $U_n(\Gamma_\rho) = (V'_U, E'_U)$  is an EUG with fanin and fanout  $\rho$ , constructed with  $U_n(\Gamma_1)_1 = (V_1, E_1), \ldots, U_n(\Gamma_1)_\rho = (V_\rho, E_\rho)$ . P contains the merged poles and  $V'_U = P \cup_{i=1}^\rho V_i \setminus P_i$  and  $E'_U = \cup_{i=1}^\rho E_i$ . Thus, the poles in  $U_n(\Gamma_\rho)$  have at most  $\rho$  inputs and outputs, and all other nodes have at most two inputs and outputs.

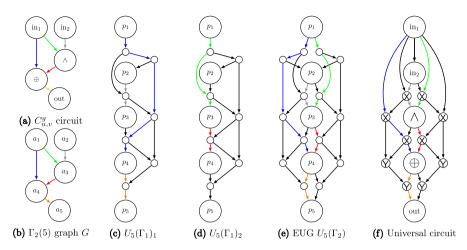

Example. Let C be the circuit shown in Fig. 1a, and G = (V, E) be the graph of circuit C with 5 nodes shown in Fig. 1b. Our aim is to edge-embed G into EUG  $U_5(\Gamma_2)$ . Therefore, we use two instances of  $U_5(\Gamma_1)$ :  $U_5(\Gamma_1)_1$  in Fig. 1c and  $U_5(\Gamma_1)_2$  in Fig. 1d. The edges  $(a_1, a_4)$ ,  $(a_2, a_3)$  and  $(a_4, a_5)$  are embedded in  $U_5(\Gamma_1)_1$ , and the edges  $(a_1, a_3)$  and  $(a_3, a_4)$  in  $U_5(\Gamma_1)_2$ . Merging the poles of  $U_5(\Gamma_1)_1$  and  $U_5(\Gamma_1)_2$  produces  $U_5(\Gamma_2)$  shown in Fig. 1e. In Sect. 3.2, we describe how to retrieve the resulting universal circuit depicted in Fig. 1f.

Recursion Base. Valiant's construction is recursive, and the recursion base graphs for up to 6 nodes are shown in [66, Fig. 3] and [45, Fig. 1].  $U_1(\Gamma_1)$  is a single pole and  $U_2(\Gamma_1)$  and  $U_3(\Gamma_1)$  are two- and three-connected poles, respectively. Valiant provides hand-optimized EUGs for  $U_4(\Gamma_1)$ ,  $U_5(\Gamma_1)$  and  $U_6(\Gamma_1)$ , with 3, 7, and 9 additional nodes, respectively (cf. [66, Fig. 3]).

Fig. 1. a An example circuit and **b** the corresponding  $\Gamma_2(5)$  graph G. **c**, **d** The edge-embedding of G into two  $U_5(\Gamma_1)$  instances with poles  $(p_1, \ldots, p_5)$ . **e** The edge-embedding of G into the  $U_5(\Gamma_2)$  graph of the universal circuit shown in (**f**).

#### 3.2. Translating Edge-Universal Graphs into Universal Circuits

In this section, we define universal circuits (UCs) and describe how an edge-universal graph is translated into a universal circuit.

**Definition 7.** A *universal circuit UC* is a Boolean circuit that can be programmed to compute any circuit  $C_{u,v}^g$  up to a given size n by defining a set of programming bits  $c^f$  such that  $UC(x, c^f) = C_{u,v}^g(x)$ .

In Valiant's UC constructions, every node  $w \in V_U$  fulfills a task when  $U_n(\Gamma_2)$  is translated to a UC. Programming the UC means specifying its control bits along the paths defined by the edge-embedding and by the gates of circuit  $C_{u,v}^g$ . Depending on the number of incoming and outgoing edges and its type, a node w is translated as described below and shown in the example in Fig. 1f.

- **G1** If w is a pole and corresponds to an input (one of the first u poles) or an output (one of the last v poles) in G, then w is an *input or output* in  $C_{u,v}^g$  as well.

- **G2** If w is not a pole and has indegree 1 and outdegree 2, this node has been placed to copy its input to its two outputs. Therefore, when translated to a UC, w is replaced by multiple outgoing wires in the parent node (as described in [45]), since the UC does not need to fulfill the fanout 2 restriction. In  $U_n(\Gamma_2)$ , w is added due to the fanout 2 restriction in the EUG necessary for the edge-embedding.

- **G3** If w is not a pole and has indegree and outdegree 1, w is removed and replaced by a wire between its parent and child nodes.

- **G4** If w is a pole and corresponds to a gate (poles  $\{u+1, \ldots, u+g\}$ ) in G, w is programmed as a *universal gate* (UG). A 2-input UG supports any of the 16 possible gate types represented by 4 control bits of the gate table  $(c_1, c_2, c_3, c_4)$ .

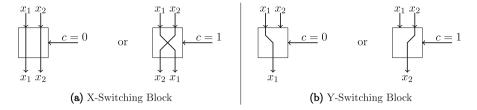

Fig. 2. Programmable switching blocks [43].

It implements function  $U: \{0, 1\}^2 \times \{0, 1\}^4 \rightarrow \{0, 1\}$  that computes

$$U(x_1, x_2, c_1, c_2, c_3, c_4) = \overline{x_1} \, \overline{x_2} c_1 + \overline{x_1} x_2 c_2 + x_1 \overline{x_2} c_3 + x_1 x_2 c_4. \tag{1}$$

- **G5** If w is not a pole and has indegree and outdegree 2, w is programmed as an X-switching block, which computes  $X: \{0, 1\}^2 \times \{0, 1\} \rightarrow \{0, 1\}^2$  with  $X((x_1, x_2), c) = (x_{1+c}, x_{2-c})$  as shown in Fig. 2a. The inputs of an X-switching block are forwarded to its outputs, switched or not switched, depending on control bit c.

- **G6** If w is not a pole and has indegree 2 and outdegree 1, w is programmed as a Y-switching block that computes  $Y: \{0, 1\}^2 \times \{0, 1\} \rightarrow \{0, 1\}$  with  $Y((x_1, x_2), c) = x_{1+c}$  as visualized in Fig. 2b. The inputs of a Y-switching block are forwarded to its output depending on the control bit c, i.e., it provides the functionality of a 2-input multiplexer.

We note that the u inputs and the v outputs can be ordered arbitrarily within themselves as long as the inputs are kept before the g topologically ordered gates and the outputs after them. Even though the output nodes cause an overhead in Valiant's UC, they are required to fully hide the topology of the circuit in the corresponding universal circuit. Note that optionally it is possible to modify the input circuit such that the outputs of the last v gates in order are the outputs of the circuit by inserting at most v copy gates [40].

The nodes programmed as UG (G4), X-switching block (G5), or Y-switching block (G6) are so-called *programmable blocks*. This means that a control bit c or vector  $\overline{c} = (c_1, c_2, c_3, c_4)$  is necessary aside from the two inputs to define their behavior. The universal gates are programmed according to the simulated gates in  $C_{u,v}^g$  and the universal switches according to the paths defined by the edge-embedding of the graph of the circuit G into the edge-universal graph  $U_n(\Gamma_2)$ . Depending on whether the path takes the same direction during the embedding (e.g., arrives from the left and continues on the left) or changes its direction at a given node (e.g., arrives from the left and continues on the right), the control bit of the universal switch is programmed accordingly. In Sect. 7.1, we describe efficient implementations of programmable blocks. All control bits and vectors together are the programming  $c^f$  of the UC.

## 3.3. Valiant's 2-way UC Construction

We described in Sect. 3.1 that a  $U_n(\Gamma_\rho)$  EUG can be constructed of  $\rho$  instances of  $U_n(\Gamma_1)$  EUGs. Valiant [66] provides an EUG for  $\Gamma_1(n)$  graphs, two of which can

**Fig. 3.** Body block  $B^{(2)}$  of Valiant's 2-way EUG  $U_n^{(2)}(\Gamma_1)$  [66].

build an EUG for  $\Gamma_2(n)$  graphs, which suffices for circuits with 2-input gates that have at most two outgoing wires. Let  $P = \{p_1, \ldots, p_n\}$  be the set of poles in  $U_n(\Gamma_1)$  that have indegree and outdegree 1, corresponding to the inputs, gates and outputs of the input circuit  $C_{u,v}^g$ , i.e., poles  $P_{\text{in}} = \{p_1, \ldots, p_u\}$  correspond to the inputs,  $P_{\text{gate}} = \{p_{(u+1)}, \ldots, p_{(u+g)}\}$  to the gates,  $P_{\text{out}} = \{p_{(u+g+1)}, \ldots, p_n\}$  to the outputs. The main, so-called body block  $B^{(2)}$  used for constructing Valiant's EUG for  $\Gamma_1(n)$  graphs  $U_n^{(2)}(\Gamma_1)$  of size  $\sim 2.5n \log_2 n$  is shown in Fig. 3 and consists of 2 poles (large circles), 4 so-called recursion points (rectangles), and 3 additional nodes (small circles). The corresponding UC has twice the size  $\sim 5n \log_2 n$ , since it corresponds to an EUG for  $\Gamma_2(n)$  graphs. This construction is called the 2-way EUG or UC construction since there are two sets of recursion nodes at each recursion step as we describe below.

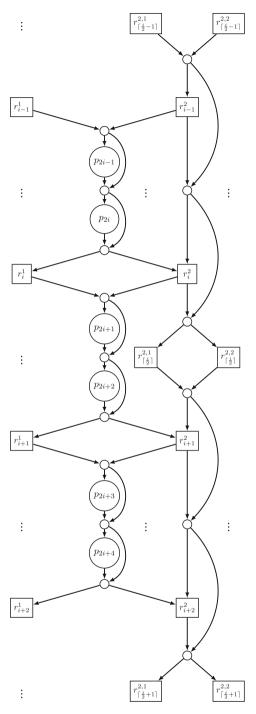

The recursive construction works as follows: The rectangles are special nodes that build up the set of poles in the next recursion step, i.e.,  $R_{\lceil \frac{n}{2}-1 \rceil}^1 = \{r_1^1, \dots, r_{\lceil \frac{n}{2}-1 \rceil}^1\}$  and  $R_{\lceil \frac{n}{2}-1 \rceil}^2 = \{r_1^2, \dots, r_{\lceil \frac{n}{2}-1 \rceil}^2\}$  are the poles of two smaller edge-universal graphs called subgraphs. EUGs are built with these poles which produce new subgraphs with size  $\lceil \frac{r_2^n-1}{2} \rceil - 1 \rceil$ , such that we have four subgraphs at the next level, etc. The blocks are chained together at the recursion points to form a skeleton, i.e., each recursion point belongs to two in the corresponding subgraph. Thus, the main skeleton of the UC consists of  $\lceil \frac{n}{2} \rceil$  such blocks with poles  $\{p_1, p_2, \dots, p_n\}$ , and the next two skeletons consist of  $\lceil \frac{r_2-1}{2} \rceil$  blocks with sets of poles  $\{r_1^1, \dots, r_{\lceil \frac{n}{2}-1 \rceil}^1\}$  and  $\{r_1^2, \dots, r_{\lceil \frac{n}{2}-1 \rceil}^2\}$ . We visualize the process of chaining the blocks together to form this skeleton in Fig. 4.

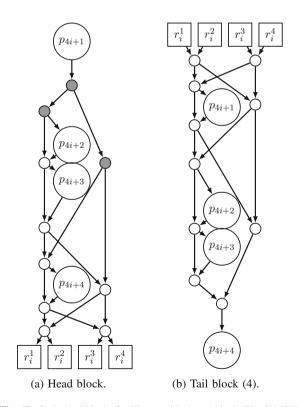

We note that the top (resp. bottom) block of a skeleton does not need the upper (resp. lower) recursion points since its poles are the inputs (resp. outputs) in the block. Therefore, we presented optimized so-called head  $H^{(2)}$  and tail  $T^{(2)}$  blocks that occur in the top and bottom of a skeleton, respectively, in [31, Fig. 2b–e].

**Fig. 4.** Skeleton built of a chain of body blocks  $B^{(2)}$  of Valiant's 2-way EUG  $U_n^{(2)}(\Gamma_1)$ .

**Theorem 4.** ([66]) The resulting 2-way EUG is edge-universal, and therefore, the resulting circuit is universal.

Proof of Theorem 4 [Val76]. We recapitulate the proof from [66] that  $U_n^{(2)}(\Gamma_1)$  is edge-universal for  $\Gamma_1(n)$ , such that any graph with n nodes and fanin and fanout 1 can be edge-embedded into  $U_n^{(2)}(\Gamma_1)$ . According to the definition of edge-embedding, it has to be shown that given any  $\Gamma_1(n)$  graph G = (V, E), for any  $(i, j) \in E$  and  $(k, l) \in E$  we can find pairwise edge-disjoint paths from  $p_i$  to  $p_j$  and from  $p_k$  to  $p_l$  in  $U_n^{(2)}(\Gamma_1)$ . As before, the labeling of nodes  $V = \{1, \ldots, n\}$  in G is according to a topological order of the nodes.

Firstly, each two neighboring poles of the EUG,  $p_{2s}$  and  $p_{2s+1}$  for  $s \in \{1, \dots, \lceil \frac{n}{2} \rceil\}$ , are thought of as merged poles, so-called superpoles, with their fanin and fanout becoming 2. In a similar manner, any  $G \in \Gamma_1(n)$  graph can be regarded as a  $\Gamma_2(\lceil \frac{n}{2} \rceil)$  graph with supernodes, i.e., each pair (2s, 2s + 1) will be merged into one node in  $\bar{a} \Gamma_2(\lceil \frac{n}{2} \rceil)$ graph G' = (V', E'). If there are edges between the nodes in G, they are simulated with loops. The set of edges of this graph G is partitioned to disjoint sets  $E_1$  and  $E_2$ , such that  $G_1 = (V, E_1)$  and  $G_2 = (V, E_2)$  are instances of  $\Gamma_1(\lceil \frac{n}{2} \rceil)$  and  $\Gamma_1(\lfloor \frac{n}{2} \rfloor)$ , respectively. This can be done efficiently, as shown in Theorem 1. The edges in  $\tilde{E}_1$  are embedded as directed paths in  $R_{\lceil \frac{n}{2}-1 \rceil}^1$ , and the edges in  $E_2$  as directed paths in  $R_{\lceil \frac{n}{2}-1 \rceil}^2$ . Both  $E_1$ and  $E_2$  have at most one edge directed into and at most one directed out of any supernode, and therefore, there is only one edge from  $E_1$  and one from  $E_2$  to be simulated going through any superpole in  $U_n^{(2)}(\Gamma_1)$  as well. Thus, the edge coming into a superpole  $(p_{2s}, p_{2s+1})$  in  $E_1$  is embedded as a path through  $r_{s-1}^1$ , while the edge going out of the pole in  $E_1$  is embedded as a path through  $r_s^1$  in the appropriate subgraph. Similarly, the edges in  $E_2$  are simulated as edges through  $r_{s-1}^2$  and  $r_s^2$ . These paths can be chosen disjoint according to the induction hypothesis. Finally, the paths from  $r_{s-1}^1$  and  $r_{s-1}^2$  to superpole  $(p_{2s-1}, p_{2s})$  as well as the paths from  $(p_{2s-1}, p_{2s})$  to  $r_s^1$  and  $r_s^2$  can be chosen edge-disjoint due to the skeleton built up of the body blocks shown in Fig. 3. With this, Valiant's graph construction results in a valid EUG with asymptotically optimal size  $\mathcal{O}(n \log n)$  and depth  $\mathcal{O}(n)$  [66]. With the building blocks described in Sect. 3.2, it is easy to see that the resulting Boolean circuit is universal.

Implementation. We provided an open-source implementation of this 2-way UC optimized for PFE in [45]. In concurrent and independent related work, Lipmaa et al. [46] also showed the practicality of Valiant's 2-way UC. They decrease its total number of gates compared to that of Valiant's block (Fig. 3) by one XOR gate. However, the number of AND gates is exactly the same, and therefore, their improvement does not affect PFE using UCs, where XOR gates are evaluated for free [44].

#### 3.4. Valiant's 4-way UC Construction

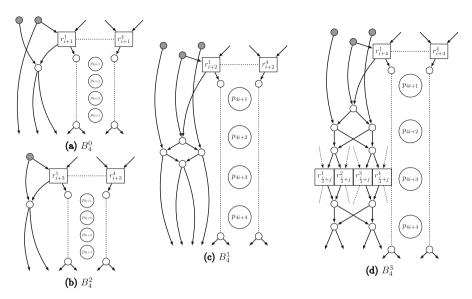

Similarly to the 2-way EUG construction (cf. Sect. 3.3), Valiant provides a more efficient 4-way EUG or UC construction [66] for  $\Gamma_1(n)$  graphs which can be extended to an EUG for  $\Gamma_2(n)$  graphs by utilizing two instances  $U_n^{(4)}(\Gamma_1)_1$  and  $U_n^{(4)}(\Gamma_1)_2$  as described in Sect. 3.1.  $U_n^{(4)}(\Gamma_1)$  has a 4-way recursive structure, i.e., at each recur-

(a) Body block of (b) Body block of Valiant [Val76]. Zhao et al. [ZYZL19].

**Fig. 5.** Body block  $B^{(4)}$  alternatives for 4-way EUG  $U_n^{(4)}(\Gamma_1)$ .

sion step, nodes in special sets  $R_{\lceil \frac{n}{4}-1 \rceil}^1 = \{r_1^1, \dots r_{\lceil \frac{n}{4}-1 \rceil}^1\}$ ,  $R_{\lceil \frac{n}{4}-1 \rceil}^2 = \{r_1^2, \dots r_{\lceil \frac{n}{4}-1 \rceil}^2\}$ ,  $R_{\lceil \frac{n}{4}-1 \rceil}^3 = \{r_1^2, \dots r_{\lceil \frac{n}{4}-1 \rceil}^3\}$  and  $R_{\lceil \frac{n}{4}-1 \rceil}^4 = \{r_1^4, \dots r_{\lceil \frac{n}{4}-1 \rceil}^4\}^1$  are the poles in the next recursion step (the main body block is shown in Fig. 5a). The recursion base is the same as for the 2-way UC construction described in Sect. 3.1. This construction results in UCs of smaller size  $\sim 4.75n \log_2 n$  but has a more complicated structure and programming algorithm. We have studied and implemented this universal circuit in [31] and recapitulate our results here and in Sect. 7. Valiant offers the main, so-called body block  $B^{(4)}$  consisting of 4 poles (large circles), 15 nodes (small circles) as well as 8 recursion points (rectangles) shown in Fig. 5a. As before, we provide so-called head  $H^{(4)}$  and tail  $T^{(4)}$  blocks that occur at the top and bottom of a skeleton in [31, Figs. 4b-4i], respectively. The blocks are connected such that the 4 top (resp. bottom) recursion points of one block are the 4 bottom (resp. top) recursion points of the next block. Similarly to the 2-way EUG, 4 sets are created for n nodes, i.e.,  $R_{\lceil \frac{n}{4}-1 \rceil}^1$ ,  $R_{\lceil \frac{n}{4}-1 \rceil}^2$ , and  $R_{\lceil \frac{n}{4}-1 \rceil}^4$  which are the poles of 4  $U_{\lceil \frac{n}{2} \rceil -1}(\Gamma_1)$  EUGs in the next recursion step. Then, these also create 4 subgraphs until the recursion base is reached (cf. Sect. 3.1).

$<sup>1</sup>_n \pmod{4}$  of these have size  $\lfloor \frac{n}{4} - 1 \rfloor$ , but for the sake of simplicity, we do not distinguish these here.

Recently, Zhao et al. in [72] optimized the body block of Valiant's UC by finding a more efficient block using exhaustive search over all possible blocks. As opposed to Valiant's UC that uses 15 additional nodes in the body block, their block uses only 14 additional nodes, and therefore, their UC achieves an asymptotically better size of  $\sim 4.5 n \log_2 n$ . We depict the further optimized body block  $B^{(4)}$  of Zhao et al. in Fig. 5b. Zhao et al. provide a computer generated proof of that this block can indeed be used to construct universal circuits. Moreover, they show that there exists no block with only 13 additional nodes that can be used to construct UCs in the same manner. This proves that the minimal size of a 4-way UC is the achieved  $\sim 4.5 n \log_2 n$ .

**Theorem 5.** ([66]) The resulting 4-way EUG is edge-universal, and therefore, the resulting circuit is universal.

The proof of this theorem is analogous to that of Theorem 4.

## 4. Programming Valiant's Universal Circuits

We designed the detailed embedding algorithm and the open-source UC implementation of [45] specifically for the 2-way UC, dealing with the whole UC skeleton as one block. In contrast, based on the modular design of [46], we modularized the edge-embedding task into multiple subtasks and described how they can be performed separately in [31]. In this section, we detail this modular approach for edge-embedding a graph into Valiant's  $\ell$ -way EUG, where  $\ell=2$  or  $\ell=4$ : The edge-embedding can be split into two parts, which are then combined.

In the following, we describe the two main steps of our modular approach presented in [31] that are based on the edge-embedding algorithm of [45]. 1) Block edge-embedding (Sect. 4.1) allows for the programming of the blocks visualized in Fig. 3 on p. 12 and in Figs. 5a or b on p. 14.2) Recursion point edge-embedding (Sect. 4.2) takes care of the programming of the whole UC. Here, the paths are defined and the necessary information is provided to the blocks (cf. Sect. 4.2). The process can be generalized to any  $2^i$ -way EUG. Moreover, the same modular edge-embedding algorithm can be applied with a few modifications for Lipmaa et al.'s generalization to any k-way UC [46], which we describe later in Sect. 5.1.

#### 4.1. Block Edge-Embedding

We consider the  $\ell$  top (resp. bottom) recursion points of a block (Figs. 3 and 5a or b) as intermediate nodes where the inputs (resp. outputs) of the block enter (resp. exit). The blocks are built so that any of these inputs can be forwarded to exactly one of the  $\ell$  poles of the block and the output of any pole can be forwarded to an output or another pole with a higher topological order.

We formalize this behavior as follows: In  $U_n^{(\ell)}(\Gamma_1)=(V_U,E_U)$ , let  $B^{(\ell)}$  be the (i-1)th block in the skeleton made up of blocks visualized in Fig. 3 for  $\ell=2$  and Fig. 5a or b for  $\ell=4$  with poles  $p_{\ell i+1},\ldots,p_{\ell i+\ell}$ . Let the mapping  $\eta^U:V_U\to\mathbb{N}^+$  denote a topological order of all nodes and poles in  $V_U$ . Then, the nodes  $r_1^1,\ldots,r_\ell^\ell$  and

$r_{i+1}^1,\dots,r_{i+1}^\ell$  denote the input and output recursion points of block  $B^{(\ell)}$ . Additionally, let  $in=(in_1,\dots,in_\ell)\in\{0,\dots,\ell\}^\ell$  and  $out=(out_1,\dots,out_\ell)\in\{0,\dots,2\ell-1\}^\ell$  denote the input and output vectors of  $B^{(\ell)}$ . The value 0 of the input and output vectors is a *dummy value* which is used if there is no specific path between an input and a pole, or between a pole and an output of  $B^{(\ell)}$ . The output vector has a larger value range, since a pole can be forwarded to another pole or an output recursion point. Therefore, we use values  $1,\dots,\ell-1$  for poles  $p_{\ell i+2},\dots,p_{\ell i+\ell}$  and values  $\ell,\dots,2\ell-1$  for the output recursion points. Pole  $p_{\ell i+1}$  cannot be a destination for a path in  $B^{(\ell)}$ , since  $\eta^U(p_{\ell i+1})$  is less than the topological order of any other pole in  $B^{(\ell)}$ . Additionally, the values of in and out need to be pairwise different or 0. Every combination of input and output vector covering the conditions formalized below in Eqs. 2–6 is valid for  $B^{(\ell)}$ . A pair  $(r_i^l, p_j) \in \mathcal{P}$  or  $(p_j, r_{i+1}^l) \in \mathcal{P}$  is a path from  $r_i^l$  to  $p_j$  or  $p_j$  to  $r_i^l$  in the set of all paths  $\mathcal{P}$  in  $B^{(\ell)}$ . Then,  $\mathcal{P}_B^{(\ell)} \subseteq \mathcal{P}$  denote the paths that are to be edge-embedded (cf. Sect. 3.1).

InPolePath:

$$\forall l \in \{1, \dots, \ell\} : in_l \neq 0 \rightarrow (r_i^l, p_{\ell i + in_l}) \in \mathcal{P}_R^{(\ell)},$$

(2)

PolePolePath:

$$out_l \neq 0 \land out_l < \ell \rightarrow (p_j, p_{\ell i+1+out_l}) \in \mathcal{P}_B^{(\ell)} \land \eta^U(p_j) < \eta^U(p_{\ell i+1+out_l}), \tag{3}$$

POLEOUTPATH:

$$out_{l} > \ell - 1 \rightarrow (p_{\ell i + l}, r_{i + 1}^{out_{l} - \ell - 1}) \in \mathcal{P}_{B}^{(\ell)}. \tag{4}$$

INDIFF:

$$\forall i n_i, i n_j \in i n : i \neq j \rightarrow i n_i = 0 \lor i n_i \neq i n_j.$$

(5)

OUTDIFF:

$$\forall out_i, out_j \in out : i \neq j \rightarrow out_i = 0 \lor out_i \neq out_j$$

. (6)

### 4.2. Recursion Point Edge-Embedding

Block edge-embedding covers only the programming of the nodes within the blocks of the UC. Another task is to program the recursion points. We use the construction of [45] which, in every step, splits a  $\Gamma_2(n)$  graph in two  $\Gamma_1(n)$  graphs, which are merged to two  $\Gamma_2(\lceil \frac{n}{2} - 1 \rceil)$  graphs. This, as described later, results in a tree of graphs with fanin and fanout one or two called *supergraph* [45]. We use this supergraph for defining the paths in Valiant's 2-way EUG. For Valiant's 4-way EUG, we use every second step of the algorithm with a minor modification. We describe our modular algorithm for the 2-way and 4-way UCs below and in Listing 1.

Let  $C_{u,v}^k$  be the Boolean circuit computing function f that our UC needs to compute and  $G \in \Gamma_2(n)$  its graph representation (cf. Sect. 2.2).

1. Splitting G∈ Γ<sub>2</sub>(n) in two Γ<sub>1</sub>(n) graphs G<sub>1</sub> and G<sub>2</sub>: As described in Sect. 3.1, Valiant's UC is derived from an EUG for Γ<sub>2</sub>(n) graphs, which is built up of two EUGs (U<sub>n</sub><sup>(ℓ)</sup>(Γ<sub>1</sub>))<sub>1</sub> and (U<sub>n</sub><sup>(ℓ)</sup>(Γ<sub>1</sub>))<sub>2</sub> for Γ<sub>1</sub>(n) graphs merged by their poles. G is similarly split into two Γ<sub>1</sub>(n) graphs G<sub>1</sub> and G<sub>2</sub>, which then need to be edgeembedded into (U<sub>n</sub><sup>(ℓ)</sup>(Γ<sub>1</sub>))<sub>1</sub> and (U<sub>n</sub><sup>(ℓ)</sup>(Γ<sub>1</sub>))<sub>2</sub>, respectively. G = (V, E) ∈ Γ<sub>2</sub>(n) is split by 2-coloring its edges [45,66], which can always be done due to Kőnig's theorem [38,48] recapitulated in Theorems 1 and 2 on p. 7–8. After 2-coloring,

E is divided into sets  $E_1$  and  $E_2$ , using which we build  $G_1 = (V, E_1)$  and  $G_2 = (V, E_2)$ , with the following conditions:

$$\mathsf{EDGEIn}E_1\mathsf{or}E_2: \ \forall e \in E: (e \in E_1 \lor e \in E_2) \land \neg (e \in E_1 \land e \in E_2). \tag{7}$$

Fanini

$$E_1: \forall e = (v_1, v_2) \in E_1: \neg \exists e' = (v_3, v_4) \in E_1: v_2 = v_4 \lor v_1 = v_3.$$

(8)

Fanini

$$E_2: \forall e = (v_1, v_2) \in E_2: \neg \exists e' = (v_3, v_4) \in E_2: v_2 = v_4 \lor v_1 = v_3.$$

(9)

- 2. Merging a  $\Gamma_1(n)$  graph into a  $\Gamma_2(\lceil \frac{n}{2}-1 \rceil)$  graph. In an EUG, the number of poles decreases in each recursion step and merging a  $\Gamma_1(n)$  graph into a  $\Gamma_2(\lceil \frac{n}{2}-1 \rceil)$  graph provides information about the paths to be taken. Let  $G_1 = (V, E) \in \Gamma_1(n)$  be a topologically ordered graph and  $G_m = (V', E') \in \Gamma_2(\lceil \frac{n}{2}-1 \rceil)$  be a graph with nodes  $V' = \{v'_1, \ldots, v'_{\lceil \frac{n}{2} \rceil}\}$ . We define two labelings  $\eta_{in}$  and  $\eta_{out}$  on  $G_m$  with  $\eta_{in}(v_i) = i$  and  $\eta_{out}(v_i) = \eta_{in}(v_i) 1 = i 1$ . Additionally, we define a mapping  $\theta_V$  that maps a node  $v_i \in V$  to a node  $v_j \in V'$  with  $\theta_V(v_i) = v'_{\lceil \frac{i}{2} \rceil}$ , i.e., two nodes in  $G_1$  are mapped to one node in  $G_m$ . At last, we define a mapping  $\theta_E$  that maps an edge  $e_i = (v_i, v_j) \in E$  to an edge  $e_j \in E'$  with  $\theta_E((v_i, v_j)) = (v_{\eta_{in}}(\theta_V(v_i)), v_{\eta_{out}}(\theta_V(v_j)))$ , i.e., every edge in  $G_1$  is mapped to an edge in  $G_m$  as follows:  $e_j = (v_i, v_j) \in E$  is mapped to  $e_j' = (v_j', v_j') \in E'$ , such that  $v_k' = \theta_V(v_i)$ , and the new node of  $v_j$  in  $G_m$  is  $v_{l+1}'$  (not  $v_l'$ ).  $G_m$  is built as follows:  $V' = \{v_1', \ldots, v_{\lceil \frac{n}{2} \rceil}\}$  and  $E' = \bigcup_{e \in E} \theta_E(e)$ . Then for all  $e_j = (v_i', v_j') \in E'$  and  $e_j' \in E'$  and  $e_j' \in E'$  are removed from  $e_j' \in E'$  along with the last node  $e_j' \in E'$  and to the definition of  $e_j' \in E'$  it does not have any incoming edges). The resulting  $e_j' \in E'$  are topologically ordered graph in  $e_j' \in E'$  and  $e_j' \in E'$  are the properties of  $e_j' \in E'$  and  $e_j' \in E'$  and  $e_j' \in E'$  and  $e_j' \in E'$  and  $e_j' \in E'$  are the properties of  $e_j' \in E'$  and the resulting  $e_j' \in E'$  and the properties of  $e_j' \in E'$  and the properties of  $e_j' \in E'$  and  $e_j' \in E'$  are the properties of  $e_j' \in E'$  and  $e_j' \in E'$  are the properties of  $e_j' \in E'$  and  $e_j' \in E'$  are the properties of  $e_j' \in E'$  and  $e_j' \in E'$  are the properties of  $e_j' \in E'$  and  $e_j' \in E'$  are the properties of  $e_j' \in E'$  and  $e_j' \in E'$  and  $e_j' \in E'$  are the properties of  $e_j' \in E'$  and e

- 3. The supergraph for Valiant's EUG construction. In the first step, G is split into two  $\Gamma_1(n)$  graphs  $G_1$  and  $G_2$ .  $G_1$  and  $G_2$  contain all the edges that should be embedded as paths between poles in the first and second EUGs for  $\Gamma_1(n)$ , respectively. We now explain how to edge-embed the  $\Gamma_1(n)$  graph  $G_1$  into an EUG  $U_n^{(\ell)}(\Gamma_1)$  (for  $G_2$  it is analogous).

For edge-embedding in the 2-way EUG,  $G_1$  is first merged to a  $\Gamma_2(\lceil \frac{n}{2}-1\rceil)$  graph  $G_m$ .  $G_m$  is then 2-colored and split into two  $\Gamma_1(\lceil \frac{n}{2}-1\rceil)$  graphs  $G_1^1$  and  $G_1^2$  [45]. These get merged to two graphs  $G_m^1$  and  $G_m^2$ , which are then 2-colored and split into two  $\Gamma_1(\lceil \frac{\lceil \frac{n}{2}-1\rceil}{2}-1\rceil)$  graphs. These steps are repeated until the recursion base is reached. In the supergraph,  $G_1^{\psi \circ 1}$  and  $G_1^{\psi \circ 2}$  are the first and second subgraphs of  $G_1^{\psi}$  for any  $\psi$ , respectively.

In Valiant's 4-way EUG construction [66], a supergraph that creates 4 subgraphs in each step is necessary. We require a merging method where a  $\Gamma_1(n)$  graph is merged to a  $\Gamma_4(\lceil \frac{n}{4} - 1 \rceil)$  graph where 4 nodes build a new node, and 4-color this graph to retrieve 4 subgraphs. However, this can directly be solved by using the method described above from [45]: After repeating the 2-coloring and the merging twice, we gain 4 subgraphs  $(G_1^{11}, G_1^{12}, G_1^{21} \text{ and } G_1^{22})$ . These can be used as if they were the result of 4-coloring the graph obtained by merging every 4 nodes into one.

However, there is a modification in this case: The first 2-coloring is a preprocessing step, which does not map to an EUG recursion step. Therefore, we have to define another

**Listing 1.** Edge-embedding algorithm for Valiant's  $\ell$ -way EUG.

```

procedure edge-embedding (\mathcal{U}, G_1 = (V, E))

2

Let S be the set of the \ell \Gamma_1 subgraphs of G_1 in the supergraph

3

Let \mathcal{R} be the \ell recursion step graphs

4

Let \mathcal{B} be the set of blocks in \mathcal{U}

5

for all e = (v_i, v_j) \in E do

6

Let i' and j' denote the positions of v_i and v_j in their blocks

7

b_i \leftarrow \lceil \frac{i}{\ell} \rceil, b_j \leftarrow \lceil \frac{j}{\ell} \rceil // number of block in which v_i and v_j are

8

Let out [r_1] denote the output vector [recursion points] of \mathcal{B}[b_i]

9

Let in [r_0] denote the the input vector [recursion points] of \mathcal{B}[b_j]

10

if b_i = b_j do // v_i and v_j are in the same block

11

if v_i \neq v_i do

out_{i'} \leftarrow j' - 1

12

13

end if

14

else // vi and vi are in different blocks

Let s = (V', E') \in \mathcal{S} denote the \Gamma_1 graph with e' = (p_{b_i}, p_{b_{i-1}}) \in E' and e' is not marked

15

16

17

Let x denote the number with s = S[x]

Set the control bit of r_0^x to 1

18

19

if b_i = b_i + 1 do // b_i and b_i are neighbours

20

21

else

22

y ← 1

23

end if

24

Set the control bit of r_1^x to y

25

out_{i'} \leftarrow x + \ell, in_x \leftarrow j'

26

end if

27

end for

28

Edge-embed all blocks in B // edge-embed all sub-blocks

29

for i = 1 to \ell do

30

if S[i] exists do

{f call} edge-embedding(\mathcal{R}[i], \ \mathcal{S}[i])

31

32

end if

33

end for

end procedure

```

labeling  $\eta_{\text{out}_P}(v) = \eta_{\text{in}}(v)$ , since in this preprocessing step we need to keep node  $v_{\lceil \frac{n}{2} \rceil}$ . Then the creation of the supergraph for the 4-way EUG construction works as follows: We merge  $G_1$  to a  $\Gamma_2(\lceil \frac{n}{2} \rceil)$  graph with labeling  $\eta_{\text{in}}$  and  $\eta_{\text{out}_P}$  and get  $G_m$ . After that, we split  $G_m$  into two  $\Gamma_1(\lceil \frac{n}{2} \rceil)$  graphs  $G_1^1$  and  $G_1^2$ . These get merged to  $\Gamma_2(\lceil \frac{n}{4} \rceil - 1)$  graphs  $G_m^1$  and  $G_m^2$  using the  $\eta_{\text{in}}$  and  $\eta_{\text{out}}$  labelings. Finally, these two graphs get split into  $4\Gamma_1(\lceil \frac{n}{4} - 1 \rceil)$  graphs  $G_1^{11}$ ,  $G_1^{12}$ ,  $G_1^{21}$ , and  $G_1^{22}$ . These are the relevant graphs for the first recursion step in Valiant's 4-way EUG construction. Then we continue for all 4 subgraphs until we reach the recursion base.

$\ell$ -way Edge-Embedding Algorithm. In Listing 1, we combine block edge-embedding and recursion point edge-embedding.

Let  $\mathcal{U}$  denote the part of  $U_n^{(\ell)}(\Gamma_1)$  without recursion steps (the main skeleton) and  $G_1=(V,E)$  be the  $\Gamma_1(n)$  graph which is to be edge-embedded in  $U_n^{(\ell)}(\Gamma_1)$ .  $\mathcal{S}$  denotes the set of  $\ell$  subgraphs of  $G_1$  in the supergraph, i.e.,  $\mathcal{S}=\{G_1^1,G_1^2\}$  for  $\ell=2$  and  $\mathcal{S}=\{G_1^{11},G_1^{12},G_1^{21},G_1^{22}\}$  for  $\ell=4$ . A *recursion step graph* of  $\mathcal{U}$  is one of the graphs having one of the  $\ell$  sets of recursion points as poles (e.g.,  $r_1^1,\ldots,r_{\lceil \ell-1 \rceil}^1$ ) without the recursion steps.  $\mathcal{R}$  denotes the set of all  $\ell$  recursion step graphs of  $\mathcal{U}$ , and  $\mathcal{B}$  denotes the set of all blocks in  $\mathcal{U}$ .

We give a brief explanation of Listing 1 that describes the edge-embedding process. For any edge  $e = (v_i, v_j) \in E$  in  $G_1$ ,  $b_i$  and  $b_j$  denote the block numbers in which  $v_i$  and  $v_j$  are. We distinguish between two cases:

Case 1.  $v_i$  and  $v_j$  are in the same block:  $b_i = b_j$ . The edge-embedding is solved within the block, and no recursion points have to be programmed for the path. Therefore, vector out of block  $\mathcal{B}[b_i]$  is set accordingly.

Case 2.  $v_i$  and  $v_j$  are in different blocks:  $b_i \neq b_j$ . There exists an edge  $e' = (b_i, b_{j-1})$  in one of the  $\ell$   $\Gamma_1(\lceil \frac{n}{\ell} - 1 \rceil)$  subgraphs of  $G_1$  that is not yet used for an edge-embedding. This determines that the path in the next recursion step has to be between poles  $p_{b_i}$  and  $p_{b_{j-1}}$ . We denote with  $s \in \mathcal{S}$  the subgraph of  $G_1$  which contains e' and x denotes its number in S, i.e., S[x] = s. This implies in which of the  $\ell$  recursion step graphs we need to edge-embed the path from  $p_{b_i}$  to  $p_{b_{j-1}}$ , and so which recursion points we need to program. We first set the control bit of the xth input (resp. output) recursion points to 1 since the path between the poles with labeling i and j enters (resp. exits) the next recursion step over this recursion point. A special case to be considered here is when blocks  $\mathcal{B}[b_i]$  are neighbors (i.e.,  $b_j = b_i + 1$ ). Then, the path enters and leaves the next recursion step graph at the same node, whose control bit thus has to be 0. The output vector of block  $\mathcal{B}[b_i]$  is the i'th value to the i'th pole in this block.

We repeat these steps for all edges  $e \in E$ . Since all input and output vector of all blocks in  $\mathcal{B}$  are set, they can be embedded with the block edge-embedding. For all  $\ell$  subgraphs of  $G_1$  in the supergraph and in the EUG, we call the same procedure with  $\mathcal{S}[i] \in \mathcal{S}$ ,  $\mathcal{R}[i] \in \mathcal{R}$ ,  $1 \le i \le \ell$ .

## 5. Extensions to Valiant's UC Constructions

Here, we describe ideas for novel UC constructions and implementations. Firstly, in Sect. 5.1, we describe the k-way generalization of Valiant's UC presented by Lipmaa et al. in [46]. In Sect. 5.2, we describe our modular building blocks for a potentially more efficient 3-way UC. We show that Valiant's optimized  $U_3(\Gamma_1)$  cannot directly be applied as a building block in the construction due to the fact that it must have an additional node to be part of a generic EUG. We prove that the EUG without this node is not a valid EUG by showing a counterexample. Therefore, it actually results in a worse asymptotic size than Valiant's 2-way and 4-way UCs [66]. Thereafter, in Sect. 5.3, we propose a  $hybrid\ UC$ , utilizing both Valiant's 2-way and 4-way UCs or Valiant's 2-way and Zhao et al.'s 4-way UC [72] so that the overall size of the resulting hybrid UC is minimized and is at least as efficient as the better construction for the given size (in Sect. 6.2 we show its concrete improvement). Finally, in Sect. 5.4, we propose a different modular and scalable approach of Valiant's 4-way UC. This approach requires a lot of modifications in the UC generation and programming algorithm, but can be generalized to any k-way UC or to our hybrid UC.

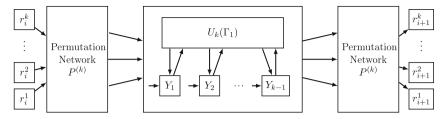

**Fig. 6.** k-way EUG construction  $U_n^{(k)}(\Gamma_1)$  [46].

#### 5.1. Generalized k-way UC

In [46], Lipmaa et al. generalize Valiant's approach by providing a UC with any number of recursion points k, the so-called k-way EUG or UC. We note that their construction slightly differs from Valiant's EUG, since they do not consider the restriction on the fanout of the poles, i.e., the nodes in the EUG that correspond to universal gates or inputs (cf. Sect. 3.1). This optimization has also been included in [45] when translating an EUG to a UC, but including it in the block design leads to better sizes for the number of XOR gates. This, however, does not make a difference in case of our most prominent application of private function evaluation (PFE) (cf. Sect. 1.1), where XOR gates are free, i.e., do not require cryptographic operations and communication.

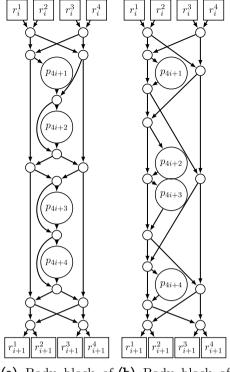

The idea is to split n=u+v+g in  $m=\lceil \frac{n}{k} \rceil$  blocks as shown in Fig. 6. Every block i consists of k inputs  $r_i^1, r_i^2, \ldots, r_i^k$  and k outputs  $r_{i+1}^1, r_{i+1}^2, \ldots, r_{i+1}^k$  as well as k poles, except for the last block which has a number of poles depending on n mod k. For every  $j \leq k$ , the list of all  $r_i^j$  builds the poles of the jth subgraph of the next recursion step, i.e., we have k subgraphs. Additionally, every block begins and ends with a Waksman permutation network [67] such that the inputs and outputs can be permuted to any pole. A Y-switching block is placed in front of every pole  $p_i$  which is connected to the ith output of the permutation network as well as the ith output of a block-intern EUG  $U_k(\Gamma_1)$ . This means that Lipmaa et al. in [46] reduce the problem of finding an efficient k-way EUG  $U_n^{(k)}(\Gamma_2)$  block  $B^{(k)}$  to the problem of finding the smallest EUG  $U_k(\Gamma_1)$ . Their solution is to build the block-intern EUG with the UC of [44], which was claimed to be more efficient for smaller circuits than [66]. Moreover, they calculate the optimal k value to be around 3.147 with their construction, which implies that the best solutions are found using small EUGs, for which Valiant provides hand-optimized solutions (i.e., for k=2,3,4,5,6) [66].

We note that the results recently presented by Zhao et al. [72] do not fit into this generalized *k*-way construction. Therefore, Zhao et al.'s optimized 4-way block is an optimization over Valiant's modular 4-way block construction [66].

#### Programming the Generalized UC

In this section, we extend the recent work of [46] by providing a detailed and modular embedding mechanism for any k-way EUG construction. We provide the main differences to the edge-embedding of the 2-way and 4-way EUG detailed in Sect. 4.

k-way  $Block\ Edge$ -Embedding. In this setting, our main block is a programmable block  $B^{(k)}$  with k poles  $p_1,\ldots,p_k$ , and k input [output] recursion points  $r_0^1,\ldots,r_0^k\ [r_1^1,\ldots,r_1^k]$ .  $B^{(k)}$  is topologically ordered with mapping  $\eta^U$  as defined in Sect. 2.1. Vectors  $in=(in_1,\ldots,in_k)\in\{0,\ldots,k\}^k$  and  $out=(out_1,\ldots,out_k)\in\{0,\ldots,2k-1\}^k$  denote the input and output vectors of  $B^{(k)}$ , respectively. Values  $k,\ldots,2k-1$  in out denote the recursion point targets  $r_1^1,\ldots,r_1^k$  (cf. Sect. 4.1). The setting of in and out is formalized in Eqs. 2–6 when  $\ell=k$ .

*k-way Recursion Point Edge-Embedding.*  $G \in \Gamma_2(n)$  denotes the transformed graph of a Boolean circuit  $C_{u,v}^g$ , where n = u + v + g.

- 1. Splitting  $G \in \Gamma_2(n)$  into two  $\Gamma_1(n)$  graphs  $G_1$  and  $G_2$ : Similarly as in Sect. 4.2, we first split G into two  $\Gamma_1(n)$  graphs  $G_1$  and  $G_2$  with 2-coloring.

- 2. Merging a  $\Gamma_1(n)$  graph into a  $\Gamma_k(\lceil \frac{n}{k} 1 \rceil)$  graph  $G_1 = (V, E) \in \Gamma_1(n)$  is merged into a  $\Gamma_k(\lceil \frac{n}{k} 1 \rceil)$  graph  $G_m = (V', E')$  (same for  $G_2$ ). Therefore, we redefine mapping  $\theta_V$  (cf. Sect. 4.2) that maps node  $v_i \in V$  to node  $v_j \in V'$ . In this scenario, k nodes in V build one node in V', so  $\theta_V(v_i) = v_{\lceil \frac{i}{k} \rceil}$ . The mapping of the edges  $\theta_E$  is the same as in the 2-way and 4-way EUG construction, and  $(v_i', v_j') \in E'$  where j < i edges are removed along with  $v_{\lceil \frac{n}{k} \rceil}$  in the end.  $G_m$  is then a topologically ordered graph in  $\Gamma_1(\lceil \frac{n}{k} 1 \rceil)$ .

- 3. The supergraph for Lipmaa et al.'s k-way EUG construction The next step of the construction is to split  $G_m \in \Gamma_1(\lceil \frac{n}{k} 1 \rceil)$  into  $k \Gamma_1(\lceil \frac{n}{k} 1 \rceil)$  graphs. This is done with k-coloring: A directed graph K = (V, E) can be k-colored, if k sets  $E_1, \ldots, E_k \subseteq E$  cover the following conditions:

Disjoint

$$\forall i, j \in \{1, \dots, k\}: i \neq j \rightarrow E_i \cap E_j = \emptyset.$$

(10)

EDGEIN

$$E_i \quad \forall e \in E : \quad \exists i \in \{1, \dots, k\} : e \in E_i.$$

(11)

Fanini

$$E_i \quad \forall i \in \{1, \dots, k\}, \forall e = (v_1, v_2) \in E_i$$

:

$$\neg \exists e' = (v_3, v_4) \in E_i \setminus \{e\} : v_2 = v_4 \lor v_1 = v_3. \tag{12}$$

According to Kőnig's theorem [38,48] described in Sect. 2.1,  $\Gamma_k(n)$  graphs can always be k-colored efficiently with a dedicated algorithm. The rest of the supergraph construction and the way it is used for edge-embedding is the same as for the 2-way and 4-way EUG as described in Sect. 4.2.

*k-way Edge-Embedding Algorithm*. The edge-embedding algorithm is the same as shown in Listing 1, with  $\ell = k$ .

### 5.2. Potentially More Efficient 3-Way UC

The optimal k value for minimizing the size of the k-way UC was calculated to be 3.147 in [46]. We describe our idea of a 3-way UC. Intuitively, based on an optimization by Valiant [66], this UC should result in the best asymptotic size. The asymptotic size of any k-way UC depends on the size of its modular body block  $B^{(k)}$  (e.g., Fig. 5a or b on

p. 14 for the 4-way UC). Once it is determined, the size of the UC is  $\operatorname{size}(U_n^{(k)}(\Gamma_2)) = 2 \cdot \operatorname{size}(U_n^{(k)}(\Gamma_1)) \sim 2 \cdot \frac{\operatorname{size}(B^{(k)})}{k} n \log_k n = 2 \cdot \frac{\operatorname{size}(B^{(k)})}{k \log_2(k)} n \log_2 n$ . The modular block consists of two permutation networks  $P^{(k)}$ , an EUG  $U_k(\Gamma_1)$ , and (k-1) Y-switching blocks (cf. Sect. 5.1, [46]).<sup>2</sup>

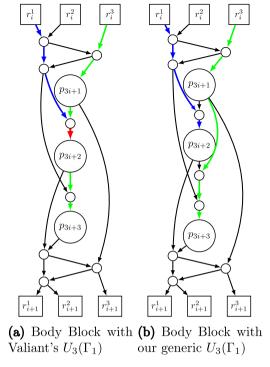

Size of Body Block  $B^{(3)}$  with Valiant's Optimized  $U_3(\Gamma_1)$ . According to Valiant [66], an EUG  $U_3(\Gamma_1)$  with 3 poles contains only three-connected poles (used as recursion base in Sect. 3.1). An optimal permutation network  $P^{(3)}$  that achieves the lower bound has 3 nodes as well. This implies that  $\operatorname{size}(B^{(k)}) = 2 \cdot P^{(3)} + \operatorname{size}(U_3(\Gamma_1)) + (3-1) = 11$ . Then, the size of the UC becomes  $\sim 2 \cdot \frac{11}{3 \log_2 3} n \log_2 n \sim 4.627 n \log_2 n$ , which means an asymptotically by around 2.5% smaller size than that of Valiant's 4-way UC with  $\sim 4.75 n \log_2 n$ .

However, there is a flaw in this initial design. Valiant's  $U_3(\Gamma_1)$  only works as an EUG for 3 nodes under special conditions, e.g., when it is a subgraph within a larger EUG. There are 3 possible edges in a topologically ordered graph G = (V, E) in  $\Gamma_1(3)$ : (1, 2), (2, 3) and (1, 3), (1, 2) and (2, 3) can be directly embedded in  $U_3(\Gamma_1)$  using  $(p_1, p_2)$  and  $(p_2, p_3)$ , respectively. (1, 3), however, has to be embedded as a path *through* node 2, i.e., as a path  $((p_1, p_2), (p_2, p_3))$ . When  $U_3(\Gamma_1)$  is a subgraph of a bigger EUG, this is possible by programming  $p_2$  accordingly. However, when we use this  $U_3(\Gamma_1)$  as a building block in the body block of our EUG, it cannot directly be applied, due to the fact that the programming of  $p_2$  depends on other constraints as well. A generic  $U_3(\Gamma_1)$  that can embed (1, 3) without going through  $p_2$  as before has an additional Y-switching block between  $p_2$  and  $p_3$ .

We depict in Fig. 7a the 3-way body block that uses Valiant's optimized  $U_3(\Gamma_1)$  in the k-way block design of [46] and show that it is not a valid body block for an EUG construction. Assume that the output of pole  $p_{3i+1}$  has to be directed to pole  $p_{3i+3}$  (green path). Then, it needs to go through pole  $p_{3i+2}$ , which means that the red edge going to  $p_{3i+2}$  is used by this path. However, there can be an other edge coming from the permutation network as an input to  $p_{3i+2}$ , e.g., from  $p_{3i}$  from the preceding block through  $r_i^1$  (blue path). This cannot be directed to  $p_{3i+2}$  anymore, as shown in Fig. 7a, since the red edge would carry two different values. Therefore, in the 3-way body block construction, it does not suffice to use Valiant's optimized  $U_3(\Gamma_1)$  [66].

Size of Body Block  $B^{(3)}$  with Our Generic  $U_3(\Gamma_1)$ . In Fig. 7b, we show the 3-way body block with the generic  $U_3(\Gamma_1)$  that allows the output from  $p_{3i+1}$  to be directed to  $p_{3i+3}$  without having to go *through*  $p_{3i+2}$  (green path), and the edge going into  $p_{3i+2}$  can be utilized by the path directed into this node (blue path). This results in  $\operatorname{size}(B^{(3)}) = 2 \cdot P^{(3)} + \operatorname{size}(U_3(\Gamma_1)) + (3-1) = 12$ , which implies that the size of the UC is  $2 \cdot \frac{12}{3 \log_2 3} n \log_2 n = 5.047 n \log_2 n$ . Unfortunately, this is even worse than the size of the 2-way UC with  $2 \cdot n \log_2 n$ , and we therefore conclude that the most efficient known UC is Valiant's 4-way UC with Zhao et al.'s optimization.

Recently, Zhao et al. [72] have shown by exhaustive search over all possible topologies that the 3-way body block  $B^{(3)}$  presented in Fig. 7b results in the smallest 3-way UC by

<sup>&</sup>lt;sup>2</sup>We note that in this section, we design the body block according to [46], i.e., the poles do not have a fanout restriction. However, all other nodes have fanout-2 restriction.

**Fig. 7.** Body block  $B^{(3)}$  construction for our 3-way EUG  $U_n^{(3)}(\Gamma_1)$ .

showing that no block with only 11 additional nodes can be used as a universal block, and indeed, our block with 12 additional nodes can be utilized.

## 5.3. 2/4 Hybrid UC Construction

In this section, we detail our hybrid UC based on Valiant's 2-way and 4-way UCs with the optimization by Zhao et al. [72], which yields the smallest UCs to date. Given the size of the input circuit  $C_{u,v}^g$ , i.e., n=u+v+g, we can calculate at each recursion step if it is better to create 2 subgraphs of size  $\lceil \frac{n}{2} - 1 \rceil$  and utilize the 2-way recursive skeleton, or it is more beneficial to create a 4-way recursive skeleton with 4 subgraphs of size  $\lceil \frac{n}{4} - 1 \rceil$ .

We assume that for every n, we have an algorithm that computes the size (i.e.,  $\operatorname{size}(U_n^{\operatorname{hybrid}(K)}(\Gamma_1))$ ) of the hybrid UC for sizes smaller than n. We give details on how it is computed in Sect. 6. Then, Listing 2 describes the algorithm for constructing a hybrid UC, at each step based on which strategy is more efficient. We note that our hybrid construction is generic, and given multiple k-way UCs as parameter K ( $K = \{2, 4\}$  in our example), it minimizes the concrete size of the resulting UC.

**Listing 2.** Hybrid construction algorithm, where  $B^{(k)}(i)$ ,  $H^{(k)}(i)$  and  $T^{(k)}(i)$  denote body, head and tail blocks with i poles in the k-way UC, respectively.

```

procedure hybrid (p_1, \ldots, p_n, K = \{2, 4\})

1

Let \operatorname{size}(U_{n'}^{\text{hybrid}(K)}(\Gamma_1)) be the function calculating the size of the smaller hybrid constructions with

2

\hookrightarrow size n' \le n

3

for all k \in K do // Number of poles in the last block for all k

4

if n \mid k do

5

m_k \leftarrow k

6

7

m_k \leftarrow n \mod k

8

end if

\begin{split} s_k \leftarrow & \operatorname{size}(H^{(k)}(k)) + \left( \lceil \frac{n}{k} \rceil - 3 \right) \cdot \operatorname{size}(B^{(k)}(k)) + \operatorname{size}(B^{(k)}(r_k)) + \operatorname{size}(T^{(k)}(m_k)) + \\ & \Longrightarrow m_2 \cdot \operatorname{size}\left( \operatorname{size}(U_{\lceil \frac{n}{k} - 1 \rceil}^{\operatorname{hybrid}(K)}(\Gamma_1)) \right) + ((k - m_k) \cdot \operatorname{size}\left( \operatorname{size}(U_{\lfloor \frac{n}{k} - 1 \rfloor}^{\operatorname{hybrid}(K)}(\Gamma_1)) \right) \end{split}

9

10

11